# Research Article

# VLSI Implementation of Green Computing Control Unit on Zynq FPGA for Green Communication

Anurag Shrivastava<sup>(b)</sup>,<sup>1</sup> Ali Rizwan<sup>(b)</sup>,<sup>2</sup> Neelam Sanjeev Kumar<sup>(b)</sup>,<sup>3</sup> R. Saravanakumar<sup>(b)</sup>,<sup>4</sup> Inderjit Singh Dhanoa<sup>(b)</sup>,<sup>5</sup> Pankaj Bhambri<sup>(b)</sup>,<sup>6</sup> and Bhupesh Kumar Singh<sup>(b)</sup><sup>7</sup>

<sup>1</sup>ECE, Lakshmi Narain College of Technology and Science Indore, India

<sup>2</sup>Department of Industrial Engineering, Faculty of Engineering, King Abdulaziz University, Jeddah 21589, Saudi Arabia

<sup>3</sup>Department of BME, Saveetha School of Engineering, Saveetha Institute of Medical and Technical Sciences, Thandalam, Chennai, India

<sup>4</sup>Department of Wireless Communication Institute of ECE, Saveetha School of Engineering, Saveetha Institute of Medical and Technical Sciences, Chennai, India

<sup>5</sup>Department of Computer Science and Engineering, Guru Nanak Dev Engineering College, Ludhiana, Punjab, India <sup>6</sup>Department of Information Technology, Guru Nanak Dev Engineering College, Ludhiana, Punjab, India <sup>7</sup>Arba Minch Institute of Technology, Arba Minch University, Ethiopia

Correspondence should be addressed to Bhupesh Kumar Singh; dr.bhupeshkumarsingh@amu.edu.et

Received 21 September 2021; Revised 3 November 2021; Accepted 6 November 2021; Published 30 November 2021

Academic Editor: Samarendra Nath Sur

Copyright © 2021 Anurag Shrivastava et al. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

The issue of the energy shortage is affecting the entire planet. This is occurring because of massive population and industry growth around the world. As a result, the entire world is attempting to implement green networking systems and manufacture the power/energy efficient products. This research work discusses the green networking system technologies. This work introduces a power-efficient control unit (CU) design and implemented on the Zynq SoC (System on Chip) ultrascale field programmable gate array (FPGA). The VIVADO HLx Design Suite is used to simulate and analyze the CU model which is considered as one of the key components of central processing unit (CPU), used for data communication purposes. The CU is made suitable for the green communication by making it power-efficient. Therefore, the power consumption of the CU is analyzed for the various set frequency value ranging between 100 MHz and 5 GHz, and it is discovered that as the clock frequency rises up, the total power consumption also tends to get increased. The total power of the proposed model is reduced by 77.42%, 21.29%, and 17.93% from three models, respectively, being compared in the present paper. Final results shows that the CU is better suited to run at low frequencies to optimize power consumption.

# 1. Introduction

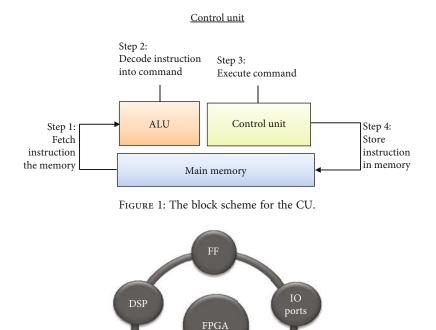

There have been many issues with the scarcity of natural resources in the Earth because of the rapid population expansion and industrialization in the world [1]. Thus, people are worried about the future generation saving of those resources. This can be done using green technology of connectivity and energy-efficient machines [2]. The work represents a step in the direction of promoting green networking technology and energy-efficient devices. A control unit

(CU), to minimize the power consumption, is installed on field programmable gate array (FPGA) in this work. A control unit is a part of a circuitry that regulates activity in the computer [3]. It gives instructions on how to react to instructions that the program sends to these devices in the logic unit, memory, input, and output devices [4]. Figure 1 shows the block scheme for the control unit. It selects and retrieves instructions from the main memory in the proper sequence and interprets them to allow other functional elements to perform the respective operations at the

FIGURE 2: Building components of the FPGA device.

BUFG

MB

appropriate time [5–7]. Each input data is passed via the main memory to a processing device, comprising the four basic arithmetic functions (i.e., adding, subtracting, multiplying, and dividing) as well as certain logical operations such as data comparison and the selection of the required problem-solving method or a suitable alternative, on the basis of default decision criteria [8, 9].

Of all these features and vast application in the field of computing, CU is regarded as one of the suitable components which can be used for green computing as well as green communication; also, these green computing and green communication makes the environment sustainable. By reducing its power consumption, the CU can be made suitable for green applications. Therefore, the power-efficient CU will be the great choice for communication technologies [10, 11]. The power consumption of CU is optimized by its realization on FPGA devices. FPGAs are those devices which are made-up with semiconductor materials. It is called field programmable because it can be reconfigured/reprogrammed after its manufacturing [12-14]. FPGA devices are made-up with many components, and theses components are regarded as building components such as clock buffers (BUFGs), flipflops (FF), input/output (IO) ports, memory blocks (MB), and digital signal processors (DSPs) [15, 16]. The building components of the FPGA device are represented in Figure 2.

1.1. Green Computing Communication. Green computing (GC) is a future generation environmentally friendly way of utilizing the computers, mobile device, and their resources.

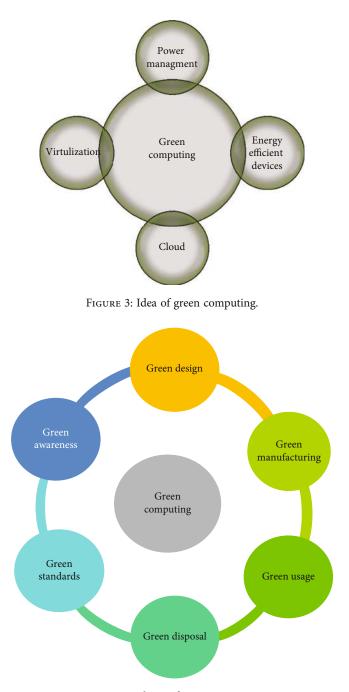

GC is also regarded as green information technology (green IT). In a broad way, GC term can also be coined as the method of designing, manufacturing, implementing, using, and disposing the mobile and computing peripherals and devices with least damage on environment resources. A brief idea of green computing is described in Figures 3 and 4.

Figure 3 shows the things which are associated with green computing. These are such power management of devices, designing of energy-efficient devices, processors, and other computer devices, cloud, and virtualization. In cloud and virtualization, we try to communicate the data with cloud server and access the data from cloud.

Figure 4 represents the utilities of GC. Generally, there 4 major points concerned with GC.

- (i) Green use—it implies minimising power consumption of computer and mobile devices

- (ii) Green disposal—it implies reusing and recycling of unwanted electronic devices

- (iii) Green design—it covers the implementation and designing power and energy efficient devices

- (iv) Green manufacturing—green manufacturing discusses about manufacturing computer and mobile devices with minimized waste

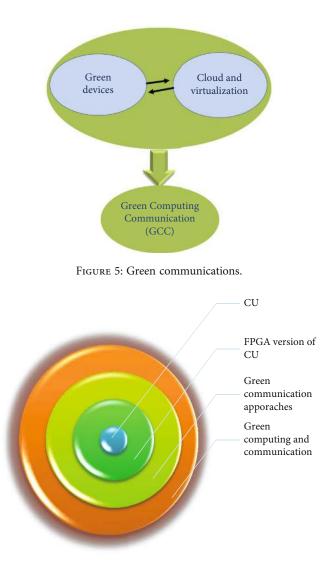

The communication of green devices with cloud and virtualization are known to be as green computing communication (GCC). The overview of GCC is shown in Figure 5.

FIGURE 4: Utilities of green computing.

# 2. Related Work

With the help of IO standard, researchers have developed a power-efficient CU on Artix-7 FPGA with the support of various Low Voltage CMOS (LVCMOS) technologies. Input and output impedance are used to minimize the electricity consumption. Authors on Artix-7 FPGA design a powerefficient CU by modifying its frequency values. The shift in frequency values would change the CU's power consumption by FPGA [17]. Researchers are using I/O standards of Stub Series Terminated Logic (SSTL) to increase CU power consumption on 40 nm of Virtex-6 FPGA. The standards of the SSTL I/O correspond to the input load impedance w.r.t with the output load to minimize power consumption [18]. An electronic CU has been developed for the control of the vehicle system by FPGA authors. The RISC processor (ARM) is used in combination with FPGA to perform parallel computing tasks [19]. A power-efficient CU on Virtex and the Spartan family FPGA was introduced to support the concepts of Green Communication researchers [20]. Authors have designed the integration of green communication on Virtex 4, Virtex 5, and Virtex 6 FPGA [21] in an energy-efficient instruction register. In [22], FPGA was used by the authors to produce a true random number by

FIGURE 6: Green computing model of CU.

inducing metastability. In [23], photovoltaic simulation modules with FPGA were built in real time. In [24], researchers carried out a frequency change design of the arithmetic logic unit (ALU) for FPGA. Virtex-6 FPGA was used in [25] researchers to design a four-bit unregistered counter, allowing for clock and cutting. Random access memory (ROM) architecture for Virtex-6 FPGA was interfaced in [26]. In [27], researchers have used FPGA device to design a low power model for wireless data communication. In [28], researchers used energy-efficient techniques such as scaling the capacitance value of the capacitor of output load to design a green communication model of FIR Filter. With the help of Spartan-6 FPGA, authors have designed a green communication model of FIR Filter [29]. In [30], different families of FPGA devices have been used by the authors to develop a green UART for communication purpose. In [31], various FPGAs of the Spartan Group have been used for the implementation of energy-efficient transceiver model. In [32], researchers have developed a green CU with FPGA. For designing such model, authors have

TABLE 1: Resource utilization of CU on Zynq Soc.

| Resource | Used | Available | Utilization % |

|----------|------|-----------|---------------|

| LUT      | 14   | 230400    | 0.01          |

| FF       | 4    | 460800    | 0.01          |

| IO       | 23   | 360       | 6.39          |

| BUFGs    | 1    | 544       | 0.18          |

used HSTL and HSULIO standards. By using Pseudo Open Drain (POD) IO standards, an efficient FPGA model of ALU has been designed by the researchers [33]. To endorse green communication, researchers have designed an energyefficient model of instruction register on FPGA [21]. In [34], different FPGAs and SOC has been utilized to enhance the performance of FIR filter for data communication and communication channel. In [35], LVCMOS IO standards are considered to execute a power-efficient UART for green computing and green communication. In order to endorse the green wireless communication, authors have projected the idea of Vedic multiplier design on FPGA devices by

FIGURE 7: Resource utilization of CU on Zynq Soc.

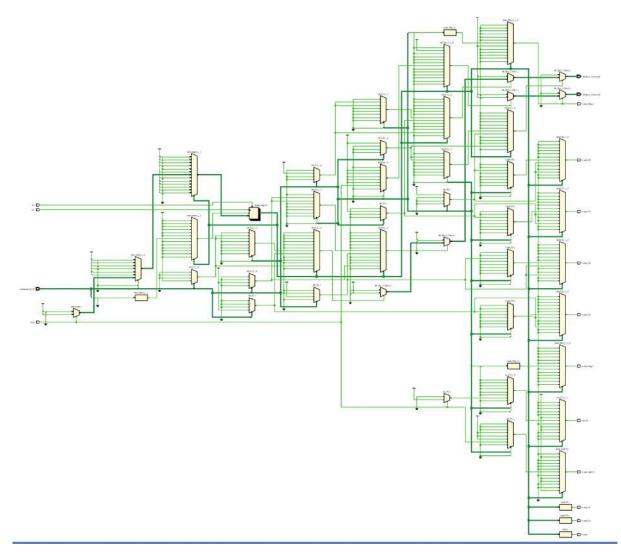

FIGURE 8: RTL of CU on Zynq SoC.

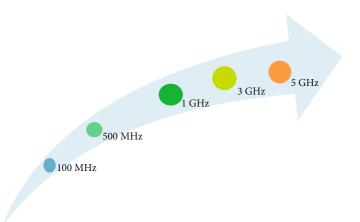

FIGURE 9: Frequency values for power calculation.

TABLE 2: Power calculation at 100 MHz.

| On chips power | Power (W) |

|----------------|-----------|

| DP             | 0.006     |

| SP             | 0.589     |

| ТР             | 0.595     |

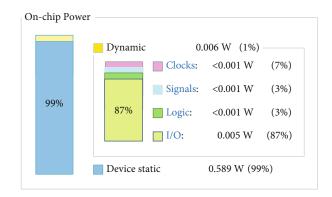

FIGURE 10: Power calculation at 100 MHz.

TABLE 3: Power calculation at 500 MHz.

| On chips power | Power (W) |

|----------------|-----------|

| DP             | 0.030     |

| SP             | 0.589     |

| TP             | 0.619     |

reducing its power consumption with the help of several IO standards techniques [36]. In [37], researchers built a powerefficient green communications paradigm employing the data outage and BUFG MB DSP state information (CSI) channel FPGA FF IO ports. In [38], authors have developed a green FF design for green wireless communication using FPGA architectures. In [39], researchers have used 28 nm FPGA device to design a thermal efficient as well as power-efficient CU to incorporate with green communication. Kintex Ultra-

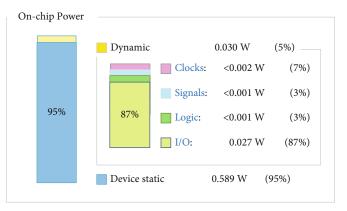

FIGURE 11: Power calculation at 500 MHz.

TABLE 4: Power calculation at 1 GHz.

| On chips power | Power (W) |

|----------------|-----------|

| DP             | 0.214     |

| SP             | 0.590     |

| TP             | 0.804     |

scale FPGA has been taken for modeling an energy-efficient CU for promoting the green communication [40, 41]. Therefore, it has been observed that in the recent times, a lot of work has been done for incorporating the concepts of green communication and the energy/power efficient devices for future generations with the help of FPGAs, but a very few works have been done with respect to the implementation of the CU for green communication. Therefore, this work is all about the realization of CU on Zynq Ultra-Scale FPGA for promoting the values and ethics of green computing and green communication. The FPGA version of green computing model of CU is represented in Figure 6.

# 3. Experimental Setup

The ultrascale Zynq Soc FPGA board is used to set up the CU implementation. The VIVADO HLx architecture suite

FIGURE 12: Power calculation at 1 GHz.

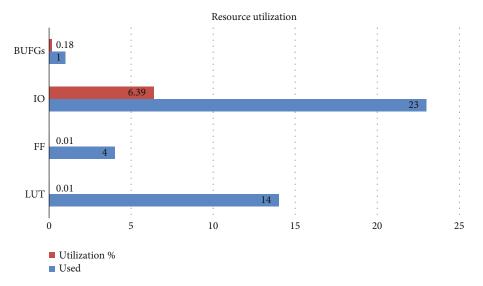

is the tool used to simulate CU on the FPGA board. Lookup tables (LUTs), flip-flops (FF), input-output (IO), and global buffers (BUFGs) are among the FPGA tools used to implement CU on the ultrascale Zynq Soc FPGA board, as shown in Table 1 and Figure 7 [42, 43].

The utilization of LUTs is 14, whereas 23-400 LUTs are available on FPGA boards for designing CU. Similarly, the utilization FF, IO, and BUFG are 4, 23, and 1, respectively, for designing CU on the ultrascale Zynq SoC FPGA. The Register Transfer Logic (RTL) of CU on Zynq SoC is shown in Figure 8.

#### 4. Results and Discussion

In addition, FPGA system dynamic power (DP) and static power (SP) are correlated with the power measurement of CUs using the Zynq FPGA [44]. The summation of both DP and SP is the overall total power (TP) consumption. The dynamic power is the device's leakage power release.

The SP is the summation of I/O, logic (L/G), clock (CK), ad signal (S/G). The power analysis of CU is done for five

and signal (S/G). The power analysis of CU is done for five set of frequency value such as 100 MHz, 500 MHz, 1 GHz, 3 GHz, and 5 GHz, as shown in Figure 9.

4.1. Power Calculation for 100 MHz. For the frequency of 100 MHz, the SP of the device is 0.589 W, which is 99% of the TP consumption. The SP is the summation of I/O, L/G, CK, and S/G. Here, I/O power is 0.005 W, and the CK, L/G, and S/G power are less than 0.001 W. The DP, also called as leakage power, is 0.006 W, which is only 1% of the TP consumption. The TP for 100 MHz frequency is 0.595 W, as shown in Table 2 and Figure 10.

4.2. Power Calculation for 500 MHz. For the frequency of 500 MHz, the TP consumption is 0.619 W, which is the summation of SP and DP which are 0.589 W and 0.030 W, respectively. The SP consumes 95% of the TP while DP consumes 5% of TP, as shown in Table 3 and Figure 11.

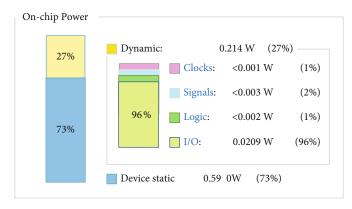

*4.3. Power Calculation at 1 GHz.* For the frequency of 1 GHz, the SP of the device is 0.590 W, which is 73% of the TP con-

TABLE 5: Power calculation at 3 GHz.

| On chips power | Power (W) |

|----------------|-----------|

| DP             | 0.184     |

| SP             | 0.590     |

| ТР             | 0.773     |

FIGURE 13: Power calculation at 3 GHz.

TABLE 6: Power calculation at 5 GHz.

| On chips power | Power (W) |

|----------------|-----------|

| DP             | 0.303     |

| SP             | 0.590     |

| ТР             | 0.893     |

sumption. The SP is the summation of I/O, L/G, CK, and S/G. Here, I/O power is 0.209 W, and the CK power is less than 0.001 W, while L/G and S/G power are 0.002 W and 0.003 W, respectively. The DP, also called as leakage power, is 0.214 W, which is 27% of the TP consumption. The TP for 1 GHz frequency is 0.804 W, as shown in Table 4 and Figure 12.

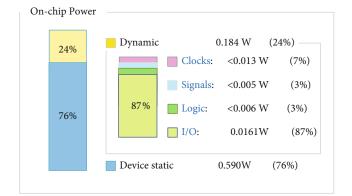

4.4. Power Calculation at 3 GHz. For the frequency of 3 GHz, the TP consumption is 0.773 W, which is the summation of SP and DP which are 0.590 W and 0.184 W, respectively.

FIGURE 14: Power calculation at 5 GHz.

TABLE 7: TP consumption for different frequency.

| Frequency | TP (W) |

|-----------|--------|

| 100 MHz   | 0.595  |

| 500 MHz   | 0.619  |

| 1 GHz     | 0.804  |

| 3 GHz     | 0.773  |

| 5 GHz     | 0.893  |

FIGURE 15: TP consumption for different frequency.

The SP consumes 76% of the TP while DP consumes 24% of TP, as shown in Table 5 and Figure 13.

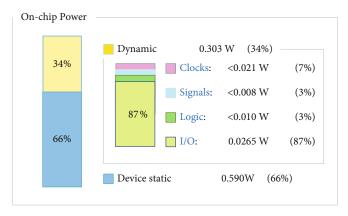

4.5. *Power Calculation at 5 GHz*. For the frequency of 5 GHz, the TP consumption is 0.893 W, which is the summation of SP and DP which are 0.590 W and 0.303 W, respectively. The SP consumes 66% of the TP while DP consumes 44% of TP, as shown in Table 6 and Figure 14.

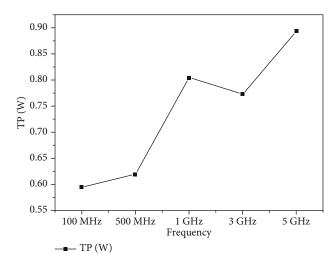

Form the power calculation for different values of frequency, it is found to be that the power consumption is maximum for higher values of frequency, i.e., 5 GHz and minimum for 100 MHz. The TP consumed for all frequency

TABLE 8: Comparison of TP consumption.

| References    | TP (W) |

|---------------|--------|

| [18]          | 2.636  |

| [20]          | 0.756  |

| [40]          | 0.725  |

| Proposed work | 0.595  |

FIGURE 16: Comparison of TP consumption.

values is depicted in Table 7 and Figure 15. It is also observed that there is an increase of 4.03% in TP as the frequency is raised to 500 MHz from 100 MHz. Also, the increment observed for 1 GHz, 3 GHz, and 5 GHz, which are 35.12%, 29.91%, and 50.08%, respectively.

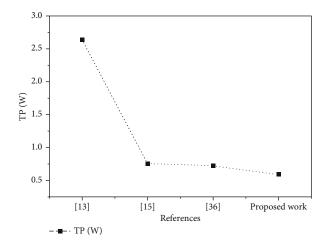

#### 5. Comparative Analysis

In this section, a comparison of TP consumption has been made with the existing works of CU on FPGA and with this work. In [18], with Spartan 6 FPPGA, the TP for CU is found to be 2.636 W, while in [20, 40], the TP consumption for CU was 0.756 W and 0.725 W, respectively. In this work, CU is designed with Zynq SoC FPGA for incorporating with green communication. The TP consumption with Zynq SoC is found to be optimized for 100 MHz frequency, i.e., 0.595 W. Therefore, it is observed that the TP consumption of CU is optimized in this proposed model. The TP of the proposed model is reduced by 77.42% from [18]. Similarly, the TP of this proposed model is reduced by 21.29% and 17.93% from [20, 40], respectively. The TP consumption of CU with existing models and the proposed model is shown in Table 8 and Figure 16, respectively.

# 6. Conclusion and Future Scope

The transition to green communication is critical in this period, as energy crises can be seen all over the world. As a result of this study, several steps have been taken to promote the concepts of green communication and power-efficient devices. The implementation of CU is carried out on the Zynq SoC ultrascale FPGA, and the simulation of the CU circuit, resource usage, and power analysis is carried out on the VIVADO Hlx Design Suite. It has been found that as the clock frequency of the circuit is increased, the power consumption decreases. As a result, it can be inferred that the overall power consumption is reduced when the clock frequency is low. Therefore, it is observed that there is an increase of 4.03% in TP as the frequency is raised to 500 MHz from 100 MHz. Also, the increment observed for 1 GHz, 3 GHz, and 5 GHz, which are 35.12%, 29.91%, and 50.08%, respectively. Also, the TP of the proposed model is reduced by 77.42% from [18]. Similarly, the TP of this proposed model is reduced by 21.29% and 17.93% from [20, 40], respectively, as shown in Figure 16. This CU circuit can be studied for other ultrascale and ultrascale plus FPGA devices in the future. Other power-saving methods, such as voltage, current, and capacitance scaling, can be used on the CU circuit as well. Impedance matching methods can also be used to make circuits more energy efficient with the aid of I/O specifications. For better performance, this FPGA design can later be converted to ASIC designs.

#### Data Availability

Data is available upon request.

### **Conflicts of Interest**

The authors declare no conflicts of interest.

#### References

- R. Mahapatra, Y. Nijsure, G. Kaddoum, N. Ul Hassan, and C. Yuen, "Energy efficiency tradeoff mechanism towards wireless green communication: a survey," *IEEE Communications Surveys & Tutorials*, vol. 18, no. 1, pp. 686–705, 2016.

- [2] L. Pietrosemoli and C. Rodríguez-Monroy, "The Venezuelan energy crisis: renewable energies in the transition towards sustainability," *Renewable and Sustainable Energy Reviews*, vol. 105, pp. 415–426, 2019.

- [3] https://www.computerhope.com/jargon/c/contunit.htm.

- [4] https://www.geeksforgeeks.org/computerorganizationcontrol-unit-and-design/.

- [5] J. H. Oh, Y. H. Yoon, J. K. Kim et al., "An FPGA-based electronic control unit for automotive systems," in 2019 IEEE International Conference on Consumer Electronics (ICCE), pp. 1-2, Las Vegas, NV, USA, 2019.

- [6] V. Bhatia, S. Kaur, K. Sharma, P. Rattan, V. Jagota, and M. A. Kemal, "Design and simulation of capacitive MEMS switch for Ka band application," *Wireless Communications and Mobile Computing*, vol. 2021, Article ID 2021513, 8 pages, 2021.

- [7] J. Bhola and S. Soni, "A study on research issues and challenges in WSAN," in 2016 International Conference on Wireless Communications, Signal Processing and Networking (WiSPNET), pp. 1667–1671, Chennai, India, 2016.

- [8] J. Bhola, M. Shabaz, G. Dhiman, S. Vimal, P. Subbulakshmi, and S. K. Soni, "Performance evaluation of multilayer clustering network using distributed energy efficient clustering with enhanced threshold protocol," *Wireless Personal Communications*, 2021.

- [9] K. Jairath, N. Singh, V. Jagota, and M. Shabaz, "Compact ultrawide band metamaterial-inspired split ring resonator structure loaded band notched antenna," *Mathematical Problems in Engineering*, vol. 2021, Article ID 5174455, 12 pages, 2021.

- [10] C. Dou, L. Zheng, W. Wang, and M. Shabaz, "Evaluation of urban environmental and economic coordination based on discrete mathematical model," *Mathematical Problems in Engineering*, vol. 2021, Article ID 1566538, 11 pages, 2021.

- [11] A. Rani and N. Grover, "Design and implementation of control unit-ALU of 32 bit asynchronous microprocessor based on FPGA," *International Journal of Engineering and Manufacturing*, vol. 8, no. 3, pp. 12–22, 2018.

- [12] S. Hauck and A. DeHon, *Reconfigurable Computing: The Theory and Practice of FPGA-Based Computation*, Elsevier, 2010.

- [13] D. Anguita, A. Boni, and S. Ridella, "A digital architecture for support vector machines: theory, algorithm, and FPGA implementation," *IEEE Transactions on Neural Networks*, vol. 14, no. 5, pp. 993–1009, 2003.

- [14] I. Kuon, R. Tessier, and J. Rose, FPGA Architecture: Survey and Challenges, Now Publishers Inc., 2007.

- [15] U. Farooq, Z. Marrakchi, and H. Mehrez, "FPGA architectures: an overview," in *Tree-based Heterogeneous FPGA Architectures*, pp. 7–48, Springer, New York, NY, 2012.

- [16] W. Wolf, FPGA-based system design, Pearson Education, 2004.

- [17] K. Kumar, B. Pandey, D. M. A. Hussain, A. Bhutto, A. K. Pandit, and E.-E. Baker, "Design of energy efficient control unit and implementation on high performance FPGA," *International Journal of Innovative Technology and Exploring Engineering*, vol. 8, no. 12S2, pp. 23–26, 2019.

- [18] S. P. Chaturvedi, A. Kaushik, and V. Baggan, "Power efficient control unit design using 40nm field programmable gate array," *International Journal of Advanced Science and Technol*ogy, vol. 19, pp. 694–709, 2019.

- [19] J. Pérez Fernández, M. Alcázar Vargas, J. M. Velasco García, J. A. Cabrera Carrillo, and J. J. Castillo Aguilar, "Low-cost FPGAbased electronic control unit for vehicle control systems," *Sensors*, vol. 19, no. 8, p. 1834, 2019.

- [20] B. Pandey, K. Kumar, S. C. Haryanti, R. R. Mohamed, and D. M. A. Hussain, "Power efficient control unit for green communication," *Test Magazine*, vol. 83, pp. 13422–13427, 2020.

- [21] S. M. T. Siddiquee, K. Kumar, B. Pandey, and A. Kumar, "Energy efficient instruction register for green communication," *International Journal of Engineering and Advanced Technology*, vol. 8, pp. 312–314, 2019.

- [22] M. Majzoobi, F. Koushanfar, and S. Devadas, "FPGA-based true random number generation using circuit metastability with adaptive feedback control," in *Cryptographic Hardware* and Embedded Systems – CHES 2011. CHES 2011, B. Preneel and T. Takagi, Eds., vol. 6917 of Lecture Notes in Computer Science, pp. 17–32, Springer, Berlin, Heidelberg, 2011.

- [23] E. Koutroulis, K. Kalaitzakis, and V. Tzitzilonis, "Development of an FPGA-based system for real-time simulation of photovoltaic modules," *Microelectronics Journal*, vol. 40, no. 7, pp. 1094–1102, 2009.

- [24] B. Pandey and M. Pattanaik, "Clock gating aware low power ALU design and implementation on FPGA," *International Journal of Future Computer and Communication2*, vol. 5, pp. 461–465, 2013.

- [25] B. Pandey and M. Pattanaik, "Low power VLSI circuit design with efficient HDL coding," in 2013 International Conference on Communication Systems and Network Technologies, pp. 698–700, Gwalior, India, 2013.

- [26] M. Bansal, N. Bansal, R. Saini, B. Pandey, L. Kalra, and D. M. A. Hussain, "SSTL I/O standard based environment friendly energyl efficient ROM design on FPGA," in 3rd International Symposium on Environmental Friendly Energies and Applications (EFEA), pp. 1–6, Paris, France, 2014.

- [27] G. Verma, T. Singhal, R. Kumar et al., "Heuristic and statistical power estimation model for FPGA based wireless systems," *Wireless Personal Communications*, vol. 106, no. 4, pp. 2087– 2098, 2019.

- [28] B. Pandey, N. Pandey, A. Kaur, D. M. Akbar Hussain, B. Das, and G. S. Tomar, "Scaling of output load in energy efficient FIR filter for green communication on ultra-scale FPGA," *Wireless Personal Communications*, vol. 106, no. 4, pp. 1813–1826, 2019.

- [29] B. Pandey, A. Jain, A. Kumar et al., *Energy Efficient and High-Performance FIR Filter Design on Spartan-6 FPGA*, 3C Tecnología. Glosas de innovación aplicadas a la pyme. Special Issue, 2019.

- [30] K. Kumar, A. Kaur, S. N. Panda, and B. Pandey, "Effect of different nano meter technology based FPGA on energy efficient UART design," in 2018 8th International Conference on Communication Systems and Network Technologies (CSNT), pp. 1– 4, Bhopal, India, 2018.

- [31] K. Kumar, B. Pandey, A. K. Pandit, Y. A. Baker El-Ebiary, S. A. Mjlae, and S. Bamansoor, "Design of low power transceiver on Spartan-3 and Spartan-6 FPGA," *International Journal of Innovative Technology and Exploring Engineering*, vol. 8, no. 12S2, pp. 27–30, 2019.

- [32] K. Kumar and P. Pandey, "HSTL and HSUL I/O standard based energy-efficient control unit circuit design on FPGA," *Gyancity Journal of Electronics and Computer Science*, vol. 4, no. 2, pp. 1–7, 2019.

- [33] B. Pandey, P. Sharan, L. L. Dhirani, and D. A. Hussain, "Role of scaling of frequency and toggle rate in POD IO standards based energy efficient ALU design on ultra scale FPGA," in 2018 10th international conference on computational intelligence and communication networks (CICN), pp. 50–53, Esbjerg, Denmark, 2018.

- [34] B. Pandey, B. Das, A. Kaur et al., "Performance evaluation of FIR filter after implementation on different FPGA and SOC and its utilization in communication and network," *Wireless Personal Communications*, vol. 95, no. 2, pp. 375–389, 2017.

- [35] K. H. Abed and R. E. Siferd, "VLSI implementation of a lowpower antilogarithmic converter," *IEEE Transactions on Computers*, vol. 52, no. 9, pp. 1221–1228, 2003.

- [36] K. Goswami, B. Pandey, T. Kumar, and D. A. Hussain, "Different I/O standard and technology based thermal aware energy efficient Vedic multiplier design for green wireless communication on FPGA," *Wireless Personal Communications*, vol. 96, no. 2, pp. 3139–3158, 2017.

- [37] C. C. Zarakovitis, Q. Ni, and J. Spiliotis, "Energy-efficient green wireless communication systems with imperfect CSI and data outage," *IEEE Journal on Selected Areas in Communications*, vol. 34, no. 12, pp. 3108–3126, 2016.

- [38] G. Gupta, A. Kaur, and B. Pandey, "LVCMOS based green data flip flop design on FPGA," in 2017 ninth international conference on advanced computing (ICoAC), pp. 41–45, Chennai, India, 2017.

- [39] K. Kumar, S. Ahmad, B. Pandey, A. K. Pandit, D. Singh, and D. M. A. Hussain, "Power efficient frequency scaled and thermal-aware control unit design on FPGA," *International Journal of Innovative Technology and Exploring Engineering*, vol. 8, no. 9S2, pp. 530–533, 2019.

- [40] A. Burg, M. Borgmann, M. Wenk, M. Zellweger, W. Fichtner, and H. Bolcskei, "VLSI implementation of MIMO detection using the sphere decoding algorithm," *IEEE Journal of Solid-State Circuits*, vol. 40, no. 7, pp. 1566–1577, 2005.

- [41] V. Degalahal and T. Tuan, "Methodology for high level estimation of FPGA power consumption," in *Proceedings of the 2005 Asia and South Pacific Design Automation Conference*, pp. 657–660, Shanghai, China, 2005.

- [42] A. Amara, F. Amiel, and T. Ea, "FPGA vs. ASIC for low power applications," *Microelectronics Journal*, vol. 37, no. 8, pp. 669– 677, 2006.

- [43] T. Tuan and B. Lai, "Leakage power analysis of a 90nm FPGA," in Proceedings of the IEEE 2003 Custom Integrated Circuits Conference, 2003, pp. 57–60, San Jose, CA, USA, 2003.

- [44] S. Ishihara, M. Hariyama, and M. Kameyama, "A low-power FPGA based on autonomous fine-grain power gating," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 19, no. 8, pp. 1394–1406, 2011.