# Volatile FPGA design security – a survey

Saar Drimer<sup>\*</sup>

Computer Laboratory, University of Cambridge http://www.cl.cam.ac.uk/~sd410

Version 0.96, April 17, 2008

#### Abstract

Volatile FPGAs, the dominant type of programmable logic devices, are used in space, military, automotive, and consumer electronics applications which require them to operate in a wide range of environments. The continuous growth in both their capability and capacity now requires significant resources to be invested in the designs that are created for them. This has brought increased interest in the security attributes of FPGAs; specifically, how well do they protect the information processed within it, how are designs protected during distribution, and how developers' ownership rights are protected while designs from multiple sources are combined. This survey establishes the foundations for discussing "FPGA security", examines a wide range of attacks and defenses along with the current state of industry offerings, and finally, outlines on-going research and latest developments.

## 1 Introduction

Field programmable gate arrays (FPGA) are generic semiconductor devices made up of interconnected functional blocks that can be programmed, and reprogrammed, to perform user-described logic functions. Since the early 2000s, FPGA vendors have gradually absorbed into the FPGAs functions that previously required peripheral devices. 2007's FPGAs have embedded processors, giga-bit serial transceivers, clock managers, analogto-digital converters, digital signal processing blocks, Ethernet controllers, substantial memory capacity, and other functional blocks beyond the arrays of basic logic elements they started out with in the mid 1980s. We are also seeing a process of industry-specific sub-families within a single family of devices that cater to embedded, DSP, military and automotive applications; this means that the distribution of the various embedded blocks is different across family members.

The off-the-shelf availability and reprogrammability make FPGAs competitive with the generally higher performing application specific integrated circuits (ASIC) when the upfront ("non-recurring engineering") costs and development times are not justified. Most

<sup>\*</sup>The author is supported by a grant from Xilinx, Inc.

new generations of FPGAs are manufactured using the latest technologies to be as competitive as possible with ASICs in terms of performance, power and price. Against commodity application specific standard products (ASSP) (devices that perform a fixed set of functions) FPGAs compete by being reprogrammable and able to process any number of functions, not only those which are pre-set. The ability to parallelize operations and execute customizable functions also makes them performance competitive compared to sequential microprocessors.

The growth in both capacity and application space of FPGAs has two main security implications. Firstly, today's FPGA designs represent a significant development investment which needs to be protected. Secondly, FPGAs are increasingly being used in applications that require security properties that are either not available today, or that have yet to be adequately investigated. Both have brought recent attention to the security attributes of FPGAs in the military, automotive, consumer industries, and also the research community, each with its own requirements and security perspectives.

This document surveys the current state of the FPGA security field with the goal of being a reference to engineers and researchers interested in the challenges of providing protection to FPGA designs in both distribution and operation<sup>1</sup>. As the basis for our discussion, we will start with defining the FPGA usage model and its participants in Section 2. Possible attacks are described in Section 3, followed by defenses in Section 4. Section 5 covers the current state of research and finally, Section 6 deals with issues of trust, adversary classification, and security metrics.

This survey is primarily about the security of SRAM-based volatile FPGAs and does not, in most part, cover non-volatile programmable logic devices or one-time programmable devices. While some of the discussion will apply to non-volatile devices, they should be considered separately as they have different usage and threat models. They do have attractive attributes, however, and are generally regarded as more secure, but with a compromise made on performance and capacity [78]. Finally, many of the issues discussed in this document are not necessarily exclusive to FPGAs and may apply to other integrated circuit devices or software. The focus here, however, is to put all those in the perspective of the FPGA usage model.

# 2 Usage model

The ability to field-reprogram the FPGA a distinct advantage, but also what exposes it to exploits. In this section we will discuss the unique usage model of FPGAs, its participants, and the interactions between them.

### 2.1 Principals

"A principal is an entity that participates in a security system. This entity can be a subject, a person, a role, or a piece of equipment, such as a PC, smartcard, or card-reader terminal" [9, p9]. FPGAs, FPGA vendors, designers, programming cables *etc.*

<sup>&</sup>lt;sup>1</sup>In early 2004, Wollinger, Guajardo, and Paar wrote the first comprehensive survey of the topic [122], which is a good companion to this one.

are principals interacting in a system whose security we are concerned with. With our security perspective, we can consider their communication as part of the execution of a security protocol. Introduced below are the principals that partake in the design and distribution of FPGA products, along with their security requirements<sup>2</sup>.

**FPGA vendor.** Altera and Xilinx have traditionally been the leaders of the programmable logic industry and in constant competition over market dominance, alternating positions over the past twenty years. In 2005, Xilinx held 50% of the programmable logic market share, Altera 33% and Lattice at a distant third place with 6% [33]. Every FPGA vendor introduces a new FPGA family roughly every 12 to 18, each costing many millions of dollars do design, fabricate, and test for production. The competition is good because it forces the vendors to be well-tuned to the needs of their customers. It also means that vendors need to be aggressive yet conservative at the same time when introducing new families, as failure of one can be devastating to the company. The amount of transistors that can fit in a die is limited, so he vendors only introduce embedded functions that are needed by the majority of their customers or several large ones, or are in-line with a long-term marketing strategy (for example, embedded hard processors, large memory blocks or structured-ASIC families). Customers must be willing to pay for all the functional blocks on the die (by accepting the price of the FPGA) even if they are left unused. This is important to remember we consider the addition of security features to FPGAs, as they must be financially profitable to the FPGA vendors.

Security-wise, FPGA vendors have two dominant concerns. Firstly, they need to protect their own proprietary designs and technology from being reverse engineered, copied, exposed, or modified. Secondly, they need to provide their customers means to protect their own designs throughout the design flow and in the field. Customers' recent interest in protecting designs has made security a competitive factor, prompting FPGA vendors to pay more attention to these issues; the gradual increase in security-related feature offerings reflects this.

**Foundry.** All FPGA vendors are fabless, which means that they design the FPGAs but partner with other companies, called foundries, for manufacturing. They are presented here as an independent principal since they are crucial to the security of the FPGA because that it is possible that designs will be modified or stolen during the process of fabrication. If the foundry is tasked with embedding cryptographic keys, serial numbers on which a security scheme relies on, this could also be a problem. In the past "trusted foundries" were established in the country where the devices were designed such that strict control and supervision was possible. Today, this is significantly harder as advanced fabrication facilities have migrated to Asian countries where this kind of control by a foreign government is not possible. To attest to the importance of this, at least as far as governments are concerned, a 2005 report [116] by the U.S. Department of Defense discusses the "alarming" rate in which "critical" microelectronics facilities are migrating to foreign countries.

$<sup>^{2}</sup>$ In 2002, Kean [55] provided a list of principals in the context of "intellectual property" protection, which is expanded here to cover all aspects of the design flow.

**System developer.** The FPGA vendor sells the FPGAs, often through distributors, to the system developer who incorporates it into a product. System developers can be divided into two groups based on their security needs and views. Using this categorization we will be able to evaluate the effectiveness of various defenses from their perspective.

- Cost-conscious. The goal of the commercial product designer is to meet the product's specifications at the lowest cost, while maintaining reliability. Often, there is a trade-off between system performance and cost and a general tendency by engineers to resist additional components, design delays, and decrease in reliability that translates into higher maintenance and support costs. The typical life-cycle of a commercial product is quite short, from months to a few years, and therefore, its proprietary design and may only need to be protected for that long; after that period, the system is no longer a worth-while target for attackers. The predominant threat faced by commercial product designers is the creation of a competing cheaper product that is derived from the original. Therefore, it is sufficient to make the process of stealing the design at least as costly as re-creating it (or slightly harder than a competing product), while keeping the cost of this defense to a minimum.

- Security-conscious. Government contractors and security-industry system developers are concerned with protecting designs, methods of operation, and communications for a substantial length of time — from years to decades — while cost considerations may be secondary. The security-conscious designer is often interested in robust, "approved" security mechanisms, based on established protocols and algorithms. In these applications, cost-performance may be important, but not at the expense of security and reliability. Some security-conscious designers make use of older, more mature, and hence more reliable, integrated circuits. Others take advantage of the most recent technologies that are more resistant to invasive attacks and increase the entry threshold of potential adversaries due to the higher cost of equipment and know-how.

It appears that FPGA vendors have a challenge in supplying security features to their customers: in a single resource-limited device, they would (ideally) like to satisfy both cost- and security-conscious designers, who have significantly different outlook on security, and what they are willing to spend for it.

**Cores designer.** Cores are ready-made functional descriptions that allow system developers to save on design cost and time by purchasing them from third-parties and integrating them into their own design. A single third-party core can also occupy the entire FPGA to create a "virtual" application specific standard products" [55]. Cores designers sell their cores in the form of hardware description language (HDL) or complied netlists, while FPGA vendors provide some cores for free (they make the money from selling the FPGAs), and some designers create free open-source designs available though sites like http://www.opencores.org. There exists free and commercial cores for nearly every popular digital function.

An ideal distribution model would enable system designers to evaluate, simulate, and integrate cores into their own designs while maintaining confidentiality of the cores, limiting the number of instances made and make every instance operational only on a specific device. A benefit of this model is that it will also enable a pay-per-use payment structure, as opposed to blanket licensing, that would enable a greater market for the cores. To date, there are no mechanisms to enable this "core distribution business" that answers to all the needs specified above; we will discuss this issue in detail in Section 5.3.

**EDA software vendor.** Electronic design automation (EDA) tools are used for the development of printed circuit boards, integrated circuits, FPGA designs, and extensively used for simulation. The various EDA vendors provide the tools that are used by all the principals mentioned above with FPGA vendors also being EDA tool suppliers. Therefore, EDA software vendors play a pivotal role in the FPGA design flow and their contribution is critical to the security of both the FPGA and FPGA-based products.

**System manufacturer.** The system developer does not usually have the facilities to mass produce a product, so therefore, the designs are sent to the system manufacturer for production and often also for testing. This principal includes all parties involved in the process of making the system ready for delivery: printed circuit fabrication, assembly (where components are soldered onto the board), testing, and even packaging.

**System owner.** This principal possesses the FPGA-based system, which is no longer under direct control or supervision of its developer. This could be a legitimate user who purchased the system at a consumer-product store, or a government who obtained it from a fallen reconnaissance aircraft; both may be malicious ("enemy"), trying to pry secrets out or circumvent protection mechanisms. Depending on the product, the system developer may restrict the owner from using certain functions in order to prevent theft of services, or from executing unauthorized code on the system. For example, set-top box developers (such as TiVo) profit from providing programming services, not from supplying the hardware itself. Therefore, they have an incentive to invest in mechanisms that prevent the theft of these services using their own or other hardware. Some cell phone manufacturers have mechanisms to prevent users from choosing a network other than the one they are "supposed" to be locked into. The security-conscious designer may want to have mechanisms to completely erase or destroy portions of the system when it falls into the "wrong" hands and perhaps employ the ability to "call home" upon tampering.

**Trusted party.** In order to reach the security goals of a protocol, a principal that is trusted by all other principals is often required for storing, processing and transferring data and keys. It is easy to add a trusted parties to a protocol though they are best avoided since implementing them in reality is difficult. The centralized nature of a trusted party makes it vulnerable to denial of service attacks, and a lucrative target for attackers. In addition, it may not even be possible to find one principal that is mutually trusted by all others. More practical issues such as location, trusted personnel, physical security and so on are also problematic.

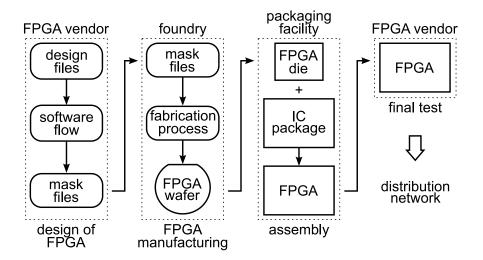

Figure 1: Simplified depiction of the FPGA design, manufacturing, packaging, and testing processes.

### 2.2 Design and manufacturing flow

Figure 1 shows a simplified design flow of an FPGA. The design files (mostly HDL) are processed by software tools to produce a netlist, which is then laid-out to provide the physical representation of gates and transistors. From the layout, files describing the "mask sets" used to manufacture the device are created and delivered to the foundry where they are physically made into "wafers" (this is a simplification, masks and other intermediate steps may not necessarily be performed by the foundry, but by another principals). The wafers are then tested for good die, which are identified and marked, and then sent for assembly where the good die are cut and attached to a carrying package. Finally, these packaged die are sent back to the FPGA vendor for final testing before they are distributed.

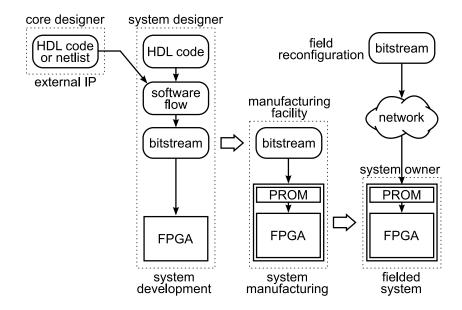

Figure 2 shows the design and manufacturing processes of the system developer who uses an FPGA in his product. It is not meant to be a complete description, but rather to provide the points at which principals interact. It is important to review these processes as every attack or vulnerability we will discuss can be placed at one or several points of this model. In the development phase, the system developer combines internally- and externally-designed cores that describe the intended logic functions of the FPGA. At this stage, the system in which the FPGA operates is also developed. The software flow, as shown in Figure 3, starts with HDL synthesis that optimizes and translates the functional description according to the resources available in the target FPGA architecture (e.g. Stratix look-up table, Spartan multiplier) into a netlist. Netlists contain a description of the instantiated primitives and the connections between them, usually in the standardized electronic design interchange format (EDIF). Synthesis tools are available from several EDA vendors, not necessarily from the FPGA vendor of the target device, unlike the tools used for the rest of the process. The information contained in the netlist is then mapped/fitted to the specific primitives of the architecture and then those are

Figure 2: The development, manufacturing, and distribution of an FPGA-based system. The system developer must be assisted by several other principals such as manufacturers, and cores and EDA vendors. At the end of the development cycle the product is in the system owner's hands.

Figure 3: Expanded view of the software flow used to process a functional description in a high-level language into a bitstream file that is programmed into the FPGA to have it perform this functionality.

placed and routed to a particular target device to produce a placelist<sup>3</sup>, where the specific route of every interconnect and physical placement of all primitives are described. The placelist is then encoded to produce a bitstream file that when loaded onto the FPGA establishes the routing to and from all the instantiated elements by setting the state of memory cells, pass gates, and routing switches. The bitstream also sets the attributes of all instantiated blocks such that once it is loaded, the FPGA performs the logic functions that were initially described in HDL. As SRAM FPGAs are volatile, they must receive the bitstream on every power-up from an external source, which is traditionally a non-volatile (NV) device, EEPROM or Flash, placed nearby on the printed circuit board. The design is simulated at the HDL, netlist, and post-PAR stages, and is also verified for correct operation when "executed" on the FPGA itself in its intended hardware setting. Static timing analysis takes into account the architecture and actual delays after the place and route process in order to verify that timing violations, such as of setup and hold timing allowances, do not occur. When the prototyping process is done, the system is manu-

$<sup>^{3}</sup>$ This new name is used in order to distinguish the information described in these files from the information described in netlists.

factured, the bitstream is programmed into the device or NV storage and tested before being shipped. In the field, the finished product is in the hands of the system owner and thus, no longer under the control of the designer. Field reconfiguration, as the name suggests, allows the user or system developer to reprogram the FPGA while it is in the field. For example, a firmware upgrade to a digital camera may be done remotely by the user plugging it into an Internet-connected PC, or an upgrade to a car's processor be done by a service technician at a service station.

## 3 Attacks

Security is an arms-race. Defenses against malicious tampering or use are put in place only to be broken and later be replaced by other, hopefully better, measures. Smartcards and microcontrollers have been in the midst of such a race for the past two decades, starting with naive, if present at all, security mechanisms and incrementally improving as exploits were discovered; examples are the work by Anderson, Kömmerling, Kuhn, and Skorobogatov [10, 11, 61, 96]. The interest in finding vulnerabilities in smartcards emerged in the mid-1990s when they started being used for pay-TV application, and later for banking; Anderson *et al.* [12] provide a recent survey of the security properties of cryptographic processors.

We are now seeing the beginning of such an arms-race for FPGAs. With FPGAs being used in more applications that require security features, and as these designs become more valuable, attackers search for vulnerabilities and developers for defenses. This section examines possible attacks against FPGAs; a subset of those are unique to FPGAs though most apply to other devices and systems but are considered here for their relevance to FPGAs. The first few attacks are closely related to the usage model, followed by attacks on the FPGA while it is operating, then physical attacks, ending with system-level attacks.

### 3.1 Cloning, overbuilding fraud, and mislabeling

FPGAs are generic, which means that a bitstream made for one device can be used in any other of the same family and size. As such, attackers can, and do, clone bitstreams by recording them in transmission to the FPGA and use them in other systems or products, usually cheaper clones that compete with the originals. Since cloning requires no more than a logic analyzer and a competent technician, it is considered to be the most common security vulnerability of volatile FPGAs. The attacker, who does not need to understand the details of the design regards it as a black-box, and only needs to invest in copying the circuit board the FPGA is mounted on, saving on the significant development costs. The original system developers have two main concerns with regards to cloning. Firstly, cloned systems take hurt the bottom line after a significant development investment, and secondly, if the clone is marked as the original the system developer suffers a reputation and support loss because the fake is almost universally of poorer quality. Since this is the path of least effort for the attacker, an increase in cost for a successful attack may act as an effective prevention mechanism to make cloning unprofitable, at least for a while.

The electronic industry has been facing increased amounts of counterfeit hardware in the last decade, mostly coming from Asia. Aside from cloning of systems, overbuilding or run-

on fraud is a major concern to many big companies. When a product is manufactured at a third party facility that fabricates, assembles and tests the hardware before it is shipped to the customer, it may manufacture more than the ordered quantities and sell the excess without incurring development costs. They may even sell the designs themselves (PCB layout, bitstreams) to competitors. To avoid this, companies qualify facilities as "trusted" and supervise/audit them, but this is hard to do in many countries, and may be unaffordable for small companies.

Mislabeling of FPGAs is also a problem for both FPGA manufacturers and system developers. Modifying or erasing markings on an IC package is trivial, and system designers have been doing so for years to make the reverse engineering of a system slightly more difficult. But when FPGAs are not purchased through authorized distributors<sup>4</sup>, how can the buyer be sure that the packaging's markings match what is inside the package? If it is a completely different device, or even a smaller FPGA family member, that would be quite simple to verify, albeit only after the purchase. Speed grades are harder to measure, though, and a slower die may be marked and sold as faster ones for a premium. There is no way for the buyer or seller to really know what is under the package, aside from programming it with a bitstream and observing correct results, though for verifying the speed is more complicated. For commercial companies it is probably safest to buy devices from the vendors or their distributors rather than on-line, though for hobbyists that only need small quantities for cheap, the risk may be worth it.

Numbers for these types of fraud are hard to come by as companies are not ready to disclose their losses unless they must. An industry consortium of large hardware development companies called the Alliance for Gray Market and Counterfeit Abatement has estimated that in 2006 [6] one in ten purchased products were fake either by over-building or cloning. These types of fraud are hard to prevent, especially when they occur in places where ownership rights are not enforced. We will discuss some counter measures against the issues above in section 4.

## 3.2 Reverse engineering the bitstream

We can define *bitstream reversal* as the transformation of an encoded bitstream into a functionally equivalent description of the original design. If we look back to Figure 3 it is reverse the process from bitstream back to HDL or netlist. Partial bitstream reversal can be further defined as the extraction of data from the bitstream, such as keys, BRAM/LUT content, or memory cell states, without reproducing full functionality. Reverse engineering is legal — with some restrictions — in many countries for interoperability reasons or discovery of infringement of patents or other rights [79]. Full bitstream reversal would, of course, reveal the entire design and the data could be used to produce another bitstream which is completely different from the original such that it would be hard to prove infringement. Keys hidden in the bitstream would also be compromised, and if the attacker is after determining which cryptographic algorithm is used, partial reversal can also be useful.

In the early 1990s, start-up NeoCAD has created complete FPGA design development tools for various vendors' FPGAs. Contrary to common belief, and according to Xilinx [69,

<sup>&</sup>lt;sup>4</sup>Obsolete devices can still be found on-line years after the manufacturers abandoned them.

113], NeoCAD did not in fact reverse engineer the bitstream, but rather, the bitstream generation executable so that their tools could generate compatible bitstreams for Xilinx FPGAs. In 1995 NeoCAD was acquired by Xilinx to become its software division. In the late 1990s, start-up Clear Logic was able to use Altera's software-generated bitstreams to produce pin-compatible, smaller, cheaper, laser-programmable ASICs (they were also more secure since they did not require an external bitstream source). Altera subsequently sued for damages while requesting the halting of Clear Logic's operations. In 2001, Clear Logic was barred from asking its customers to use Altera's software tools since it violated their end-user license agreement (EULA), and in late 2005, Altera won the case and was awarded damages [8, 117]; Clear Logic had already ceased operations by 2003. Although both cases involved the *generation* of compatible bitstreams, neither company was able to completely reverse engineer them to obtain the original functional description. NeoCAD reverse engineered a binary executable and Clear Logic used existing bitstreams to laserprogram devices made from reverse engineering the FPGA's mask sets. We must also remember that compared to today's FPGAs, the ones of NeoCAD and Clear Logic's time were much less sophisticated; so even if they did reverse engineer bitstreams, the task would have been considerably easier than doing something comparable today.

The bitstream's encoding is largely undocumented and obscure, but not encrypted or confidential in a cryptographic sense, with FPGA vendors keeping this encoding a secret as they do for the chip's own design and layout information. As we shall see in Section 4.3, several design protection schemes rely on the continued secrecy of this encoding with vendors having some commitment to keeping it this way. The obscurity, complexity, and size of the bitstream makes the reverse engineering process difficult and time consuming, though theoretically possible. There are no reports of successful reversal of modern FPGA bitstreams as defined above or even a cost estimate that is backed up by data and empirical analysis. The possibility of legal action is certainly an effective deterrent in academic and commercial environments, although for some organizations and in certain countries, these are less of a concern. The incentives for full reversal increases proportionally with the value represented in bitstreams and with the increased use of FPGAs, and since there is a rapid growth in both, we can expect much more activity in this area.

Extracting RAM and LUT content from bitstreams is not new (see Ziener et al. [24], devices' datasheets, and vendors' own tools). The harder part of the process, however, is to automate the process of converting the placelist to a netlist from which the original functional design can be extracted. A topical Internet search yields quite a few hits for projects and services, though most of which seem to be half-baked or stale, with companies providing such a service making claims that are hard to verify. The one exception is "ULogic", a "free software project aimed at netlist recovery from FPGA closed bitstream formats" [115]. Ulogic's developers Note and Rannaud have produced a report [83] in which they describe a tool they developed can convert Xilinx's bitstreams into placelists. The Xilinx Design Language (XDL) is a largely undocumented plain text representation of placelists (which are otherwise in unintelligible form) supported by the Xilinx tools from at least ISE version 4.1i. Using the XDL, developers can directly manipulate placed and routed designs, and even bypass the entire software flow to create XDL representations from scratch. From XDL, the files can be converted back to a placelist and encoded to a bitstream. This allows the iterative process of producing an XDL design, converting it to a placelist and then to a bitstream; by changing single bits, routing and settings at a time, one can create a database that correlates placelist data to bitstream bits. Note and Rannaud have simply automated this process to create a "de-bit" tool in addition to "xdl2bit", which is a bitstream generation tool that is claimed to be equivalent to Xilinx's "bitgen" for some device families, but is much faster. The authors rightly assess the security risks to deployed systems due to their development by stating that the step of "making sense" of the data is still missing, namely, the full reversal to a "true netlist". The eventual goal of the Ulogic project is producing a netlist, and there may be less public efforts with similar aims; the increased value embodied in bitstream will inevitably drive more people and organization to invest time to accomplish automated full reversal. If reverse engineering is a concern, or thought to be within reach of a potential adversary, it is probably prudent to no longer rely on bitstream encoding, even though it is still unclear what is the actual cost of full reversal. Certainly, hiding keys in look-up tables and RAMs is not a good strategy because it only requires a partial reversal and basic knowledge of the bitstream's construction. In Section 4 we will discuss some solutions that increase the efforts required to be invested by an attacker.

#### 3.2.1 Open formats and hardware

The "open hardware" design community's discussion [57, 91] on FPGAs, and of other open format matters, is quite active and is worth noting in this context. Open hardware advocates are pushing towards a hardware equivalent of the software open source efforts and seeking manufacturers' support. The dominant argument is that open bitstreams and architectures would enable third parties — perhaps open-source — to develop vendorindependent tools that may include support for unique functions and languages otherwise not made available by the vendors' tools. Megacz [75] demonstrated this by the creation of a complete open-source application programming interface (API) for bitstream manipulation for an Atmel FPSLIC FPGA, after its configuration bitstream format was posted on the *comp.arch.fpqa* Usenet newsgroup in late 2005 [39]. One of Ulogic's stated goals is proving to FPGA vendors that third-party tools can be better than their own, demonstrated by their nimble bitstream encoder. Up to now FPGA vendors have been resisting this approach by mostly staying out of the debate, with the rare exception of the Xilinx XC6200 FPGA in 1997. This is firstly, in order to avoid supporting people who create their own bitstreams and use home-grown tools; this argument can be easily dismissed, though discrimination for supporting the hardware based on certain software tools is not going to be easy, and bad for public-relations, so it is not that simple. Secondly, due to fear of competition with their own software tools and loss of control over how their devices are used. Lastly, and most importantly, the "openness" will also require revealing proprietary information, including portions of the architecture, which is the edge vendors have over one another and which they cannot afford to lose. But it may simply be that there is no business opportunity there, as the most relevant consumers of FPGAs are large companies who prefer to get the whole package, including support, accountability, and regular updates. Business motives dictate that appeasing the occasional researcher and open-source advocate is not worth the risk to the bottom-line. In 1998, however, we saw Xilinx release the JBits API [41], which allowed users to directly manipulate bitstreams. It supported only a few device families and was not very convenient to use, but it marked a step in the direction of openness that would enable the creation of independent tools.

JBits was quite extensively used by academic researchers and was updated only to the Virtex-II family and it seems to have been abandoned since.

## 3.3 Readback

Readback is the process of retrieving a snapshot of the FPGA's current state while it is still in operation. Upon request, the FPGA sends the snapshot that includes configuration, look-up tables, and memory contents to the host PC, or other device, via the configuration port. This image is different from the original bitstream by missing the header, footer, initialization commands, and no-ops; of course, the dynamic data in LUTs and BRAMs is also different from their initialized state. Readback is a powerful characterization tool in the verification and production testing of the FPGA by the vendors, and also allows the system developer to verify the correctness of the design as it is operating on the FPGA itself.

If enabled, however, an attacker can readback the design, add the missing static header and footer and use it in another device, re-program the FPGA with a modified version, or reverse engineer it. It also enables an active "readback difference attack" where the attacker is able to observe signal changes on an individual clock-cycle basis to bypass defense mechanisms. Consider the case where a functional core is waiting for an enable signal from an authentication process. If the adversary has control over the input clock, he can take a snapshot before the signal is set, clock the design, and then take another snapshot. Through a relatively easy iterative process of comparing the snapshots, the attacker can determine which bits are required to be changed in order to modify the state of signals. Then, the original bitstream can be modified to have the enable signal asserted permanently, subverting the defense. In contrast, readback can also be used as a defense mechanism by providing indications of tampering, such as in the case of ionizing radiation attack described in the following section.

Xilinx provides a bitstream bit for disabling readback, but it can be easily found. However, when bitstream encryption is used, multiple, majority-voted, disabling registers are activated within the FPGA to prevent readback [70] [123, User Guide 071]. Lattice devices also disable readback when bitstream encryption is used [66, Tech. Note 1109]. In theory, these disabling bits can be located via invasive attacks, but there is no evidence that this has been accomplished or even attempted. Altera's devices do not have readback capabilities and are therefore not vulnerable to this type of attack.

## 3.4 Side-channels

Side-channel attacks rely on device-external measurable manifestations of internal processes to deduce secret data or modes of operation by exploiting the implementation rather than the algorithmic construction. The challenge for designers interested in preventing this analysis is the isolation of internal operations of integrated circuits from their environment as they interact with other devices, and consume and emanate energy in the form of electromagnetic and heat radiation. Described below are three types of side-channel attacks and their relevance to FPGAs.

#### 3.4.1 Power analysis attacks

Integrated circuits consume power in two ways. Dynamic power consumption is due to CMOS gates changing state while parasitic and load capacitance are charged or discharged according to the logic transition,  $0 \rightarrow 1$  or  $1 \rightarrow 0$ , respectively; this also includes the brief low impedance period caused by both the p- and n-mos transistors simultaneously conducting during the transition. A simple dynamic power consumption model for a CMOS gate is:

$$P = C_{\text{load}} \cdot V_{\text{supply}}^2 \cdot f \cdot A$$

where  $C_{\text{load}}$  is the load capacitance of the gate, which includes wire, parasitic and output capacitance, that need to be charged or discharged with every transition;  $V_{\text{supply}}$  is the supply voltage to the gate; f is the operating frequency; and A is the probability of a  $0 \rightarrow 1$  or  $1 \rightarrow 0$  transition. Standaert *et al.* [100] describe a simple experiment that confirms this model on an FPGA. To obtain power trace samples, most of the literature describe measuring the voltage across a low-value resistor placed between either the circuit's power or ground, and the respective external power supply terminals; the exception is Bucci *et al.* [17] who suggest an active sampling circuit to enhance the quality of samples. Shang *et al.* [94] provide a thorough analysis of the dynamic power consumption of a 150 nm Xilinx Virtex-II FPGAs by looking at the power contribution of resources along a signal path. Their results show that about 60% of dynamic power dissipation is due to interconnect routing (the effective capacitance of driven wires), 16% to logic, and 14% to clocking resources.

Static power consumption is the power consumed when the circuit's gates are not changing state. Shang et al. estimated that for a 150 nm FPGA, 5-20% of the total consumption is static and is due to gate leakage. Gate leakage has dramatically increased for 90 nm and 65 nm transistors built for high frequencies, often accounting for a larger portion of total consumption than dynamic power. This leakage is due to the decreasing dimensions of the transistors, and the reduced threshold voltage, which cause relatively more current to flow between the source and drain terminals and through the gate oxide. This leakage is also very sensitive to temperature variations, and therefore, not uniform across the die, or in time, and may correspond to switching activity of the circuit. Kim et al. [58] provide an excellent introduction to the issues associated with static power consumption. The smaller dimensions have an effect on dynamic consumption as well since  $V_{\text{supply}}$  is reduced and the capacitance are smaller, and the interconnects are shorter, resulting in less consumption; albeit, in general, there are more transistors switching as there are more transistors per device. Up to now static power consumption has been largely ignored, though it may be interesting to examine how it contributes to the analysis by providing data dependent information.

Analysis of the current consumption patterns of an integrated circuit may reveal information about the specific data it is processing, with the most common target is finding the key used in a cryptographic operation. In 1999, Kocher *et al.* [60] introduced two types of power analysis, simple (SPA) and differential (DPA). With SPA the attacker directly searches power traces for patterns such as algorithmic sequences, conditional branches, multiplication, exponentiation, and other signatures that allow the inference of key material. DPA compares acquired traces with a statistical power consumption model that is tailored to the target device and specific implementation. This model is based on prior knowledge or analysis of the device which is then enhanced by many recorded samples of controlled operations, for example, by processing known plaintexts with known keys. This way, even if the implementation details are not fully known, the attacker can infer key material based on controlling single bit changes during an encryption. While attacking a device, the model enables the attacker to iteratively guess candidate key bits and obtain statistical correlation between model and measurement. The statistical analysis is required to increase the signal-to-noise ratio such that a candidate guess is distinct from the samples; if noise is present, more samples are required to reach that distinction, but most noise sources and patterns can be modeled such that they can be sufficiently removed. In some cases, even a small number of known bits can make it possible to mount a brute force search for the remainder.

Most power analysis research to date has been done on microprocessors, such as smartcard ICs, for which a model is relatively easy to construct and power traces are simple to obtain due to their sequential and slow operation. Mangard et al. [73] provide a comprehensive introduction to power analysis techniques for smartcards. Power analysis of FPGAs has started receiving increased interest since 2003 with Ors et al. [85] and Standaert et al. [99] being the first to examine the possibility of successful attacks. Ors et al. described a power analysis platform for examining Xilinx's 220 nm Virtex device, with a successful SPA attack on an elliptic curve implementation operating in isolation. The research of Standaert et al. on the same Virtex FPGA has shown that SPA is not practical for most paralleled cryptographic implementations when many concurrent operations are running on a single device. DPA, however, was deemed to be possible, and within a year Standaert and co-authors [100, 101] demonstrated a potentially successful attack based on statistical correlation techniques against an implementation of the Advanced Encryption Standard (AES) and Data Encryption Standard (DES). The investigation showed that the pipelining of the cipher does not protect against DPA since operations are separated into registered states and are thus better observed in the power traces. However, an unrolled implementation, where each round is implemented on its own for faster throughput (at the expense of more resources), was shown to measurably increase the efforts of a would-be attacker. This is because all encryption/decryption rounds are run concurrently and, with the key unknown, the contribution to the power trace is effectively random noise that cannot be predicted and easily removed during analysis. In practical scenarios the cryptographic operation would be but a small subset of all the concurrent operations on the FPGA, all contributing noise. In 2006, Standaert et al. [102] analyzed the power signature of isolated pipelined structures on a 180 nm Spartan-II FPGA, improved their previous results from [100], and confirmed some of the results of Shang *et al.* They also concluded that pre-charging buses with random values to mask transitions, at the expense of resources and throughput, amounts to added difficulty to an attacker, but should not be relied on as a single solution against power analysis.

Power analysis attacks could be made harder if operations that depend on secret data have the same power signature as ones that do not; achieving this, however, is incredibly challenging and the research community is constantly evaluating and critiquing new and old defense techniques. Standaert *et al.* [103] provide a survey of currently suggested defenses against power analysis attacks, namely, time randomization, noise addition, masking, and dynamic and differential logic, with the conclusion that no single solution can eliminate the susceptibility to power analysis attacks. Messerges [76] also surveys the weaknesses of power analysis countermeasures. Tiri and Verbauwhede [112] proposed an FPGA-specific countermeasure called wave dynamic differential logic (WDDL) synthesis. Using differential logic and pre-charging of the gates, this method increases the resistance to DPA by making power dissipation independent of logic transitions with the disadvantage of increasing circuit size and lowering the operating frequency. This would make a power analysis attack very difficult but though in practice, uncontrolled manufacturing variations prevent the interconnects from perfectly matching each other so there will always exist some measurable variability (we will see how these variations are put to good use for PUFs in Section 5.1).

Power analysis in an attacker controlled environment, such as in the cases above, is essential for our understanding of the vulnerabilities FPGAs are exposed to. However, in order to provide some context, below is a list of some of the challenges facing an attacker targeting a modern FPGA system in practice.

- Familiarity with implementation details. Most of the FPGA attacks described in the literature use some knowledge of specific implementation details to increase the likelihood of success. This will almost universally be untrue when attacking a real system because every implementation is different. It would be interesting to how well some attacks succeed against a completely unknown cipher implementation. However, the attacker has the advantage with FPGAs (compared with ASICs) in that he has one available to create a good power consumption model.

- *Isolation of target function.* In order for the attacker to obtain a correlation with a model, the noise contributed by concurrent processes must be removed. If these operations are unknown, this will present challenges to the attacker, although noise can be statistically removed given the right model. As a designer, a somewhat costly defense would be to implement an identical cryptographic function operating in parallel with a different key to inject what is effectively random noise.

- Obtaining high signal-to-noise ratio samples. With today's FPGAs operating at over 500 MHz, the required measurement equipment is not trivial, and more advanced techniques than the traditional small resistor are required. Reducing the operating frequency may not be possible due to detection circuits, and specifically to FPGAs, their clock managers (such as a "Digital Clock Manager") set to a particular frequency range. For example, Xilinx's DCMs have two operating modes for high and low input/output frequencies, so the bottom threshold can be in the few hundred MHz (120–550 MHz, depending on multiplier setting [123, DS202, Table 50]). The attacker must also isolate the signal from the FPGA from the surrounding devices that contribute noise through the shared ground and power supply. Countermeasures may be a detection circuit for clock and temperature tampering, not allowing the attacker to tamper with the clock's frequency.

- Probe BGA packages on dense multilayer circuit boards. All high-end FPGAs with low-end ones quickly following suit have a flip-chip ball grid array (BGA) packaging, the largest having nearly 2000 balls, that physically prevent easy access to pins while the device is still soldered onto the board. BGA packages necessitate

that traces be routed inside internal layers, using blind/buried vias, which increases the entry cost for an attack. Even if the unencrypted bitstream is copied to another system for analysis, that system still needs to be developed. Relatively cheap mechanical and electrical mechanisms can be added to the printed circuit design to make an attack increasingly more expensive; for example, sensitive signals between devices can be routed in internal printed circuit layers, perhaps sandwiched between sensor mesh layers.

Finally, the attacker will need to deal with devices manufactured at 90 and 65 nm technologies, the vulnerability of which to power analysis is still to be investigated. Smartcards have a simple and standardized interface and can be isolated, making it simple to launch attacks using "kits" and readily available equipment. In contrast, each FPGA-based system interfaces with the FPGA differently and in a much more complex way. This is a major difference between smartcards and FPGAs, where the former has a simple and standardized interface. We may be able to conclude that would-be attackers must overcome considerable challenges before being able to collect power traces, and then even more trying to analyze them.

#### 3.4.2 Electromagnetic emanation analysis

This side-channel attack relies on circuits producing electromagnetic fields due to the movement of charge during the execution of internal operations. These fields can be picked up outside of the device using carefully tuned antennas, even without removing its packaging. Compromising emanations were known to military organizations since at least the 1960s, and have been used in electronic warfare since; Kuhn [62] provides the history and evolution of such attacks along with practical experiments and results from eavesdropping on computer displays.

Applying electromagnetic analysis (EMA) attacks on integrated circuits has only started to receive attention from the research community since the late 1990s. In the rump session of Eurocrypt 2000 Quisquater and Samyde introduced the terms simple and differential electromagnetic attacks, SEMA and DEMA, as the EM analysis equivalents to power consumption analysis. A paper then followed [90] describing their techniques and initial results analyzing microcontrollers. At about the same time, Gandolfi et al. [36] demonstrated EM analysis on three cryptographic implementations in microcontrollers. Their results show that if set-up correctly, EMA attacks can be more efficient and produce better signal-to-noise ratios than their power analysis counterparts. In a comprehensive analysis Agrawal et al. [3, 4] analyze smartcards and observe that there are two kinds of emanations, "direct", which are caused by current flowing along interconnects, and "unintended", caused by electrical and magnetic coupling between wires and components. The authors were able to exploit these emanations to obtain better results than their application of power analysis. There is an inherent advantage to electromagnetic attacks over power analysis in that they can be localized to a particular portion of the chip where the activity of interest takes place and can be mounted in the device's original setting.

Carlier *et al.* [19] have reported the first EM analysis of an AES implementation on a 130 nm Altera Cyclone FPGA. Their "square electromagnetic attack" is based on the square attack [23] which is more efficient than brute force for six rounds or less of AES.

This chosen plaintext attack fixes all but one byte of the input and observes the propagation of this byte's bits throughout the round functions. The authors were successful in obtaining some key bits by placing an antenna close to the FPGA and using DEMA techniques; they were also able to distinguish relevant signals from the noise produced by parallel processes.

De Mulder *et al.* [26] have reported a successful attack against a special implementation of an elliptic curve algorithm on a 220 nm Xilinx Virtex 800 FPGA. They used SEMA to observe key-dependent conditional branching, and DEMA statistical techniques against an improved algorithmic implementation. A later publication by De Mulder *et al.* [27] has more technical details on the DEMA attack. It is interesting to note that localization considerations were taken into account and that the FPGA was operating at a very low frequency of 300 kHz. As with the power analysis reports, these implementations ran in isolation, making the attack environment ideal for the attacker.

In summary, EM analysis is certainly a side-channel that can be exploited by attackers, though many of the difficulties outlined for power analysis also apply here and require further research. As Argrawal *et al.* [5] and others demonstrate, the combination of power and electromagnetic side-channel analysis may be the best way to improve results. An interesting aspect that may affect both attacks, and is yet to be explored, is the distribution of ground and power pins in the package. We discussed down-facing die in flip-chip packaging, but the arrangement of power and ground pins has also been radically changed to gain better signal integrity. Traditionally, ground pins were at the center of the package with power pins in batches around this center cluster. Package and chip designers now tend to spread power pins across the grid array, and closer to signal pins, for less inductive and shorter ground return paths. It would be interesting to see if this makes acquiring good samples, perhaps locally to where the target function is, better or worse.

#### 3.4.3 Timing analysis

Each data-processing operation takes a certain time to complete and if that operation depends on secret material such as a key, some information may leak. Conditional branching, memory access, and algorithmic operations, for example, are often key-dependent in cryptographic function implementations; analyzing their timing signatures can provide sufficient number of key bits. A common example of timing attack is when passwords are checked a character at a time, halting on the first mismatch. Noting the different processing time the attacker can determine the password in just a few attempts. Kocher [59], who introduced this class of attacks in 1996, and Dhem *et al.* [28] have shown how practical these attacks are against microcontroller implementations of cryptographic algorithms.

Observing timing variations through the power traces might not be as effective with FPGAs because unlike microcontrollers, processes run concurrently. However, timing can be observed through memory accesses and other interfaces with external devices. The designer can prevent information leaking through timing variations by making sure that sensitive operations require the same number of clock cycles to complete; by adding timing randomization to operations; or, by loading data into internal memory blocks before processing it. In general, any operation that is observable via the device's pins should be checked for timing-related leaks.

### 3.5 Ionizing radiation

Single event upsets (SEU) are "radiation-induced errors in microelectronic circuits caused when charged particles lose energy by ionizing the medium through which they pass, leaving behind a wake of electron-hole pairs" [80]. SEUs in CMOS devices are generated by atmospheric and ambient ionizing radiation consisting of neutrons, protons and heavy ions and also from alpha particles emitted from materials used for integrated circuit packaging [53, 82] [123, White Paper 208]. An SEU may cause a transient pulse called a "single transient effect" resulting in delay faults [35] and may also cause a memory bit to flip state; multi-bit upsets due to a single event are also possible with decreasing probabilities. SEU flips are called "soft errors" because they can be corrected by overwriting or power-cycling.

In FPGAs, the result of a flip in a *used* configuration cell is a change to the functionality of the device. Lesea et al. [71] provide experimental results from a long running study to validate extrapolated mean time between failure (MTBF) estimates from accelerated particle beams. This was done by placing hundreds of unconfigured FPGAs, manufactured with different technology geometries, exposed to ambient radiation at four different altitudes. The true MTBF was measured over periods of years and was determined to be higher than many previous predictions for small feature size transistors. However, the mean time between *functional* failure can be at least ten times that rate. This is because most of the FPGA's fabric is routing, and even if there is a 100% utilization of resources, only up to 10% of the whole FPGA is actually used. Of course, flipped bits in user logic, such as ROM content, may also result in faulty operation. As an adversarial tool, one can use ionizing radiation to modify the configuration of the device to disable protection mechanisms or alter memory content. This attack could be made successful by exhaustively irradiating the device until the desired results are observed; if one is able to focus the radiation and accurately apply it, once the location of the relevant registers is known, the cost of attacking other systems will be lower. However, given the amount of transistors in a device and the cost associated with precise irradiation, this attack might not be practical except to well funded outfits. We should be aware that SRAM cells for memory and FPGA configuration are of different construction than ones found in memory and ASICs. While SRAM cells are built for speed and have minimal loading, FPGA configuration memory is allowed to be slow and thus, may have larger capacitive loads, making this type of SRAM cell harder to flip [50, 71].

Measures for detection (and correction) of SEUs were introduced by FPGA vendors for high-reliability applications [7, App. Note 357] [123, App. Note 714]. These functions continuously scan the configuration cells and compare their CRC or Hamming syndrome to the original's, alerting on discrepancy. Triple modular redundancy (TMR) is another solution, where all logic is triplicated and majority voters inserted to determine logic faults due to radiation. This is used mostly in space applications where the mean time between function failure is so low that the cost is justified. Along with TMR, these applications also "scrub" the content of the FPGA every so often to restore the correct state of the cell that flipped due to SEUs. Although not originally intended as security-enhancing measures, these solutions may be used to detect radiation attacks, which may also be applied to tamper proof modules which are not built to resist them. Aside from the internal checks, readback could be used to send the read-out bitstream to an external

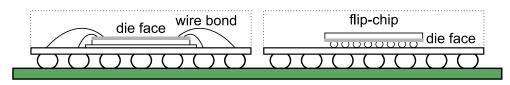

Figure 4: A wire-bond package is shown on the left where the die faces up with wires bonded connecting it to the solder balls through a substrate; in the flip-chip package on the right the doun-facing die has "bumps" used to connect it to the circuit board substrate using solder balls.

radiation hardened device to verify it using stored copy of the original. Alternatively, if the bitstream is authenticated, it could be read-back and used to reprogram the FPGA.

### 3.6 Invasive and semi-invasive attacks

Invasive attacks physically probe and alter the target device in order to extract secret information from it. The process involves de-packaging of the device and removing the passivation layer that protects the metal interconnects from oxidation. This can be done using chemicals, or for more precision, with a laser cutter that creates a hole for the insertion of probes. This requires a microprobing station that allows the attacker to accurately control the probes, position the die, and observe it with a microscope. A more sophisticated and expensive tool required for small feature size integrated circuits and higher precision is the focused ion beams (FIB) workstation. Using accelerated particle beams that interact with gases close to the die, the FIB can create incisions at the nanometer scale, deposit metal connection, and take high resolution images of the die. This can enable an attacker to either read data from buses or disable certain structures. Skorobogatov [96] details the process of invasive attacks on microcontrollers while Soden *et al.* [98] provide an excellent survey of techniques used for failure analysis by device manufactures, which are the same ones that may be used by attackers for analysis and attack.

The shrinking feature sizes<sup>5</sup>, integrated circuit complexity, and the destructive nature of invasive attacks make them very costly. Further, the advent of flip-chip packaging used for many of today's FPGAs, and shown in Figure 4, prevent easy access to the face of the die. Flip-chip packages mount the die facing down, close to the package's pins to reduce inductance and allow greater package densities, or smaller pitch. The older wire-bond packages had the die facing up and wires attached to die in order to connect to the package's pins, and thus were easier to probe. Currently, there are no published reports on a successful invasive attack against volatile FPGAs.

Semi-invasive attacks attacks require the removal of the device's packaging, leaving the passivation layer intact, while the rest of the analysis is done using techniques such as imaging and thermal analysis. This class of attacks were introduced by Skorobogatov [96] and cover the gap between the non-invasive and invasive types. Semi-invasive attacks are cheaper than invasive ones since they typically do not require expensive equipment

$<sup>^5\</sup>mathrm{In}$  2006, FPGAs manufactured in  $65\,\mathrm{nm}$  and made of 12 metal layers were introduced.

or extensive knowledge of the chip; Skorobogatov has applied these attacks on devices fabricated with 250 nm and larger manufacturing technologies. As with invasive attacks, no reports are available on successful applications of these techniques on recent FPGAs. One relevant semi-invasive techniques is data remanence: the effect resulting in the retention of evidence of previously stored state in storage media or RAM cells after they have lost power. Ionic contamination, hot-carrier effects, and electromigration can "impress" the stored state over time. Gutmann [42, 43] covers remanence of magnetic media and RAM at length. For RAM, under certain conditions, such as high voltages or lower temperatures, the previous state is available for a period of time after power is removed. Skorobogatov [97] tested eight (manufactured at 250 nm technology and larger) feature-size SRAM devices, all showing remanence of up to a few seconds at sufficiently low temperatures. No public data is available for remanence analysis of other types of cells may not apply.

Both invasive and semi-invasive techniques remain an interesting research topic that will undoubtedly yield new insights for dealing with the shrinking feature sizes of modern FPGAs and integrated circuits in general.

## 3.7 Brute force, crippling, and fault injection

In cryptography, brute force means attempting all possible key values to search for a valid output. It can also mean exhaustion of all possible logic inputs to a device in order, for example, to make a finite state machine reach an undefined state or discover the combination to enter the device's "test mode". Another form of brute force attack is the gradual variation of the voltage input and other environmental conditions, rather than variation of logic states. Brute force is sometimes associated with black-box attacks that attempt to exhaust all input combinations and record the outputs in order to reverse engineer the device's complete operation, or create a new design that mimics it. Considering the stored state, complexity, and size of current FPGAs, this type of attack is not likely to be practical or economic for reverse engineering the FPGA's whole functionality [122]. That said, if a subset of the functionality is targeted that can be interfaced with directly through the IOs, brute forcing can be fruitful, perhaps in combination with other attacks. For critical functions, therefore, randomization may be useful. Christiansen [20] suggests adding "decoy circuits" to the design to increase the effort of an attacker. The cost is high, though, seven times LUT usage and twice the power in addition to requiring more IOs and design time.

Crippling attacks either subvert a system to perform malicious functions or completely bring it off-line, similar to denial-of-service attacks on networked servers and devices. The absence of robust integrity preserving mechanisms for bitstreams, such as authentication, enables anyone to program an FPGA if they have access to it. In the case where bitstream encryption is used (see Section 4.2) confidentiality is provided, but may not be sufficient, as an adversary can still re-program the device with an invalid bitstream and bring the system off-line. An extreme scenario is described by Hadžić *et al.* [44] where an FPGA is permanently damaged due to induced contention by using invalid bitstreams. Their attack may not work in practice, however, because most systems cannot supply the necessary current for sufficiently long to damage the device, unless they are connected to a non-current-limited power supply. In any case, bitstream authentication, discussed in Section 5.2, will solve all these issues, except the one where the FPGA is left unconfigured, because it can only store a single configuration at a time. Of course, if the attacker has physical access to the system, nothing could be done to prevent denial-of-service, aside from physical measures.

Fault injection or glitch attacks attempt to force a device to execute an incorrect operation, or cause it to be left in a compromising state, or create a condition that leaks secret information. This is done by altering the input clock, or creating momentary over- or under-shoots to the supplied voltage. As an example, if a conditional branch is skipped by the CPU due to a clock glitch some commands will not be executed; a voltage surge or trough can cause registers to keep their state. If a power glitch is applied at the right time, the number of rounds of an encryption algorithm may be reduced; Anderson and Kuhn [10] demonstrate how glitches and fault injections were used to attack microcontrollers. The best defense against these attacks is making sure all states are defined and at the implementation level, verifying that glitches cannot affect the order of operations. Other defenses are clock supervisory circuits to detect glitches, and detection of voltage tampering from within the device. Some of these solutions are available, and are discussed in Section 6.3.

### 3.8 Relay and replay attacks

Relay attacks allow an adversary to impersonate a participant during an authentication protocol by extending the intended, or assumed, transmission range for which the system was designed. Relay attacks have been known since at least 1976 [22, p75] and are simple to execute as the adversary does not need to break the cryptography if it is used. A good example is a relay attack on proximity door-access cards that was demonstrated by Hancke [46]. To gain access to a locked door, the adversary simply relays the challenges from the door to an authorized card some distance away and sends the responses back. The only restriction on the attacker is that the signals arrive at the door and remote card within the allotted time, which Hancke showed to be sufficiently liberal. Another example, is the joint work of the author with Steven Murdoch [31] on relaying smartcard payment transactions to place unauthorized transactions on a victim's card. It is evident then, that despite the knowledge of such attacks we regularly see systems susceptible to them being deployed.

Consider a system where the loaded bitstream executes an authentication protocol with a chip that is placed near it on the PCB, and with which it shares a key (more about this schemes in Section 4.3). This is meant to prevent the bitstream from being used on any other system that does not have that specific authentication device on it. But if this system is cloned along with the bitstream nothing prevents the challenges to be sent to be relayed to a centralized database. This example is a bit contrived for commercial products because it is unlikely that cloners will go through the effort of implementing such relay attack, though for some systems it may be productive. In general, every security system should consider the possibility of an attacker being able to relay challenges and responses for a range beyond the one assumed, and proper timing constraints should be applied. A cryptographic solution can be in the form of distance bounding, where the FPGA can determine the distance of another device by a mutual exchange of multiple singlebit challenge-response pairs and placing an upper bound on the distance by assuming the signals traveled at the speed of light. The author and Steven Murdoch [31] have implemented a wired version of the Hancke-Kuhn distance bounding protocol [47] on an FPGA as a defense against relay attacks, being able to bound the distance between participants to below a few meters. This may be a low-cost defense against relay attacks when devices supporting the protocol, such as FPGAs, are communicating, or even used as a cheap anti-tampering defense.

Replay attacks allow the attacker to resend recorded protocol transaction data at a later time. The purpose, for example, can be to repeat a money transfer transaction or the impersonation of a participant in an authentication protocol; Syverson [107] provides a taxonomy of replay attacks. Cloning of FPGA bitstreams is the simplest replay attack. Consider the case where a critical security flaw has been found in a fielded design and a field-reconfiguration is performed with an updated bitstream. If the attacker was able to record the bitstream containing the vulnerable design, and even if it is encrypted, he would still be able to program the FPGA with it. This is possible because the FPGA cannot verify the freshness of bitstreams or provide freshness of its own to the cryptographic process because it does not preserve any state between complete configurations. One solution can be the addition of a non-volatile counter that is added to the encryption or authentication process to provide freshness; this value is called a nonce, which can be random, pseudo-random or even a predictable string, but must strictly be used only once. A more complicated solution that does not require additional FPGA features and at the expense of user logic, is for the design to send an authenticated message to a database. which attests that the operating version is up to date.

### 3.9 Social engineering

Social engineering or pretexting is the practice of manipulating people into revealing secrets through any form of human-to-human interaction; phones are mostly used because of the relative low risk and the ease in which one can pretend to be someone else. When a fraudster can hand a \$100 note to a cleaning staff member for some inside information or cleverly manipulate the CEO's secretary to email the information to him from within the company's network, the type of FPGA, cryptographic algorithm or any other technologybased defense becomes irrelevant. The attacker can also penetrate offices under the guise of a technician and install a sniffing device on the port or cable used to program FPGAs, not only getting the designs, but also the keys used to encrypt them. In general, social engineering attacks are significantly cheaper than defeating active protection mechanisms. Simply restricting access for sensitive areas of the company's network or files to particular individuals with proper credentials can help, along with a robust audit trail of access to information. Education, rather than technology, is the more effective way to minimize the damage from social engineering due to the inherent human element; Mitnick [77] details his exploits in this area and also suggests ways for companies to mitigate losses due to social-engineering. One must also consider the corrupt, disgruntled and/or underpaid employee who is seeking fame, fortune, vengeance, or all three. These can be hired by competitors and walk away with secrets in their handbag or they may install a Trojan horse, logic bomb, or a back-door in corporate files or software code. Phishing and intrusion to databases is also a concern (think about modification of the HDL of cores that are offered free to customers). Then, of course, there are the more traditional crimes of laptop theft, break-ins, remote access at conferences and so on.

The social engineering class of attacks applies to any type of information and is mentioned here for completeness as system developers must be aware of the social threats in addition to the technical ones. Measures to thwart these attacks and minimize their effect should be an integral part of every defense strategy and certainly part of the threat and cost analysis.

# 4 Defenses

In the previous section we discussed the vulnerabilities and threats to which FPGAs are prone, now we consider ways in which designers can protect their products.

## 4.1 Defense categories

The efficacy of a defense mechanism is evaluated by the cost of circumventing it; skill, tools, and time required for breaking the defense are monetized to give the analyst a metric that indicates the system's estimated level of security. Before delving into the technical discussion, let us first define defense categories:

- Social deterrents are provided by legal systems and also rely on peoples' good social conduct and aversion from being prosecuted and incarcerated. Designs can be protected by trademarks, copyrights, trade secrets, patents, contracts, licensing agreements and, of course, by the catch-all concept of "intellectual property"<sup>6</sup> (IP). However, social deterrents are only effective where appropriate laws exist and are enforced. Attitudes towards design-ownership rights vary significantly from country to country, making this type of deterrent not wholly effective in places where it matters the most: in countries where most counterfeit goods are manufactured and in which ownership rights tend not to be enforced.

- Active deterrents are physical and cryptographic mechanisms that prevent theft and misuse of designs. Active protection is highly effective if implemented correctly, and is also locale-free (assuming we ignore export restrictions laws or cryptographic devices). Further, combined with the social deterrents, active deterrents can help convince a court that the designer has taken the appropriate measures to protect the design and that the perpetrator had to actively circumvent them.

- *Reactive* deterrents provide detection or evidence of intrusion and fraud that may help in applying the social tools that are available. Digital forensics rely on these mechanisms, such as closed-circuit TV, watermarking, fingerprinting, and steganography, to initiate further investigation or improve the security of a system after an attack or intrusion. Audit trails are a reactive mechanism, and are an important

$<sup>^{6}\</sup>mathrm{This}$  term is now so loaded that it has become somewhat meaningless; in this paper, other, more descriptive terms, will be used instead.

facet of security in the absence of, or in addition to, active ones. Reactive measures do not actively prevent fraud or theft, but their presence may deter would-be attackers, and it is sometimes beneficial to advertise them.

### 4.2 Bitstream encryption

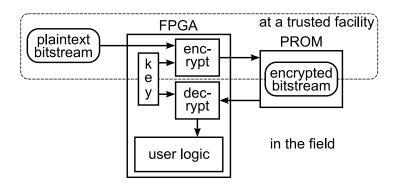

Encryption is a reversible function that provides confidentiality to data, and depends on the secrecy of a key such that even if the encryption algorithm is known, the reversal of the process to arrive at the correct original input is not possible. Encrypting the bitstream at the end of the design flow and decrypting it within the FPGA defends against cloning, reverse engineering, and in some cases, provides limited tampering protection. The basic encryption of configuration data for programmable devices was first suggested in 1992 in a patent by Austin [13]. But the first implementation was in Actel's 60RS device family, though it soon became an example-case for bad key distribution practice since they permanently embedded the same vendor-defined key inside all devices (this protected against reverse engineering rather than cloning) [54]. This meant that a single successful attack would allow decryption of all bitstreams, so the incentive to obtain the key was high — and since the key had to be present in the software, the attacker only needed to reverse engineer the code, rather than resort to invasive attacks. In 2000 Xilinx implemented a bitstream encryption mechanism in their Virtex-II family which allowed a user-defined key, though by now this functionality is common in most high-end FPGAs, and works as follows.

After the bitstream has been produced, the software requests a key from the user and encrypts the configuration payload of the bitstream. The user then "programs" this same key into the FPGA, which has a dedicated hard-wired decryptor in its configuration core. The bitstream has header information that instructs the FPGA to pass the data through the decryptor before it is sent to the configuration memory cells, as usual. An attacker who obtained the encrypted bitstream cannot use it because he does not have the key; thus, he can neither reverse engineer it or use it in another device (assuming different keys are loaded into each FPGA). Altera's Stratix II and III FPGAs also allow the designer to choose whether to force all bitstreams through the decryptor, disallowing unencrypted bitstreams. This prevents the "execution" of any bitstream not encrypted with the correct key, but does not prevent denial-of-service attack by attempting to program the FPGA with an invalid one.

#### 4.2.1 Key storage