# Wafer direct bonding: tailoring adhesion between brittle materials

Andreas Plößl<sup>\*</sup>, Gertrud Kräuter

Max-Planck-Institut für Mikrostrukturphysik, Weinberg 2, D-06120, Halle (Saale), Germany

Accepted 12 October 1998

# Abstract

It is a well-known phenomenon that two solids with sufficiently flat surfaces can stick to each other when brought into intimate contact in ambient air at room temperature. The attraction between the two bodies is primarily mediated through van der Waals forces or hydrogen bonding. Without a subsequent heating step, that type of bonding is reversible. Annealing may increase the energy of adhesion up to the cohesive strength of the materials concerned. The wafer bonding phenomena in brittle materials systems, especially in silicon, is reviewed in the experiment. The focus is on low temperature bonding techniques. The pivotal influence chemical species on the surfaces have on the subsequent type of bonding (van der Waals, hydrogen, covalent bonding, mechanical interlocking) is discussed. Methods of modifying the surface chemistry for tailoring bonding properties are addressed. The paper is aimed at providing an overview of the current understanding of the factors determining the bondability and strength of the bonding obtainable. The authors assess the present state of the experimental methods for determining basic parameters governing the adhesion. A number of examples illustrate the applicability of fusion bonding for as diverse fields as opto-electronics, microsystems technology, and fabrication of advanced substrates like silicon-on-insulator wafers. © 1999 Elsevier Science S.A. All rights reserved.

*Keywords:* Wafer bonding; Wafer direct bonding; Fusion bonding; Low-temperature bonding; Smart cut; Exfoliation; Silicon-on-insulator; Electronic properties

# 1. Introduction

What is wafer direct bonding? If two solids of the same material with clean and flat surfaces are brought into close proximity, attractive forces should pull the two bodies together into intimate contact so that bonds can form across the interface. Two crystals with matching orientation should merge into one crystal with no indication of the former junction, while two misoriented crystals would form a grain boundary at their interface. In the former case the adhesion would be equal to cohesion, in the latter case a similar value would be obtained. Everyday-experience speaks against this scenario and usually it is argued that the bodies can make contact only at some asperities, and even there surface adsorbates would prevent the formation of strong chemical bonds and themselves provide only poor adhesion. Although this interaction suffices to cause friction, it is usually incapable of holding two bodies together. In wafer direct bonding, however, exactly this occurs: two solids with well-polished flat surfaces, when brought into close proximity, spontaneously adhere or 'bond' to each other, and once initiated, the bonding will spread by itself across the whole interface. There is no gap at the interface, the two bodies are only an atomic distance apart. The bodies adhere without external force or layer of glue, giving rise to the colloquial reference to wafer direct bonding as 'gluing without glue'. Wafer direct bonding is also known as 'wafer bonding', or 'direct bonding'. Although in some cases bonding requires external pressure and

<sup>\*</sup> Corresponding author. Tel.: +49-345-5582-635; fax: +49-345-5511-233; e-mail: ploessl@mpi-halle.de

high temperature, 'fusion bonding' and 'bonding by atomic rearrangement' may be safely subsumed under wafer direct bonding. It is, however, to be distinguished from 'anodic bonding' where at elevated temperature and with an electric field applied, metals are joined with sodium-containing glass [1–3].

The adhesion depends on the type of interaction: van der Waals forces, hydrogen bonds or strong chemical bonds of metallic, ionic or covalent nature may mediate the adhesion. A discussion of forces acting at surfaces can be found, for example, in the monograph by Israelachvili and the references to earlier studies at Cambridge therein [4]. Usually in wafer direct bonding, the attraction between the two bodies primarily is seen as a result of van der Waals forces or hydrogen bonds. This type of bonding is reversible provided no subsequent heat treatment has been performed. To show that recent progress in wafer direct bonding permits attaining the full range of attractive interaction through judicious adjustment of the bonding conditions is one of the aims of the current review. Irrespective of composition or internal structure, no matter whether the material is monocrystalline, polycrystalline or amorphous, and no matter whether the material is of a single phase or a composite of several, all materials may be expected to be directly bondable to each other provided the surfaces meet the requirements in smoothness, flatness and cleanliness. In the case of malleable materials mutual conformity can be brought about by plastic deformations; here, however, the focus will be almost exclusively on the brittle materials which allow only elastic distortions.

Although perhaps unexpected from the perspective of common experience, the phenomenon of direct bonding is not new as will be shown in the brief section on its history. The requirements imposed on the surface of materials to make them directly bondable and the procedures generally practised for bonding will be listed in a separate chapter. Methods to judge the quality of bonding or to unravel the intricate interfacial chemistry will be introduced in the section on "Examination of bonding quality". The system studied best is silicon bonding, and in "Silicon direct bonding" the scope in interfacial adhesion engineering attained in recent years can be shown paradigmatically. "Other materials" treats a variety of other systems of interest, and treating an economically important combination not in a separate chapter is not to deny it its importance, it only reflects the dearth of published knowledge on the underlying bonding chemistry. "Electronic properties" deals with silicon and with III–V compound semiconductor bonding. "Examples of applications" mainly aims at giving a flavour of the variety of situations where bonding has established itself as the method of choice or where bonding has been suggested.

In view of the large number of articles published on wafer direct bonding, this review aims not to provide an exhaustive bibliography; instead the reader is referred to a dedicated issue of Philips Journal of Research [5], to topical conference proceedings [6–9], recent reviews [10–21] and to the book by Tong and Gösele on that subject [22]. The adhesion phenomenon is not always wanted. Although closely related, avoidance of bonding is not explicitly covered in the present article, as recent reviews treat stiction in microelectromechanical systems [23–26].

# 2. History of wafer bonding

Although wafer direct bonding has only recently been added to the toolbox of microelectronics and microsystem technology, the basic phenomenon has been known and used for many centuries. The developments leading to present-day wafer bonding were reviewed, for example by Gösele and Stenzel [27]; Haisma reviewed its history in the patent literature [28]. Additional information on early patents may be found for instance in Ref. [18].

Around 1230–1240 the Franciscan friar Bartholomaeus Anglicus, for instance, one of the medieval encyclopaedists digesting and compiling other sources, stressed the importance of cleanliness when joining silver and gold [29]:

Quando autem lamina vel bractea aurea cum argentea subducta debet malleando incorporari, necesse est a tribus maxime præcaueri, scil. a puluere, vento and humore, quia si aliquid horum inter aurum and argentum se permiscuerit, nequaquam vnum cum altero se tenebit, and ideo oportet vt in loco valde mundo and quieto hoc duo metalla adinuicem vniantur, quando autem modo debito sic vniuntur, inseparabilis fit vnio, ita quod ab inuicem non possunt vlterius separari.

When reasoning about the cohesion of solids, Galilei invoked a hypothetical experiment which possibly is the first discussion of the adhesion of solids with plane surfaces. He argues that two completely plane, smooth and polished plates of marble, metal or glass, one placed on top of the other, would adhere to each other if one tries to lift the upper one, whereas two plates with rough surfaces would not, and he asserts that it is the vacuum which would be created upon separation of the smooth bodies which causes the adherence between the plates and, so he concludes, the cohesion between the entities of which a solid is comprised [30].

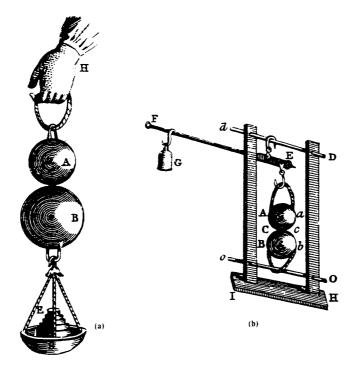

Desaguliers pressed with his hands two spheres of lead from each of which he had cut a segment of about 1/4 in. in diameter together, 'with a little Twist, to bring the flat Parts to touch' as well as he could [31]. The lead balls stuck so fast that it took approximately the same tensile stress to separate them as in the case of bulk lead [31,32]. Fig. 1 shows a demonstration of the adhesion [33]. In all those empirical examples, malleable materials were joined: only they permitted the plastic deformations necessary to bring the two bodies into intimate contact and thus to enable strong, metallic bonding. Cold welding would not work for brittle materials, the main concern of this article. The observation, reported by Desaguliers in 1734, that friction between sliding surfaces decreased with decreasing surface roughness until the surfaces became so smoothly polished that the adhesion between the bodies dramatically increased the friction [34], indicated that a better polishing technology would make brittle materials also bondable. Last century, when the emerging optical

Fig. 1. Rev. Desaguliers' demonstration before the Royal Society of the adhesion of lead joined with normal pressure and tangential force [33].

Fig. 2. Schematic set-up of Obreimoff's famous splitting experiment on mica. A wedge of thickness h was inserted to cleave off a lamella of thickness d.

industry learnt to polish glass to optical quality, duly stiction between glass pieces was observed and termed 'ansprengen' by German craftsmen [35], and in analogy, 'wringing on', 'wringing into contact' or simply 'to spring' [28,35]. Similarly, optically polished metallic precision measurement length scales known as 'end pieces' were found to adhere to each other. Often, the adherence then was just a nuisance. The phenomenon had become so commonplace that by 1930 Obreimoff started his report on the surface energy of mica with a reference to glass put in optical contact, stated that the analogue can be observed when two freshly split mica foils are put together, and then posed the question he was going to answer in the paper: whether one needs to apply the same force to split two mica sheets placed in optical contact as to split a fresh one [36]. To measure the fracture surface energy of mica, he used the arrangement schematically shown in Fig. 2. A glass wedge of thickness *h* was inserted at the bonding interface between a mica lamina of thickness *d* and the parent block of which it had been cleaved. Obreimoff found that the surface energy decreased dramatically, from 5.0 J m<sup>-2</sup> (corrected for an error in his formula) for mica split in vacuo to 0.38 J m<sup>-2</sup> for mica split in ambient atmosphere. For 'bonded' mica the surface energy approached the value of mica in air.

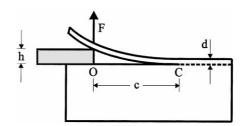

In 1936, Robert John Strutt, fourth Baron Rayleigh (1875–1947), reported probably the first thorough scientific study of room temperature adherence between glass slides [37]. Evaluating the reflective properties of the room temperature bond interface, he arrived at an average separation between the bonded glass plates of ca. 10–30 Å which did not decrease when the samples were pressed together. However, from his comparison with bonded samples annealed short of the softening point, an atomically small separation between the bonding surfaces may be inferred. The adhesion between room temperature bonded silica pieces was quantified by measurements of tensile strength and 'work of stripping' or bond energy. For the latter he developed a chevron-type double cantilever beam test, schematically shown in Fig. 3, which yielded a fracture surface energy of 71 erg cm<sup>-2</sup>, in the range of modern observations. He noted that upon re-contacting only about half

Fig. 3. Lord Raleigh's set-up for measuring the 'work of stripping'. A square piece of glass (B) was bonded under a rectangular glass piece (A) such that a corner of the square was positioned under the notch cut into the rectangle. With the aid of the hook, weights were added to induce debonding [37].

the work of stripping was recovered; the factors causing the irreversibility have not yet been analysed. His comprehensive account could have been a seminal paper on wafer bonding; however, scientifically and technologically it was rather inconsequential and not even his biographer did make much of the work's potential [38].

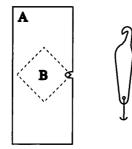

During the following decades, direct bonding found only occasional entry into the scientific literature, mostly as a specialised joining technique. At Philips Research Laboratories, He–Ne gas lasers were fabricated with the mirrors bonded to the body of fused silica [28], shown in the photograph of Fig. 4 [39]. At least for the thousands of hours of laser operation, room temperature bonding proved to form a vacuum-tight seal [40]. Antypas and Edgecombe probably were the first to utilise direct bonding as a tool for the transfer of epitaxial layers [41]. For the fabrication of a transmission photocathode, they bonded at elevated temperatures a GaAs/AlGaAs bilayer grown epitaxially on a GaAs substrate onto a glass substrate. The AlGaAs layer served as etch-stop during the chemical removal of the GaAs substrate. The epitaxial-layer-transfer concept has only recently found more wide-spread application, for instance in the form of epitaxial lift-off [42]. Together with some later work by Liau and Mull [43], the report by Antypas and Edgecombe [41] sometimes is seen as the inception of wafer bonding in the field of III–V compound semiconductors.

In spite of the long history of the direct bonding phenomenon, the modern development of the science and technology of wafer bonding only was stirred by two reports in the mid-eighties [44,45].

The driving force behind the first report was the quest for a silicon-on-insulator fabrication process yielding device layers of a quality equivalent to bulk wafers. Most electronic devices require only a small fraction of the thickness of a standard wafer. Isolating the thin device layer electrically from the mechanical support of the 'handle wafer' offers a number of advantages. Originally, the radiation hardness resulting from the greatly reduced sensitivity to electron-hole pairs generated by radiation was perceived, particularly for military applications, as the main benefit. Meanwhile, the reduction in operating voltage, the integrability of high and low voltage devices and the increased packing densities possible turned out as the advantages of commercial import. To demonstrate a novel route to such a SOI-substrate, Lasky bonded a thermally oxidised wafer to a handle wafer. Before chemically thinning the oxidised wafer to leave a thin monocrystalline layer on top of the oxide, the room temperature bond was strengthened at temperatures between 700°C and 1050°C [45].

Fig. 4. The short, stable plane-mirror He–Ne gas laser represents probably the first industrial application of direct bonding [28]. The reflecting mirrors and the body of fused silica were 'wrung together' [39].

In the second report, Shimbo et al. tried to substitute deep dopant diffusion and the growth of thick epitaxial layers in the processing of devices by a wafer bonding step. Wafers covered with a native oxide were contacted at room temperature; the thus bonded pair was annealed at 1000–1100°C to induce covalent bonding and to dissolve the oxide interlayer [44].

Finally, wafer bonding was seen as a solution to a variety of problems in microelectronics and microsystems technologies, and thus the reports could spark a new field in materials science and revitalise an old joining technique.

# 3. Bonding requirements and procedure

## 3.1. Introduction

Wafer bonding puts very high demands on the surfaces to be mated with regard to their flatness, smoothness as well as their cleanliness. In this chapter the requirements which have to be fulfilled to ensure a high bonding yield will be discussed.

Wafer bonding requires surfaces free of contaminants. The contamination which play an important role in wafer bonding can be classified as (a) particle contamination (like dust, hair, fibres), (b) organic contamination (hydrocarbons from the air, plasticisers from wafer boxes) and (c) ionic contamination (metal ions from metal tweezers or glass containers).

Of all these sources of contamination, particles present on the wafer surface before bonding pose the most obvious problem in wafer bonding. Because they act as spacers, particles inhibit the interaction between opposing surface species. As a consequence unbonded areas result which are often many times larger than the particle itself. A particle with a diameter of 1 µm trapped in the interface between two standard 100 mm wafers may lead to an unbonded area with a diameter of 1 cm. Organic contaminants usually do not lead to unbonded areas during room temperature bonding because they are present on the surface as single molecules or as a film and thus do not greatly affect the surface roughness. The contamination film, however, adheres only weakly to the substrate and therefore may limit the adhesion ultimately achievable. In addition organic contaminants are thought to be responsible for the nucleation of interface bubbles during annealing. Like organic contaminants do not affect the adhesion. Depending on the application trace metal contamination may not present problems at all. However, for electronic applications they may be harmful since they can affect the electronic properties of the semiconductor material.

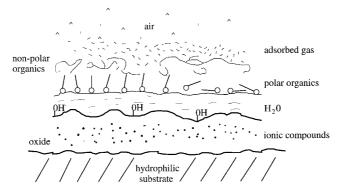

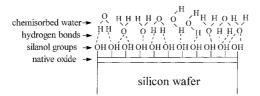

Fig. 5 schematically illustrates the adsorbate layers commonly found on a hydrophilic substrate surface.

## 3.2. Cleaning of silicon surfaces

To obtain high quality interfaces it is important to remove all these sources of contamination before bonding. Fortunately, the cleaning procedures commonly used in semiconductor industry are fully compatible with wafer bonding. They are able to remove the surface contamination without degrading the wafer surface. In the following we will limit the discussion of cleaning procedures to silicon surfaces.

When bonding other materials cleaning methods compatible with these materials have to be adopted, always keeping in mind that contaminants have to be removed without degrading the surface.

Fig. 5. Schematic illustration of the adsorbate layers commonly expected on hydrophilic surfaces.

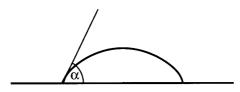

Frequently used in semiconductor processing of silicon as well as in wafer bonding is the hydrogen peroxide based RCA wet cleaning procedure. It basically involves two steps: RCA 1 (NH<sub>4</sub>OH/H<sub>2</sub>O<sub>2</sub>/H<sub>2</sub>O = 1 : 1 : 5; also referred to as SC 1 or SE 1) and RCA 2 (HCl/H<sub>2</sub>O<sub>2</sub>/H<sub>2</sub>O = 1 : 1 : 6; also referred to as SC 2 or SE 2) [46]. Other cleaning procedures commonly employed are a mixture of hydrogen peroxide and sulphuric acid (1 : 4 or 1 : 2) or concentrated nitric acid [46]. It has been reported that a mixture of H<sub>2</sub>SO<sub>4</sub> and H<sub>2</sub>O<sub>2</sub> combined with a small amount of hydrofluoric acid leads to a very thin and smooth native oxide layer useful for wafer bonding [47]. The hydrophilicity of wafer surfaces which underwent different pre-treatments as well as the long-term stability of a clean surface have been investigated by contact angle measurements [48,49]. For the removal of hydrocarbons from the silicon wafer surface a treatment with periodic acid dihydrate (HIO<sub>4</sub>·2H<sub>2</sub>O) has been recommended [50].

Since the native oxide can act as a trap for metallic and organic contamination it is frequently removed from the wafer by a dip in diluted hydrofluoric acid or buffered ammonium fluoride solution. Afterwards, the wafer is treated with one of the cleaning solutions mentioned above to form a new, clean native oxide on the wafer surface. Care has to be taken as ammonia (present in RCA 1) attacks bare silicon thereby increasing the microroughness considerably [51]. To prevent this from happening, it has been suggested to decrease the ratio of  $NH_4OH$  in the RCA 1 mixture to 0.05–0.25 if bare silicon surfaces are present. Besides the wet cleaning technology which is still the working horse in semiconductor cleaning, there is a growing interest in dry wafer cleaning methods. Dry cleaning procedures commonly employed before the bonding include UV/ozone cleaning [46,52] as well as various plasma treatments [46,48].

Due to the aggressive nature of the agents used in wet cleaning and unsolved problems regarding their disposal it is likely that in the future dry cleaning methods will become increasingly important also in wafer bonding technology.

For the bonding of hydrophobic silicon surfaces the wafers are first cleaned using the wet or dry cleaning methods mentioned above. Afterwards the oxide is etched away in hydrogen fluoride or ammonium fluoride solution. Care has to be taken since hydrophobic silicon surfaces tend to get contaminated by organic compounds even more readily than hydrophilic surfaces [53].

#### 3.3. Flatness and smoothness

The surface flatness is a macroscopic measure which is defined as the deviation of the front wafer surface from a specified reference plane while the back wafer surface is considered being ideally flat. Typically the total thickness variation (TTV) is used to quantify the flatness of a wafer. It

is defined as the difference between the highest and lowest elevation of the top surface of the wafer. During the bonding at room temperature each wafer has to be deformed in order to achieve conformity [54]. X-ray topography (XRT) can be used to image the strain pattern which relate to the flatness nonuniformity of the bonded wafers (see also chapter 4). The strain contrast in XRT-images of room temperature bonded samples do not differ from the contrast found for wafers bonded at elevated temperature. This indicates that most of the deformation occurs already at the room temperature bonding step. Maszara et al. estimated the local stress caused when wafers elastically deform on the mutual surface adaptation [54].

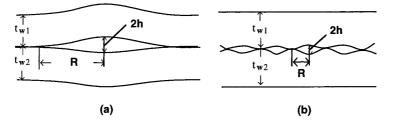

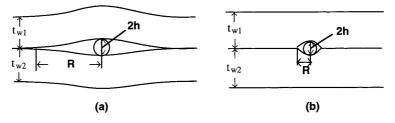

Two sufficiently smooth wafers will spontaneously bond at room temperature despite a flatness variation of a few micrometres. However, if the flatness variations are too large, unbonded areas result. Gösele et al. have theoretically investigated the conditions under which a gap which separates two wafers will prevent bonding [17,55–57]. Recently, a more comprehensive analysis has been undertaken which essentially bears out the previous results [58]. If the gaps are caused by flatness non-uniformities with the lateral extension *R* much larger than the gap height *h* the condition for a closing of the gap depends on the ratio of *R* to the wafer thickness  $t_w$ . For  $R > 2t_w$  (Fig. 6(a)) the gap will close if:

$$h < \frac{R^2}{\sqrt{\frac{2}{3}\frac{E't_w^3}{\gamma}}},\tag{1}$$

with  $E' = E/(1 - \nu^2)$ , E being Young's modulus,  $\nu$  Poisson's ratio, and  $\gamma$  the surface energy. In cases where  $R < 2t_w$  (Fig. 6(b)) the condition for gap closing is independent of the wafer thickness and is given by

$$h < 3.6(R\gamma/E')^{1/2}.$$

(2)

When bonding wafers of different thickness the equations become more complex [17,56]. In general, the thinner wafer determines the bonding behaviour (for equal *E*). Fig. 7 shows the region of gap closing for two silicon wafers of equal thickness for  $\gamma = 100 \text{ mJ m}^{-2}$ . These theoretical considerations indicate that even pieces with infinite thickness can be bonded provided that they possess the required flatness [57,59]. For silicon pieces thicker than about 3 mm the conventional semiconductor polishing method does not produce the necessary flatness anymore. For such materials optical polishing has to be applied [57,59]. Two 20 mm thick silicon pieces bond to each other after being optically polished down to a surface flatness variation of a 10th of a wavelength (about 63 nm) [57].

Commercially available prime grade 4 in. silicon wafers of the usual thickness (0.5 mm) exhibit a flatness variation of  $1-3 \,\mu$ m. Variations of this order can be easily accommodated through mutual deformation of the wafers. Bow and warpage up to 25  $\mu$ m pose no obstacle to bonding.

Fig. 6. Schematic drawing of a gap caused by flatness non-uniformities [17,56]: (a)  $R > 2t_w$ ; (b)  $R < 2t_w$ .

Fig. 7. Parameter combinations of gap height *h* and lateral extension *R* of gaps which can be closed for silicon wafers with a thickness of 525  $\mu$ m and a surface energy of 100 mJ m<sup>-2</sup>. The area in which a closing of the gap can occur is shaded [17,56].

Besides the flatness of a surface, its smoothness usually quantified as microroughness, is crucial for wafer bonding. The microroughness is a local microscopic parameter relating to the wafer surface roughness in very small wavelengths. If the microroughness exceeds a critical value the wafers are not bondable anymore. A model which describes the relation between bondability and surface morphology has been derived by Gui et al. [60]. They consider the elastic contact between a nominally flat, but rough surface and a nominally flat smooth surface. The roughness of the former is caused by a random series of asperities with spherical caps with an constant radius  $\beta$  and a Gaussian height distribution. The adhesion parameter  $1/\Delta_c$  which is defined as the ratio of the standard deviation of the distribution of asperity heights  $\sigma$  to the extension which an asperity can sustain before the adhesion is lost has been derived by Fuller and Tabor [61]:

$$\frac{1}{\Delta_{\rm c}} = 0.513 \frac{\sigma}{\beta^{1/3}} \left\{ \frac{K_{\rm E}}{\Delta\gamma} \right\}^{\frac{2}{3}}.$$

(3)

$K_{\rm E}$  is the elastic constant which is defined by the following formula:

$$K_{\rm E} = \frac{4}{3} \left\{ \frac{1 - \nu_1^2}{E_1} + \frac{1 - \nu_2^2}{E_2} \right\}^{-1},\tag{4}$$

where  $\nu_1$  and  $\nu_2$  are the Poisson's ratios and  $E_1$  and  $E_2$  Young's moduli of the two materials. Fuller and Tabor have derived the relation between the relative pull-off force of the contacted interface and adhesion parameters [61]. If  $1/\Delta_c > 3$  no force is needed to separate the materials. For known material properties and surface adhesion force the surface roughness at which bonding will become impossible can be calculated. For hydrophilic silicon wafers with  $\gamma = 100 \text{ mJ m}^{-2}$  and a mean radius of the surface asperities of 100 µm bonding would occur if the standard deviation of the asperity heights is less than 2 nm.

In practice hydrophilic silicon wafers will bond spontaneously to each other via hydrogen bonds if the microroughness characterised by a value such as root mean square (rms) roughness is less than 0.5 nm. Commercially available prime grade polished silicon wafers exhibit a rms roughness in the

Ångstrom range. Unstructured silicon wafers with standard thickness thus are bondable without any problems. The low rms roughness of silicon wafers are without any doubt related to the ever improved polishing techniques developed in the last decades. The last and most important step in the polishing of wafers in terms of surface smoothness is the chemo-mechanical polishing (CMP). It is this final polishing step which produces extremely smooth surfaces crucial for void-free wafer bonding [62]. Besides being used as final step in the production of prime grade silicon wafers, CMP can be employed for preconditioning of surfaces. It is applied just prior to using the wafers and activates the wafer surface by removing the uppermost few nanometres of the material. CMP preconditioning yields an activated surface free of contamination [62]. Finally CMP is used to planarise patterned or structured wafers before a wafer bonding step. Particularly when fabricating micromechanical devices a final CMP step may be necessary before bonding the patterned and structured wafers. The deposition of a thin CVD oxide followed by CMP has been used to form a flat layer on the surface of a processed VLSI bulk silicon wafer. The patterned substrates which were not bondable due to a lack in surface quality were first planarised by depositing an oxide via plasma enhanced chemical vapour deposition utilising tetraethoxy silane (TEOS) as precursor. The surfaces produced subsequently underwent CMP yielding rms roughness of less than 0.5 nm [63]. Spontaneous bonding was observed upon contact with bare silicon wafers.

High quality surfaces suitable for direct bonding also have been achieved via CMP of polycrystalline silicon [60,64], silicon dioxide [60,62] and silicon nitride [60,65,66].

# 3.4. The bonding procedure

To minimise re-contamination of the wafer surfaces bonding should be conducted directly after cleaning. A clean environment is absolutely necessary to ensure a high bonding yield. Thus, bonding is usually carried out in a high quality cleanroom. Typically a class 10, or better class 1, cleanroom is chosen for bonding. However, even in this clean environment bubbles caused by particulates may be detected. Furthermore, as cleanroom atmospheres are usually places of high hydrocarbon concentrations organic compounds may readily adsorb onto the clean surfaces.

The bonding is carried out either manually or by making use of a commercial bonder. The latter is particularly useful if the wafers have to be aligned before bonding. The room temperature bonding step may be carried out in air or in a different atmosphere such as oxygen, nitrogen or argon. Besides bonding under normal pressure, the bonding under reduced pressure has attracted interest. It offers certain advantages which will be discussed in chapter 5. The bonding at room temperature usually is reversible (with the exception of UHV-bonding, chapter 5).

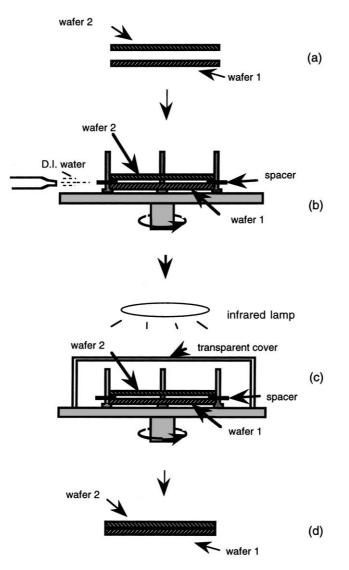

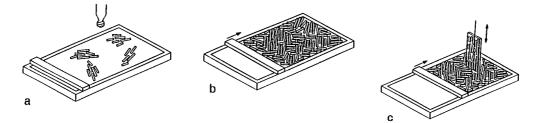

For research purposes and low budget production a bonding apparatus which can be used outside a cleanroom facility has been developed [67,68]. This so-called micro-cleanroom is based on the spin-coater concept with some additional features (Fig. 8). After wet or dry cleaning, two wafers are placed in the micro-cleanroom so that the mirror-polished sides face each other. They are separated from each other by removable spacers. The space between the two wafers is then thoroughly flushed with particle-free, deionised water. After the rinsing a lid is put over the wafers and they are spin-dried. The drying can be enhanced by heating the wafers using an IR lamp. Finally, the spacers are removed without opening the lid. The upper wafer drops onto the lower one. If the bonding is carried out in air the wafers usually float on each other due to a thin air cushion between them. By locally pressing them gently together so as to squeeze out the air bonding is initiated. The bonding then propagates by itself. In general, the bonding should be started at only one location since an initiation of the bonding simultaneously on different locations may cause the trapping of air bubbles.

Fig. 8. Schematic drawing of the micro-cleanroom [67,68].

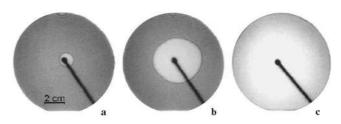

Within a few seconds the bonded area spreads over the entire wafer surface, particularly when bonding hydrophilic silicon surfaces. The bonding between two hydrophilic 4 in. Si wafers as observed with an IR camera is shown in a sequence of photographs in Fig. 9. The velocity of the contact wave has been studied. Stengl et al. [69] have investigated the bonding velocity of hydrophilic silicon surfaces as a function of temperature. They report a decrease in bonding speed with increasing temperature reaching zero at about 200°C. This behaviour is attributed to the enhanced desorption of water molecules at elevated temperature which are involved in the formation of hydrogen bonds across the interface. Haisma et al. reported an increase in bonding velocity with an increasing pH of the solutions used for surface energy [16]. However, Cha showed that wafers covered with a thin film of protein molecules exhibit an exceedingly low bonding speed while at the same time the fracture surface energy is in the range expected for van der Waals interaction [70]. This indicates that a low bonding velocity does not necessarily relate to a low fracture surface

Fig. 9. Sequence of photographs taken with an infrared-sensitive camera, showing the propagation of the bonded area.

energy. Bengston et al. investigated the dependence of the bonding velocity on the wafer thickness [71]. Thicker wafers are less deformable and thus the bonded area spreads slower when thicker wafers are involved [71]. However, when using wafers of identical surface quality, no dependence on thickness could be observed. Instead the contact wave velocity was found to depend on the gas pressure in the interface [72]. The authors carry out bonding experiments at ambient pressure and under reduced pressure. The bonding velocity increases with decreasing pressure. The authors conclude that the bonding speed is determined by pressing the gas out of a localised area just in front of the propagating bonding front [72].

Bonding has also been carried out by contacting the wafers under ultra-pure water leaving a water film which is much thicker than the commonly observed few monolayers of water in the interface [73–75]. If the wafer pair is stored at slightly elevated temperatures under vacuum the water slowly diffuses laterally out of the interface.

# 3.5. Interface bubbles

One problem frequently associated with wafer bonding is the formation of interface bubbles, sometimes referred to as voids. In principle there are two different kind of interface bubbles: (a) bubbles which occur in the as-bonded interface at room temperature and (b) bubbles which are generated at elevated temperatures (typically at  $200-800^{\circ}$ C).

The first type is usually caused by surface irregularities, particulates or trapped air. Trapped air can be avoided by initiating the bonding in the centre of the wafer pair or bonding in vacuo. Particles cause unbonded areas as they prevent the wafers from making close contact. The wafers are deformed around the particle upon bonding. The resulting bubbles or circular unbonded interface areas are quite large compared to the actual size of the particle. Tong et al. have investigated the bubble diameter as a function of the size of a particle trapped between two wafers [17,56].

In Fig. 10 the deformation caused by a particle trapped in the interface in shown schematically. In Fig. 10(a) the radius h (or height H = 2h) of the particle is much smaller than the radius R of the unbonded area resulting and much smaller than the wafer thickness  $t_{w}$ . Using the simple theory of

Fig. 10. Schematic drawing of a particle leading to an unbonded area [17,56]. (a) Unbonded area with a radius R larger than the wafer thickness  $t_{w}$ ; (b) with a radius, R, smaller than the wafer thickness,  $t_{w}$ .

small elastic deflection of a thin plate, R can be calculated from Eq. (5) by assuming that the particle is incompressible [17,56]:

$$R = \left[2/3E't_{\rm w}^3/\gamma\right]^{1/4}h^{1/2} \tag{5}$$

( $\gamma$  = surface energy of each wafer when partially debonded,  $E' = E/(1 - \nu^2)$  with E denoting Young's modulus and  $\nu$  Poisson's ratio).

For two wafers of different thickness more complex equations result [17,56].

It can be easily derived from Eq. (5) that even a relatively small particle will result into a large unbonded area. For example a particle of diameter  $0.5 \,\mu\text{m}$  trapped between two 4 in. silicon wafers each with a thickness of 525  $\mu\text{m}$  will yield an unbonded area of approximately 0.5 cm radius. Since compared to thick wafers thinner wafers are more easily deformable a reduction in wafer thickness leads to a considerable decrease of unbonded area. Moreover, for very small particles with a radius below a critical radius  $h_{\text{crit}}$  given by

$$h_{\rm crit} = 5(t_{\rm w}\gamma/E')^{1/2},$$

(6)

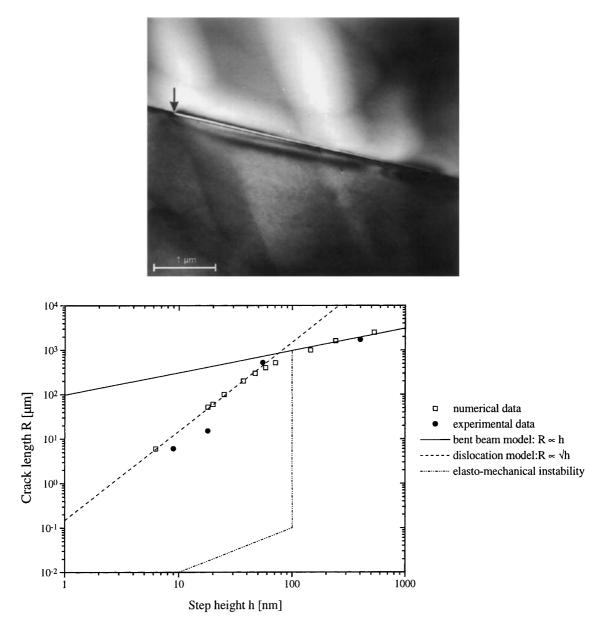

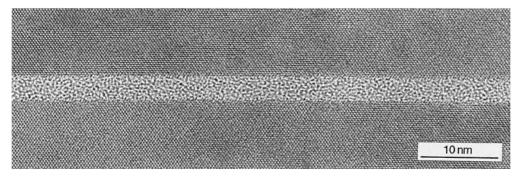

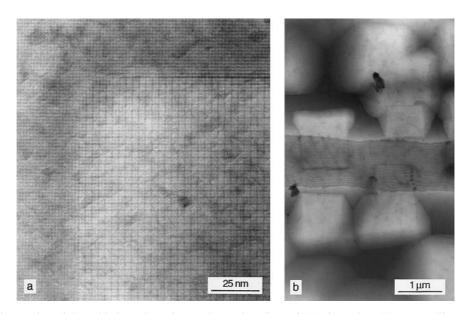

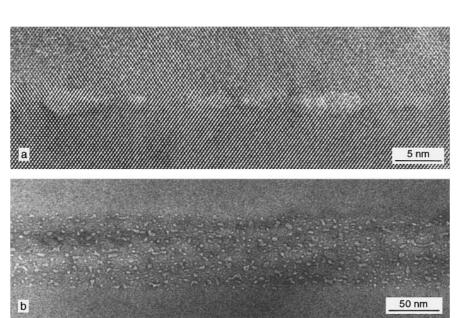

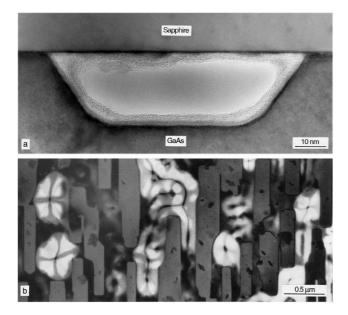

the resulting unbonded area is very small (Fig. 10(b)). This behaviour is thought to be due to an elasto-mechanical instability occurring under these conditions [17,56]. For a 4 in. silicon wafer pair a critical height,  $h_{crit}$ , in the order of 100 nm was anticipated, i.e. a particle of this size trapped in the interface would cause an unbonded area only with a radius in the same order (100 nm). For a study of the crack length as a function of asperity height, a wafer with photolithographically defined steps of down to 9 nm height was bonded against a plane wafer and subsequently examined using high-voltage electron microscopy [76,77]. Fig. 11(a) shows the long crack in the wake of a 18 nm step. The presently available results of step-structures (Fig. 11(b)) cannot validate the elasto-mechanical instability which had been hypothesised in Refs. [17,56] for the case of spherical particles.

In conclusion, bubbles or unbonded areas in the interface of as-bonded wafers at room temperature can be avoided by:

- bonding sufficiently flat wafers,

- joining clean surfaces in a particle-free environment,

- avoiding the trapping of air.

In addition to the bubbles which are observed at room temperature, unbonded areas may be generated during storage or annealing. In the interface of hydrophilic silicon pairs the bubbles are formed at temperatures as low as room temperature upon storage for an extended period of time [78]. In contrast hydrophobic silicon pairs reportedly did not show any interface bubbles upon storage for up to 113 h at 220°C [78]. However, the formation of bubbles is observed during annealing at 300°C. In general, the interface bubbles vanish when the bonded wafer pairs are heated to temperatures above 1000°C. The formation of interface bubbles upon annealing was first reported by Shimbo [44] and Ohashi [79]. The bubbles were thought to be related to interfacial water [44,69,80]. However, no correlation was found between the amount of water in the interface and the tendency for bubble formation [81]. Even in the interface of hydrophobic silicon wafers, in which there is no water present, a large number of interface bubbles may be detected upon annealing. Mitani et al. suggested that the presence of hydrocarbons in the interface contributes to the formation of interface bubbles [81,82]. A thermodynamic model for the formation of interface bubbles has been presented [82]. The authors suggest that small hydrocarbon molecules are desorbed which are mobile at the interface of the bonded wafer pair. If the vapour pressure which they generate exceeds the energy of adhesion

Fig. 11. Investigation of crack length as a function of step height [77]. (a) The high-voltage transmission electron micrograph shows the long crack in the wake of the 18 nm step (marked with an arrow). (Figure reproduced with kind permission of the authors) (b) Comparison of theoretically predicted and experimentally observed crack lengths as a function of step height. The numerical data were calculated employing the boundary element method. The expected elastomechanical instability [17,56] is indicated (data taken from [76]).

interface bubbles are nucleated. The bubbles grow by incorporating hydrogen molecules which diffuse along the interface [82].

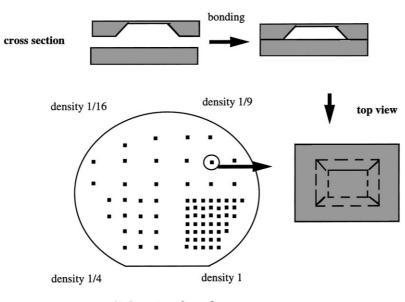

To study the formation of temperature-dependent interface bubbles and the chemical composition of the trapped gases arrays of cavities of the same size but with different areal densities were produced on a silicon wafer by anisotropic etching [83]. The test structure with the arrays of cavities is depicted in Fig. 12. At the bottom of each cavity only a thin membrane

cavity layout on the wafer

Fig. 12. Cavity structure: Test-wafer layout using various densities of cavities [83].

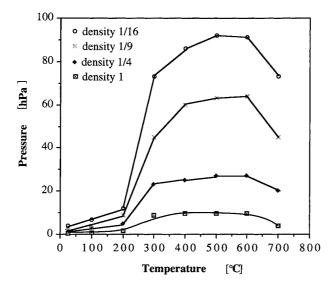

remained. The expansion of the membrane is related to the pressure formed in the cavity. The structured wafer was bonded to a bare silicon wafer, with either hydrophilic or hydrophobic surfaces under high vacuum. Upon heating the pressure inside the cavities increases. The increase in pressure was measured as a function of cavity density, time and temperature applied. The results of this experiment are shown in Fig. 13. A higher pressure is observed in the cavities with a lower areal density. This can be explained by the larger bonding area around these cavities compared to the bonding area around the cavities with a higher areal density. The gasses trapped in the cavities have

Fig. 13. Pressure increase measured in cavities of bonded hydrophilic silicon wafers as a function of annealing temperature and areal density of the cavities (annealing time: 70*h*) [433].

been characterised by mass spectrometry [84]. The main content of the gas mixture trapped in both hydrophilic as well as hydrophobic silicon wafer pairs at a temperature range from room temperature to 700°C was identified as hydrogen. Minor amounts of water, hydrocarbons and nitrogen have also been found [84]. These results indicate that at temperatures below 500°C hydrogen molecules diffuse along the interface until they find a cavity or form an interface bubble around a nucleus. Only above about 500°C an appreciable amount of hydrogen diffuses into bulk silicon.

In hydrophilic silicon wafer bonding hydrogen is formed by the reaction between bulk silicon and water (Eq. (7)):

$$\mathrm{Si} + 2\mathrm{H}_2\mathrm{O} \to \mathrm{SiO}_2 + 2\mathrm{H}_2. \tag{7}$$

The water for this reaction originates from the few monolayers of water which are present on a hydrophilic silicon surface. Additional water is formed during the condensation reaction between silanol groups (Eq. (8)):

$$- \overset{i}{\text{Si}} - OH + OH - \overset{i}{\text{Si}} - - \overset{i}{\text{Si}} - O - \overset{i}{\text{Si}} - + H_2O$$

(8)

The water diffuses to the bulk silicon where it reacts according to Eq. (7).

The hydrogen in the interface of hydrophobic silicon wafers is formed by the desorption of hydrogen atoms which terminate the surface of hydrophobic silicon wafers (Eq. (9)):

$$-\overset{i}{\operatorname{Si}}-\overset{i}{\operatorname{H}} + \overset{i}{\operatorname{H}}-\overset{i}{\operatorname{Si}}-\overset{-}{\operatorname{Si}}-\overset{i}{\operatorname{Si}}-\overset{i}{\operatorname{Si}}-\overset{i}{\operatorname{H}}+ \overset{i}{\operatorname{H}}_{2}$$

(9)

The results of the experiment described above clearly indicate that interface bubbles formed upon annealing are caused by hydrogen. However, for interface bubbles to form the presence of hydrogen alone was found insufficient; hydrocarbons as nucleation centres are also necessary [81]. Taking this in account methods can be devised to prevent the formation of interface bubbles. One step towards the prevention of interface bubbles would be the removal of any thermally unstable organic contamination prior to bonding. Mitani et al. could show that hydrophilic silicon wafers which have been exposed to oxygen or argon at elevated temperature prior to bonding do not form any interface bubbles after bonding and subsequent annealing [81]. A simpler approach to bonding without the occurrence of temperature-dependent interface bubbles is the treatment of hydrophilic silicon surfaces with the dihydrate of periodic acid (HIO<sub>4</sub>·2H<sub>2</sub>O), a strong oxidising agent [50]. Both procedures remove organic contamination effectively. As a consequence no interface bubbles are generated upon annealing, even though plenty of water and, after annealing, subsequently hydrogen (Eq. (7)) is present in the interface. Interface bubbles can also be avoided by bonding wafers which are covered with a thermal oxide. The open structure of the thermal oxide is said to allow the hydrogen as well as the volatile organic contaminants to diffuse into the oxide, thereby greatly reducing the gas pressure at the interface [80].

# 4. Examination of bonding quality

## 4.1. Introduction

There is a variety of parameters which characterise a bond interface. The relevance of specific properties of the interface depends on the application in mind. For each property, a particular

experiment may be regarded as particularly suitable. It cannot be the intention to list here all the methods applicable to wafer-bonding-related questions. Here only those methods will be summarised which have been most prominent in wafer bonding research.

Frequently, in wafer bonding one is concerned with the question of how well two wafers actually are bonded. The quality of the bonding is determined by the fraction of the interfacial area being in intimate contact and the strength of the bond interaction.

First some methods are to be presented with which areas of bonding can be distinguished from unbonded areas.

# 4.2. Detection of unbonded areas

After having bonded two wafers one usually would like to know whether intimate contact was established across the whole boundary area or, to put it differently, whether there are any 'voids', 'interface bubbles' or 'delaminations', 'debonds' or 'disbonds' as the unbonded areas generally are referred to. In the evaluation of adhesive bonds, 'void' often means a space in the joint which is free of the adhesive material, whereas 'delamination' refers to a separation between a bonding partner on the one side and the adhesive material attached to the other bonding partner on the other side. As in wafer direct bonding the very surface of the bonding partners must be regarded as the adhesive material, this distinction is impractical and the terms often are used synonymously. Depending on their origin, voids may be present immediately after contacting the wafers or only after some storage or annealing time. Uneven surfaces, particles on the surfaces, or pockets of gases trapped by the advancing bonding front can cause voids from the beginning [85]. The mechanisms for the generation of voids with time has not been unravelled in detail. However, it is generally agreed upon that the voids are caused by local accumulation of gases. The gas in the voids can stem from (1) outgassing from the materials to be bonded, (2) from gas entrapped during bonding, (3) thermal decomposition of surface contaminants like hydrocarbons or (4) chemical reactions at the bond interface. In the case of hydrophilic silicon bonding, the formation of water during the silanol condensation or the formation of hydrogen during the oxidation of silicon in the reaction with interfacial water would be examples for the latter cause.

Whether voids of a given size are permissible or not depends on the particular application in mind. If one of the bonded wafers needs to be thinned down to a small thickness, even small delaminations can endanger the integrity of the film. Debonded areas in a loaded bond may accelerate failure.

There are destructive and non-destructive techniques for the detection of interfacial voids. The suitability of a given method depends among other considerations on the size of the bubbles to be detected, the properties of the bonding materials, the stability of the bond interface, the speed and ease of use. The more common techniques only will be listed here. In general, the non-destructive detection of voids is not a difficult analysis problem, unlike the quantitative evaluation of the strength of adhesion.

## 4.2.1. Optical transmission

The most popular technique to detect areas where intimate contact is lacking is based on the interference of light reflected at internal surfaces [12]. Those Newton's rings delineate the shape of the delamination. Simultaneously, the bright and dark rings of equal optical thickness permit determining how far the surfaces are separated from each other [86].

In the case of at least one optically transparent bonding partner, like glass, quartz, sapphire or gallium phosphide, voids can be observed with the unarmed eye. For materials with lower band gaps

infrared light for illumination and an infrared sensitive camera for viewing are required. Often, the bonded pair is examined in transmission but a reflexion set-up can be of advantage when one of the bonding partners is opaque, for example, like heavily doped silicon. For routine inspection of silicon bonding, a tungsten halogen lamp as light source and a silicon CCD camera whose IR blocking filter has been removed are sufficient.

The method's appeal for global surveying rests mainly with its real-time and non-destructive nature. To detect voids, the surfaces must be separated by at least a quarter of the probing wavelength. The lateral resolution typically is quoted to be 1 mm [12].

Infrared microscopy can be used to enhance the lateral resolution. Khánh et al. reported on a scanning infrared microscopy method utilising light scattered at inhomogeneities [87]. They demonstrated a resolution of about  $1-2 \mu m$ . Light scattering topography has also been used to detect voids in a fast and non-destructive manner [88].

## 4.2.2. Scanning acoustic microscopy

Next to the interference of light at internal surfaces, scanning acoustic microscopy is the most widespread non-destructive technique to detect delaminations. In acoustic microscopy, mechanical waves are used for probing a sample. A variety of configurations have been demonstrated; for a review, see for example [89].

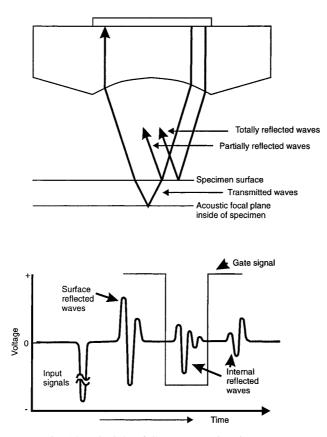

In wafer bonding, a reflexion mode scanning acoustic microscope is commonly employed. In this so-called C-scan mode, an acoustic transducer generates an acoustic pulse which a lens focuses to a diffraction-limited spot. Typically, the transducers operate at a frequency in the range between 10 and 100 MHz. After the emission of the probing signal, the transducer is switched into detection mode and receives the incoming echoes. The amplitude or the phase of the incoming echo are detected. Through gating, an echo coming from a particular depth can be selected, and by scanning the transducer relative to the sample an acoustic image of that plane in the sample is gathered. Fig. 14 schematically shows an oscilloscope trace of an incoming echo, a so-called A-scan. At the interface between the solid and the void the mechanical waves are reflected almost completely, giving the technique a very high sensitivity even for minor gaps of some 10 nm separation. On the other hand, the large impedance mismatch between solids and air makes it a necessity to use a coupling fluid to effectively transmit the ultrasound pulses from the transducer to the sample and back. Often water is being used. The need for a couplant can limit the non-destructiveness of the method. In the case of weakly bonded specimens, for instance silicon wafers bonded at room temperature in air, the coupling agent way diffuse into the bonding seam, thus causing delamination.

The lateral resolution of acoustic microscopy depends on the frequency used and the materials under investigation. For a 400 MHz transducer, the lateral resolution reportedly lies around  $4 \mu m$ , and around  $8 \mu m$  for a 200 MHz transducer; the vertical resolution was found to be better than 50 nm [90].

The useful depth range of the technique is limited on the top surface by a dead zone where the large echoes from the couplant/sample interface mask the echoes from the near surface region and in the depth of a sample by the attenuation of the acoustic pulses.

Other variants of acoustic microscopy can be used. In particular, there is some interest in extending acoustic techniques to a quantification of the strength of the adhesion in bonded areas, as mentioned below.

## 4.2.3. X-ray diffraction topography

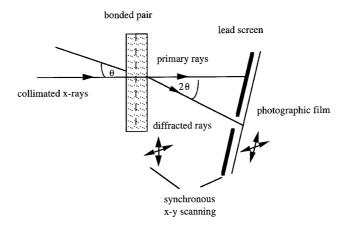

When smaller voids are to be detected, X-ray diffraction topography [91] can be used, provided the sample is monocrystalline. In X-ray topography, local changes in spacing or orientation of lattice

Fig. 14. Principle of C-scan acoustic microscopy.

planes in the investigated sample cause local variations in diffracted X-ray intensities which then are represented in a two-dimensional image. Therefore, at least one of the bonding partners needs to be a single crystal.

The bonded pair is aligned to meet the Bragg's condition  $n\lambda = 2d \sin\theta$  (where  $\lambda$  is the X-ray wavelength, *d* the spacing of the diffracting planes,  $\theta$  the angle between the incident beam and diffracting planes and *n* the order of the diffraction), and while the sample is illuminated with a collimated beam of monochromatic X-rays, the ensemble of sample and X-ray recording film is scanned in front of the beam (Fig. 15). The elastic distortions in the wake of a void cause topographic contrast and thus reveal the presence of a bubble.

In the absence of suitable X-ray lenses, there is no magnification involved in X-ray topography. The spatial resolution essentially is limited by the resolution of the detector, for X-ray film this amounts to ca. 1  $\mu$ m. Because of the need for scanning and the low X-ray intensities, long exposure times are necessary, making the technique time-consuming and expensive. As an example, an X-ray topogram of a 100 mm wafer usually takes several hours.

For the investigation of bonded wafers, X-ray topography may be used in transmission or in reflexion [10,92,93].

Of the common non-destructive void detection techniques discussed in this article, X-ray topography probably is the most sensitive technique; however, the equipment is not routinely available and the method is time-consuming and expensive.

Fig. 15. Principle of X-ray topography.

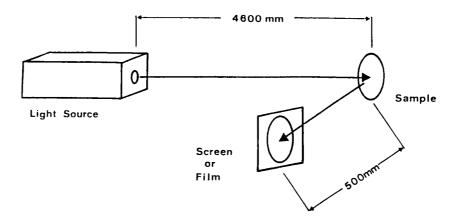

#### 4.2.4. Magic mirror topography

The magic mirror, or Makyoh, topography is a simple technique for characterising the morphology of mirror-like surfaces [94,95]. The basic principle of the method is shown in Fig. 16. At a small inclination from normal incidence, a collimated beam of light illuminates the whole surface of the sample under investigation. The reflected light is projected into a camera or onto a screen or photographic film to record the topographic image. Any deviations from an ideal mirror plane can cause contrast in the reflected image. The method is very simple, fast and non-destructive.

Particles enclosed in the bonding interface or a gas-filled delamination cause the wafer to locally bulge. In the case of a wafer with a mirror-polished backside, the convex surface deformation due to a bubble can be seen in the reflected image as a dark centre surrounded by a bright ring. As the radius of curvature concomitant with an interface bubble depends on the thickness of the wafers bonded, the ability of the method to detect voids is higher when a thinner wafer has been chosen as reflecting surface. To gain higher sensitivity, the wafer can even be thinned and polished after bonding [96].

Okabayashi et al. compared X-ray topography, ultrasonic microscopy and magic mirror topography; they found that for a  $350 \,\mu\text{m}$  thick silicon wafer, the magic mirror topography had a slightly lower resolution than X-ray topography [94]. In addition to contrast from the delaminations,

Fig. 16. Principle of Magic Mirror [94].

warpage caused during the initial contacting and other defects leaving surface features may complicate the interpretation of the images.

# 4.2.5. Void detection by etching

Unlike light transmission, C-mode scanning acoustic microscopy, X-ray diffraction topography or the Makyoh method, void detection by etching is a destructive technique. Either the bonded wafer pair is simply etched to thin it or a cross-section is being etched.

The first variant of the method relies on the fact, mentioned above, that thinning one of the wafers of a bonded pair under test enhances the visibility of voids simply through the decrease in the radius of curvature for thinner 'membranes' [96,97].

In the second variant, the sample is sawed or cleaved to expose a cross-section of the bonded interface to attack by etchant. Therefore, the samples must adhere strongly enough to withstand the cross-sectioning and immersion in the etching solution. The method permits the detection of voids too small for detection through light transmission, but it only can reveal those bubbles present in the plane of cross-sectioning.

Mitani et al. [98] decorated defects in silicon/silicon bond interfaces with a hot aqueous solution of potassium hydroxide (KOH) on samples sawed in suitable crystallographic directions. They utilised the well-known crystallographic anisotropy of silicon for etching in KOH and the preferential attack of defective silicon. During 15–30 min in the KOH solution, the stronger etching at voids enhances their visibility in optical or scanning electron microscopy.

Horning et al. [99] simply cleaved their silicon/silicon samples and, instead of KOH, they used 4–5 min room temperature Wright etching to decorate the interfacial defects. The main advantage of their procedure seems to lie with the simpler sample preparation and with the better visibility of the etch defects. Samples which were well-bonded apparently displayed only little etching in the interface, thus small defects are not obscured. By implication, the Wright etching technique was reported to require samples of higher adhesion than the KOH approach. Another drawback of the Wright etchant (aqueous solution of  $CrO_3$ ,  $Cu(NO_3)_2$ , HF, HNO<sub>3</sub>,  $CH_3COOH$ ) may be seen in its toxicity and cancerogenity.

For III–V compound semiconductor interfaces, Babic et al. immersed their samples in a  $1:1:50 \text{ H}_2\text{SO}_4: \text{H}_2\text{O}_2: \text{H}_2\text{O}$  solution for 90 s or substituted sulphuric acid by phosphoric acid [19].

#### 4.3. Quantification of adhesion

An important parameter in the characterisation of a bonding process is, loosely speaking, the 'amount' of adhesion. Practical adhesion can be quantified in a variety of ways, among others as Dupré work of adhesion or fracture surface energy, or as bond strength.

# 4.3.1. Measurement of surface energy

In the case of brittle materials which we are concerned here, the Dupré work of adhesion can be measured with fracture mechanical techniques. The work of adhesion and surface energies,  $\gamma_1$ ,  $\gamma_2$ , are related via

$$W_{\text{adhesion}} = \gamma_1 + \gamma_2 - \gamma_{12},\tag{10}$$

with the interface energy  $\gamma_{12}$ . The thermodynamic aspects of adhesion and interfacial energies are discussed, for example in Refs. [100–102].

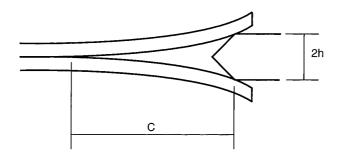

The most common approach for the measurement of fracture surface energies on bonded wafers uses an elaboration of Obreimoff's arrangement for controlled cleavage [36] described above: the

Fig. 17. Double cantilever beam test geometry under constant wedging conditions. The razor blade of thickness 2h causes a crack of length c.

double cantilever beam test geometry under constant wedging conditions, shown in Fig. 17. The elastic strain energy in the bent thin plate balances the work of adhesion  $W_{AB}$  required to form two new surfaces through the extension of the crack. A wedge of a thickness of 2h is inserted at the rim of the beams into the bond interface so as to debond an area of crack length *c*. At equilibrium, the critical strain energy release rate  $G_{Ic}$  equals the work of adhesion

$$W_{\rm AB} = 2\gamma = G_{\rm Ic} = \frac{3Eh^2d^3}{4c^4},$$

(11)

with d being the thickness of the beams and E denoting Young's modulus in the direction of crack propagation [102].

The work of adhesion can also be related to the critical stress intensity factor,  $K_c$ ; in the case of pure mode I loading, this can be expressed as [102–104],

$$W_{\rm AB} = 2\gamma = G_{\rm Ic} = \frac{K_{\rm Ic}^2 (1 - \nu^2)}{E},$$

(12)

with  $\nu$  denoting Poisson's ratio. One of the advantages of the stress-intensity factors in the case of a known crack geometry is their relation to uniformly applied stress [102],  $\sigma_A$ :

$$K_{\rm Ic} = \psi \sigma_{\rm A}^{\rm I} \sqrt{c},\tag{13}$$

with  $\psi$  a geometry term, tabulated for many crack geometries [105].

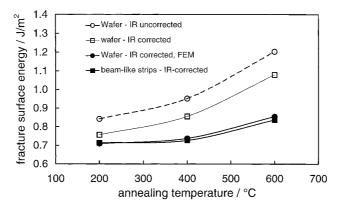

Maszara et al. probably were the first to apply the crack-opening characterisation method in the study of wafer direct bonding [106]. Following their example, the test customarily is applied to complete bonded wafer pairs, and, instead of the work of adhesion, most of the wafer bonding literature quotes the fracture surface energy  $\gamma$  as a measure for the bonding strength. The crack length usually is measured optically, allowing for the additional crack length shadowed by the tip of the wedge and for that part of the crack narrower than ca.  $\lambda/4$  of the probing wavelength. The double cantilever beam test applied to complete wafers is sometimes referred to as 'razor blade', 'Maszara' or 'crack opening' test. When executed with the due circumspection, the values should be reproducible to approximately 10%. However, because of the deviation from the proper double cantilever beam geometry, the measurement on complete wafers systematically overestimates the fracture surface energy [107]; as shown by Bagdahn et al. through a finite element analysis, the error increases for increasing adhesion, in their example from about 20% to 80% (Fig. 18).

With some caution, the test can also be applied to patterned wafers, where only a certain area,  $A_c$ , of the total wafer area  $A_t$  is available for bonding [108]. In the case of stripes of bonding running

Fig. 18. Fracture surface energy derived from various measurements on wafer and beam-like specimens, after Ref. [107].

parallel to the direction of crack propagation, the apparent fracture surface energy is reduced; this was compensated by a multiplicative factor  $A_t/A_c$ :

$$\gamma = \frac{3Eh^2d^3}{8c^4} \cdot \frac{A_{\rm t}}{A_{\rm c}}.\tag{14}$$

For stripes normal to the direction of crack propagation, the unmodified formula is applicable.

When bonding wafers of different thickness or elastic properties, the work of adhesion could be calculated according to

$$W_{\rm AB} = G_{\rm Ic} = \frac{3h^2 E_1 d_1^3 E_2 d_2^3}{2c^4 (E_1 d_1^3 + E_2 d_2^3)}.$$

(15)

The case of a thin wafer bonded to a thick one, or the testing arrangement of Fleming et al. [109], essentially is the system studied by Obreimoff with

$$W_{\rm AB} = 2\gamma = G_{\rm Ic} = \frac{3Eh^2d^3}{8c^4},$$

(16)

where only one beam is being bent.

Without proper precautions, the fracture surface energy derived from the blade test cannot be identified with the intrinsic surface free energy of a solid. Frequently, the test is not completely reversible (cf. also Ref. [37]) and above all, environmental conditions like humidity are known to affect the observed fracture surface energy considerably, often causing a decrease with time [110]. The sensitivity of the fracture surface energy of silicon dioxide, for instance, towards humidity has long been recognised [111]; cracks in pure silicon, however, appear to be rather immune to chemical processes [102]. The main appeal of this blade test applied to complete bonded wafer pairs is its ease of use, requiring no special sample preparation. When comparing data from different experimentators, or when comparing the values with other techniques, the short-cuts taken in the customary blade test should be borne in mind. In addition, there is sometimes some ambiguity in terminology. The fracture surface energy measured occasionally is referred to as interface energy which is not to be confused with the interfacial energy mentioned above. Bond or bonding energy are other terms not unknown in the direct bonding literature. Those terms often make it difficult to know precisely whether the fracture surface energy or the work of adhesion, twice the fracture surface energy, is meant.

In principle, creating a new surface by advancing a crack through the contact interface or advancing the bonding front should be equivalent. Suitably structured wafers may serve as tools for an 'in situ' determination of the work of adhesion. Horning et al. patterned silicon wafers with a sequence of parallel lines of known height which serve as wedges [112]. If the line height, line spacing and wafer-thickness were chosen appropriately for the work of adhesion, the wafers bonded between a given pair of lines. A variation of line spacings across the wafer included a range of bond energies. The bond energy was then measured by a simple IR inspection. The technique was used to investigate the influence of surface treatments on the strength of adhesion. With a method similar in spirit, the adhesion was estimated with which two 10 nm thick platinum films, bonded immediately after sputter-deposition onto silicon, adhere to each other [113].

The double cantilever beam test under constant loading was used by Lord Raleigh in his investigation of the bonding of glass [37]. For a rectangular crack geometry, the strain energy release rate is an increasing function of the crack length, making the system unstable. Preparation of a chevron-type specimen geometry stabilises the system again, and such a geometry was used in that investigation. The laborious preparation necessary understandably has never become popular. However, when bonding structured wafers, proper chevron test geometries have been successfully applied [114].

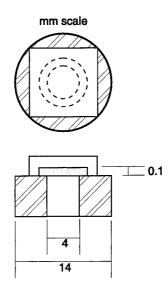

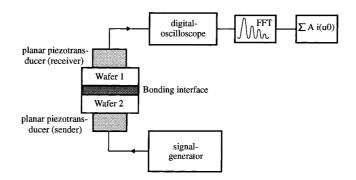

Fracture surface energies as a measure for adhesion can also be extracted from hydrostatic blister tests [115]. Shimbo et al. bonded a silicon wafer with shallow wells against an equivalently polished silicon disk with through-holes, as illustrated in Fig. 19 [44]. Through the hole of a test chip, hydrostatic pressure was applied and the fracture strength was taken as a measure for the strength of adhesion.

# 4.3.2. Tensile testing

Perhaps the most popular characterisation technique is the tensile test [92,116]. The specimen under test is pulled normal to the bonding interface until the system ruptures (Fig. 20(a)). Almost generally, the stresses observed are much smaller than those which correspond to the forces acting in the bonding interface. This is usually attributed to small flaws in the bond (deliberately introduced structures would act similarly [117]), to elastic stresses stored during formation of the joint, or for

Fig. 19. Sample geometry for adhesion test using hydrostatic pressure [44].

Fig. 20. Tensile test geometrie. (a) Principle, (b) modification for thin films.

instance to defects at the edges of the sample. The applied stress is being concentrated at certain defects and this leads to early failure [118].

Most experimentators mention that the sample under test should be slightly larger than the test stubs, in order to prevent glue creeping around the edges and covering the sides of the test chip (Fig. 20(a)) [116]. The alignment of the test stubs is of critical importance, as small deviations from the surface normal already induce bending moments which can cause premature failure of the sample under test [119]. When applying the adhesives properly, tensile strength values up to 80 MPa may be measured for a standard geometry; for more strongly bonded samples the glue between sample and test stubs gives only a lower limit for the adhesion. Care needs to be taken in dicing the bonded wafers for tensile testing to minimise residual damage at the periphery of the test specimens.

In the case of thin films transferred via direct bonding to a wafer, Abe et al. recommended a modified geometry, shown in Fig. 20(b) [92].

# 4.3.3. Other tests

Occasionally torsion or shear tests are being used [119].

With all these tests, it is of importance to assess a suitable number of equivalent specimens. Any comparison, be it quantitative or qualitative, must allow for the strong dependence of critical tensile stress values on flaws. When strengthening the bonds of hydrophilic silicon wafers, the tensile strength often does not increase monotonically with the annealing temperature in spite of the monotonic increase in bonding energy. The reason for this is generally ascribed to formation and later disappearance of bubbles in the bonding interface [116].

Often adhesion is assessed simply by noting that a bond withstood certain treatments like grinding of one of the wafers, dicing up the bonded pair through sawing or cleaving, or other loads associated with the application in mind.

An interesting question particularly for microsystems applications, yet hitherto not pursued in much detail, is the problem of long-term stability of subcritically loaded samples [114,120]. The lifetime of joints can be calculated using fracture mechanical models incorporating stress corrosion [114].

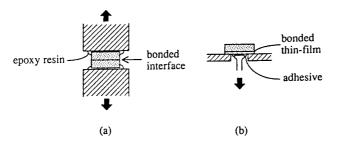

All tests presented so far determine some parameter characterising the adhesion destructively. A non-destructive evaluation method with a reasonable lateral resolution would be advantageous. There are several approaches being pursued, all based on acoustic techniques, to realise a non-destructive test for adhesion characterisation.

One method is based on the non-linear dependence of the backdriving force at the bond interface on the deflection, Fig. 21 [121,122]. By increasing the amplitude of the ultrasonic probe pulses, the back-driving force of the bond interface was being brought into the non-linear regime. As schematically shown in Fig. 21, a sinusoidal signal is transmitted into the sample under test. A broad-band ultrasonic transducer is used as receiver for the signal modulated by the elastic response

Fig. 21. Schematic set-up of for the non-destructive quantification of adhesion using acoustic microscopy measurements [122].

of the interface. The received signal is Fourier transformed and a summation of the Fourier components served the authors as measure for the back-driving force. Its maximum was taken as a measure of the strength of bonding. Local variations in adhesion and an increase as a function of annealing temperature could be measured. Further developments in ultrasonic transducers could allow a realisation of the technique's potential [122].

Hao et al. used picosecond ultrasonics to generate and detect acoustic pulses in bonded siliconon-insulator structures [123,124]. A laser pulse hit the aluminium-coated wafer surface and launched a strain pulse into the structure. At interfaces the pulse is partially reflected and those echoes are being detected via the modifications in reflectivity which they impart on the aluminium layer. The authors asserted that numerical fitting allowed them to detect improvements on bond quality; however, no direct comparison with results obtained with another technique have been provided.

#### 4.4. Methods to unravel bonding chemistry

Due to its steric constraints, wafer direct bonding represents a novel environment for the study of chemical reactions. During the annealing of bonded wafer pairs, various chemical reactions must occur to facilitate an increased adhesion. Often the reactions can involve by-products whose evolution can determine the overall reaction behaviour. The chemical reactions upon which much of wafer direct bonding is based may also have a bearing on the long-term stability of the bonding joint or on the pressure attainable in encapsulated cavities. With the exception of silicon bonding, the study of the interfacial chemistry has not yet received much attention. The analysis of the interfacial reactions is being complicated by the initially weak adhesion of many of the systems of interest. Only in exceptional circumstances can destructive techniques like analytical electron microscopy or secondary ion mass spectroscopy be used. Additionally, the area of interest is buried typically in wafer thickness, ca. 1/2 mm, below the surface, ruling out surface analytical probes like X-ray photoelectron spectroscopy.

Two approaches have been demonstrated as particularly well suited to the problem of wafer bonding chemistry, one being a destructive mass spectroscopic technique, the other being a variant of infrared spectroscopy, leaving the bonding interface intact but requiring the preparation of a suitable specimen out of a bonded wafer pair.

#### 4.4.1. Mass spectroscopy

The mass spectroscopic analysis of gases evolving during the annealing of bonded samples is mainly the work of Mack [83,84,120,125]. For his experiments, he etched holes into the wafers so

Fig. 22. Specimen geometry for IR spectroscopy in multiple internal reflexion on bonded samples [129].

that only a thin membrane had been left; Fig. 12 gives an example of the patterns used. Bonding then created cavities in which the gases could be collected. The deflection of the membrane permitted measuring the internal gas pressure as a function of annealing time or temperature. Hermeticity and interfacial diffusion were thus determined. After in vacuo fracturing of those membranes, the gas content could be analysed mass spectrometrically.

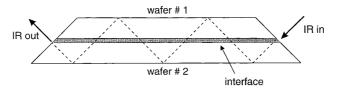

## 4.4.2. IR spectroscopy

For the infrared spectroscopic analysis of bonded silicon wafers, multiple internal transmission has been established as a most useful geometry with which even for buried layers the sensitivity can be achieved necessary for the detection of monolayers [126–130]. The schematic drawing of Fig. 22 illustrates the shape of a typical sample: the light entrance and exit edges are bevelled, either as shown or to form a parallelogram. In the case of weakly adhering specimens, there is a certain risk that the bonded wafers separate upon dicing, bevelling or chemical cleaning [127]. With the void detection methods described above, like optical transmission or scanning acoustic microscopy, the integrity of the samples can be ascertained. Because of the protective nature of bonding [131], the interface chemistry can be investigated over prolonged periods of time and for various annealing conditions.

Multiple internal transmission infrared spectroscopy is very sensitive to absorption perpendicular to the interface, and interface absorption is strongly enhanced compared to absorption at the outer surfaces of the specimen. However, in-plane absorption would be difficult to detect [127]. The technique provides chemical information via the infrared active molecular species present in the interface. In addition, from shifts of spectral features, the interaction which mediates the adhesion, for example van der Waals forces or hydrogen bonding, can be inferred. As an example, infrared spectroscopy had been used to corroborate that in hydrophobic silicon bonding the hydrogen-terminated (111) oriented wafers adhere essentially through van der Waals interactions [129].

# 5. Silicon direct-bonding

## 5.1. Introduction

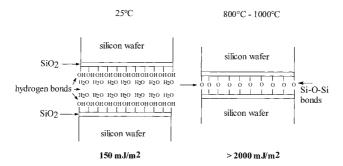

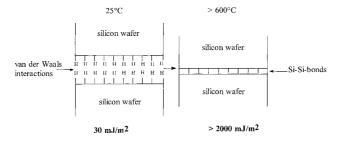

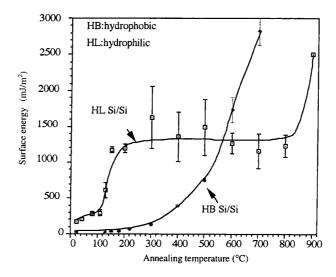

The phenomenon that mirror-polished oxidised or non-oxidised silicon surfaces bond to each other when they are contacted at room temperature was first reported in 1985/1986 independently by two research groups [44,45]. In the meantime many other materials have been joined by wafer bonding; however, silicon remains the best studied system in wafer bonding technology and is used frequently as a model for a better understanding of the bonding behaviour displayed by other materials. It is widely accepted that intermolecular interactions including van der Waals forces are responsible for the bonding phenomenon at room temperature. Depending on the surface species

involved hydrogen bonding may also play an important role in wafer bonding. However, neither van der Waals forces nor hydrogen bonds are strong enough to join two solids irreversibly. Thus, it is highly desirable to form strong chemical bonds (covalent bonds) across the interface. As we will see in this chapter, the silicon surface may be modified in many ways so that the actual bonding may be caused by weak van der Waals interaction, by hydrogen bonding or even by strong covalent bonds. If the bonding is carried out under ultra-high vacuum covalent bonds even may be formed at room temperature. However, in general, the adhesion is relatively weak at room temperature and is typically increased by annealing the joint. At elevated temperatures, chemical reactions take place between the surface species of opposing wafer sides which usually yield covalent bonds. Typically temperatures of more than  $1100^{\circ}$ C have been regarded as necessary for this step [14,44,45]. In recent years, however, a variety of procedures have been developed which yield strong adhesion at moderate temperatures. By-products which are formed during interface reactions may cause problems as they may lead to a build-up of pressure in the interface and subsequently to local debonding. Acceptable by-products in silicon wafer bonding are water and hydrogen for water may be consumed through a reaction with silicon and the small hydrogen molecules readily diffuse in the silicon lattice or into a silicon dioxide layer.

Materials which are difficult to bond due to an unfavourable surface chemistry may be bonded via silicon interlayers. Silicon layers can be deposited on many substrates and chemo-mechanical polishing ensures bond-quality surfaces. Since the bonding is governed by the surface species of the two joined materials, the basic bonding behaviour of materials with silicon layers is analogous to the bonding of pure silicon wafers.

In this chapter the actual bonding of different silicon surfaces is described.

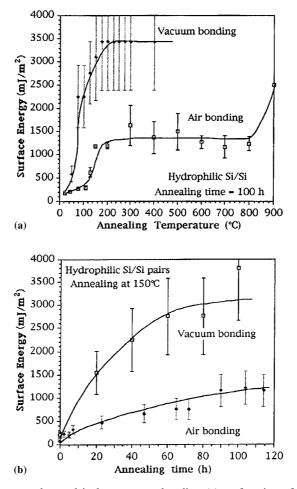

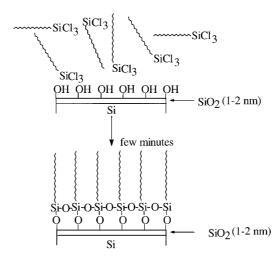

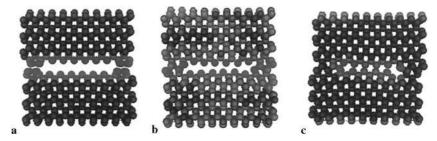

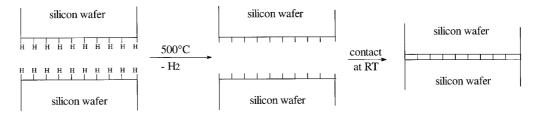

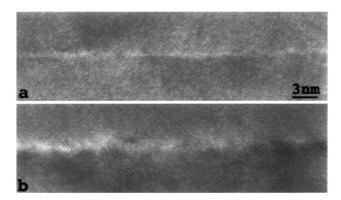

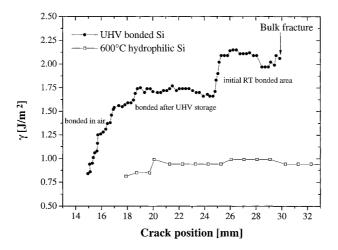

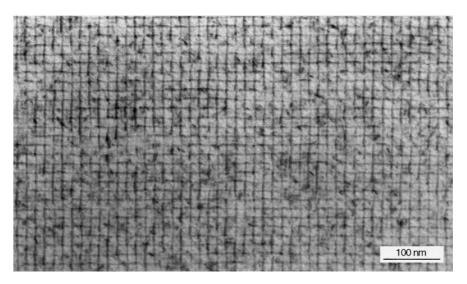

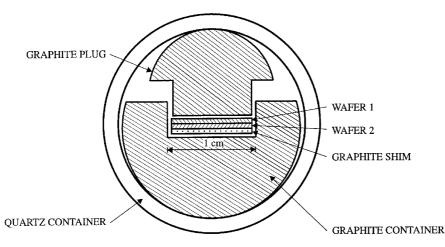

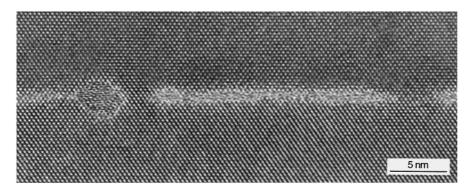

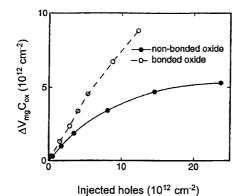

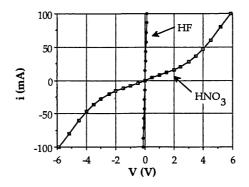

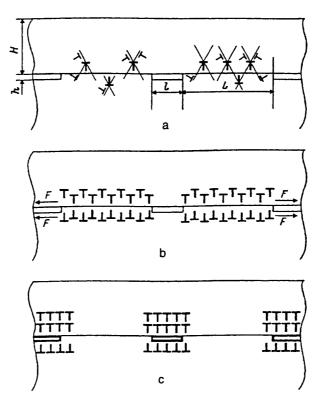

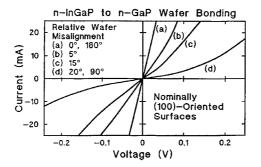

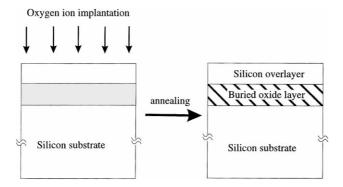

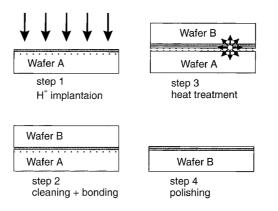

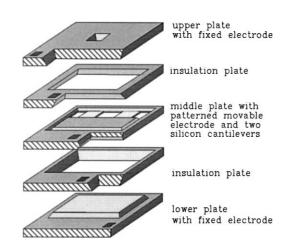

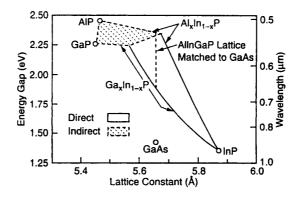

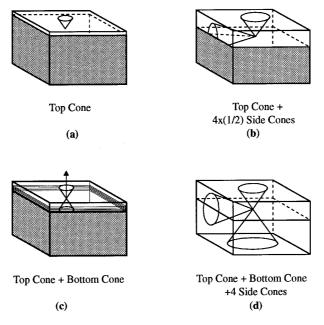

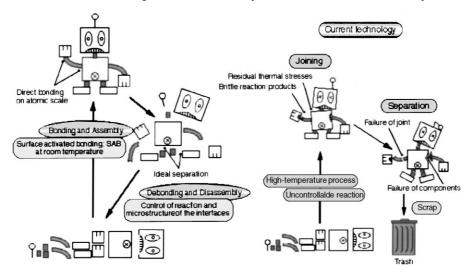

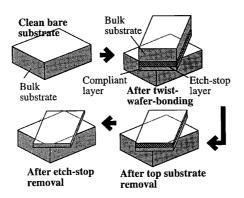

It has been stressed already that particulates which are present on the wafer surface before bonding lead to unbonded areas. As a consequence bonding has to be carried out in a particle-free atmosphere. The bonding is either done manually, or a commercially available bonder is used. The latter is particularly useful if the wafers have to be aligned before bonding. For research purposes and small budget production a so-called micro-cleanroom for utilisation in a normal laboratory has been developed. The set-up is described in chapter 3.