# Wafer-Level Parylene Packaging With Integrated RF Electronics for Wireless Retinal Prostheses

Wen Li, *Member, IEEE*, Damien C. Rodger, *Member, IEEE*, Ellis Meng, *Senior Member, IEEE*, James D. Weiland, *Senior Member, IEEE*, Mark S. Humayun, *Member, IEEE*, and Yu-Chong Tai, *Fellow, IEEE*

Abstract-This paper presents an embedded chip integration technology that incorporates silicon housings and flexible Parylene-based microelectromechanical systems (MEMS) devices. Accelerated-lifetime soak testing is performed in saline at elevated temperatures to study the packaging performance of Parylene C thin films. Experimental results show that the silicon chip under test is well protected by Parylene, and the lifetime of Parylenecoated metal at body temperature (37 °C) is more than 60 years, indicating that Parylene C is an excellent structural and packaging material for biomedical applications. To demonstrate the proposed packaging technology, a flexible MEMS radio-frequency (RF) coil has been integrated with an RF identification (RFID) circuit die. The coil has an inductance of 16  $\mu$ H with two layers of metal completely encapsulated in Parylene C, which is microfabricated using a Parylene-metal-Parylene thin-film technology. The chip is a commercially available read-only RFID chip with a typical operating frequency of 125 kHz. The functionality of the embedded chip has been tested using an RFID reader module in both air and saline, demonstrating successful power and data transmission through the MEMS coil. [2010-0008]

*Index Terms*—Accelerated-lifetime soak testing (ALST), chip packaging, Parylene C, radio-frequency (RF) coil.

# I. INTRODUCTION

W IRELESS retinal prostheses employ electronic systems to partially restore the lost visual function of blind patients due to diseases, such as retinitis pigmentosa and age-related macular degeneration. In particular, an epiretinal approach has been developed by implanting high-density electrodes on the inner retinal surface to electrically activate remaining nerve cells [1]–[3]. For such systems that involve completely intraocular implantation, there is a need for chip integration and packaging technologies that are capable of

Manuscript received January 7, 2010; revised March 23, 2010; accepted April 26, 2010. Date of publication June 14, 2010; date of current version July 30, 2010. This work was supported in part by the Engineering Research Center Program of the National Science Foundation under Award EEC-0310723 and in part by a fellowship from the Whitaker Foundation (D.R.). Subject Editor S. Shoji.

W. Li is with the Department of Electrical and Computer Engineering, Michigan State University, East Lansing, MI 48823 USA (e-mail: wenli@egr.msu.edu).

D. C. Rodger and M. S. Humayun are with the Keck School of Medicine, University of Southern California, Los Angeles, CA 90007 USA (e-mail: drodger@usc.edu; humayun@usc.edu).

E. Meng and J. D. Weiland are with the Department of Biomedical Engineering, University of Southern California, Los Angeles, CA 90007 USA (e-mail: ellismen@usc.edu; JWeiland@doheny.org).

Y.-C. Tai is with the Department of Electrical Engineering, California Institute of Technology, Pasadena, CA 91125 USA (e-mail: tai@mems.caltech.edu).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JMEMS.2010.2049985

high-lead-count interconnections while ensuring system biocompatibility, flexibility, and long-term reliability [4]. Traditional integration methods use soldering, wire bonding, flip chip, and tape-automated bonding to form interconnections between discrete components [5]. They are labor intensive, inefficient, and costly, limiting the achievable integration density. In addition, because the bonding materials used in these technologies are generally not biocompatible, extra protection layers would be required for biomedical applications. Butler et al. [6] developed a multichip module packaging process, by which microelectromechanical systems (MEMS) devices can be integrated with complementary metal-oxide-semiconductor (CMOS) electronic dies using the "chip first" General Electric high-density interconnect technology. Although this technology bypasses many issues with traditional interconnecting methods, its lack of flexibility and biocompatibility remains a problem unsolved. In recent years, much effort has been placed on the development of advanced packaging methods for bioimplant systems using polymers or glass [7]-[9]. For example, a microflex interconnection technology has been demonstrated [8] by bonding individual components on a predefined flexible polyimide substrate. While devices packaged with this technology are flexible enough, their long-term biocompatibility has not been proven. The process is also tedious and costly for the integration of high-electrodedensity devices. Harpster et al. [9] demonstrated the long-term hermeticity of glass-silicon implantable packages, but these packages are too rigid for retinal prostheses.

To overcome the challenges encountered in current technologies, we developed a chip-level integrated interconnect packaging method [10] that enables the integration of CMOS integrated circuit (IC) chips and prosthetic electrodes [11], and have now extended it to an embedded chip integration technology that can readily incorporate multiple monolithic chips in silicon housings and functional Parylene-based MEMS devices (e.g., MEMS coil) [12] to achieve high-level system functionalities. In this new approach, chip-to-packaging interconnections are established using standard microfabrication techniques, such as photolithography and metal etching; therefore, no wire bonding, bump bonding, or soldering is needed. In addition, the interconnect density is limited only by photolithography resolution and microfabrication tolerance, which offers the possibility to achieve high-lead-count (> 1000) integration. Finally, the favorable mechanical and chemical properties of Parylene C [13] allow our final devices to be highly flexible and biocompatible. Other advantageous properties of Parylene C include its transparency and conformal pinhole-free deposition

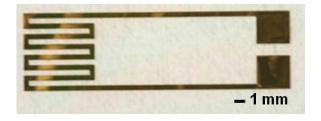

Fig. 1. Fabricated thin-film resistor with pure gold metallization and Parylene C packaging.

in a room-temperature chamber, allowing our packaging technology to be post-IC compatible.

## II. PARYLENE-C PACKAGING BEHAVIOR

Parylene C is known to have lower water and gas permeability compared with two other commonly used polymers, namely, polydimethylsiloxane and polyimide [14]. However, human body fluid, fairly well approximated by an oxygenated saline solution with a salt content of about 0.9% at  $pH \sim 7.4$ and  $37 \pm 1$  °C [15], is very corrosive for metal and electronic circuits. The long-term stability and reliability of Parylene C packaging in liquid environments have not been fully understood yet and therefore deserve further investigation prior to in-depth technology development. In this paper, we have studied Parylene packaging behaviors through accelerated-lifetime soak testing (ALST) in hot saline (0.9% NaCl solution), which is a close imitator of body fluid. Two major structures used in the system integration, namely, Parylene-coated metal and Parylene-coated circuitry, have been tested, as discussed in the following sections.

## A. Parylene-Protected Metal

To study the lifetime of Parylene-protected metal, thin-film resistors consisting of Parylene-C-coated gold wires are designed as test structures [16], [17]. Samples are microfabricated using a Parylene-metal-Parylene thin-film technology [18], starting with Parylene C vapor deposition (PDS 2120 system, Special Coating Systems, Indianapolis, IN) on a standard 4-in silicon wafer. After that, a 200-nm layer of gold is deposited in an e-beam evaporator (SE600 RAP, CHA Industries, Fremont, CA), followed by metal wet etching with photoresist as a mask. After the photoresist mask is removed, Parylene deposition is performed again to seal the metal structure. Then, photoresist is spun and patterned to expose contact pads, as well as to define the device shape. Finally, unwanted Parylene C is removed using oxygen plasma in a reactive ion etch (RIE) system (Semi Group Inc. T1000 TP/CC), and devices are then released from the substrate in a water bath. Fig. 1 shows an example of fabricated devices that have the same metal linewidth and edge space width of 500  $\mu$ m. Prior to soak testing, all fabricated samples are treated in a vacuum oven with nitrogen backfill at 200 °C for two days. It has been experimentally demonstrated that this thermal treatment can enhance the adhesion of Parylene/Parylene interface and also lower the water permeation of Parylene thin film [17], [19].

TABLE I SOAK TESTING RESULTS OF PARYLENE-PROTECTED METAL UNDER BOTH PASSIVE AND ACTIVE CONDITIONS

| Testing   | Thickness of Parylene | MTTF       |                        |

|-----------|-----------------------|------------|------------------------|

| Condition | Coating (µm)          | 77 °C      | 90 °C                  |

| Passive   | 4.7                   | > 250 days | $\sim 70 \text{ days}$ |

| Active    | 4.7                   | N/A        | < 2  days              |

|           | 9.2                   | N/A        | $\sim 62 \text{ days}$ |

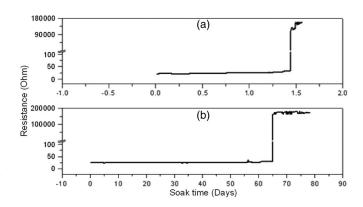

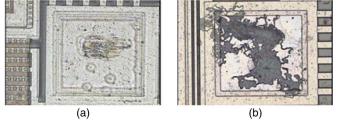

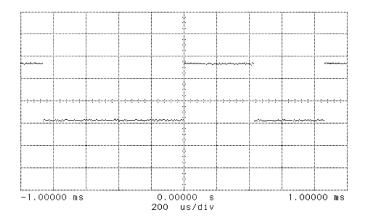

Fig. 2. Typical aging curve of tested samples under active conditions. (a) Sample with 4.7- $\mu$ m Parylene coating failed after less than two days of soaking. (b) Sample with 9.2- $\mu$ m Parylene coating can withstand long-term soaking of approximately 60 days.

The process typically takes effect at temperatures of over 180 °C, below which Parylene delamination occurs after only one day of soaking, indicating that no significant improvement is achieved. It is of note that the process temperature must be lower than the melting temperature of Parylene C (290 °C), as strong recrystallization of Parylene can happen beyond this point [20], [21], resulting in brittle polymer films.

The samples are tested under accelerated conditions both passively and actively. In the passive soak testing, devices are immersed in saline at elevated temperatures and then removed daily from the oven in order to monitor for failures under an optical microscope. The active soak testing is conducted in a simplified electrochemical setup that consists of a platinum wire as a reference electrode and the tested sample as a working electrode. During the experiments, the reference electrode is grounded, and a square wave with a magnitude of 6 V and a frequency of 50 Hz is continuously applied on the working electrode to create a potential difference between the two electrodes in saline. The test unit is then heated in a convection oven, and the dc resistance of the thin-film resistor is recorded every 10 min using an HP 4145 B semiconductor parameter analyzer (HP/Agilent Technologies Inc., Santa Clara, CA) controlled by a LabView program (National Instruments, Austin, TX). Five samples are tested under each condition, and their mean times to failure (MTTFs) are recorded when failures are observed, as summarized in Table I. In the passive mode, sample failures are considered as uniform water bubbles or delaminations at the interface of Parylene/Parylene or Parylene/metal. While in the active mode, we define sample failures as soaking time points when resistance increases significantly, usually by over three orders of magnitude of the original value (Fig. 2).

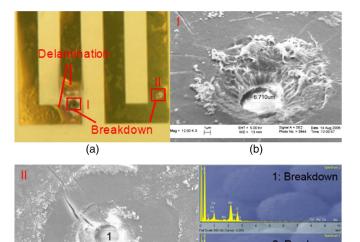

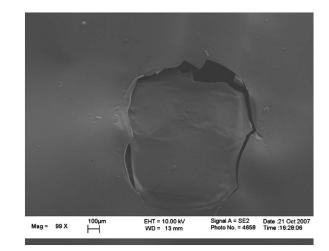

Fig. 3. (a) Parylene breakdowns occur in a 4.7- $\mu$ m Parylene-coated sample, and delaminations are observed surrounding the breakdown area. (b) SEM image showing a crater-shape breakdown hole. (c) SEM images and EDS spectra on another failed area. Exposed gold element is detected inside the breakdown hole, indicating that a through hole is formed.

The passive soak tests are carried out at both 77  $^{\circ}$ C and 90  $^{\circ}$ C, so that the MTTF at body temperature can be extrapolated using an Arrhenius relation in (1) [22]

$$MTTF = A \exp\left(-\frac{E_a}{kT}\right) \tag{1}$$

where A is the pre-exponential constant,  $E_a$  is the activation energy, T is the temperature in Kelvin, and k is the Boltzmann's constant. Based on the data in Table I, an activation energy of approximately -1.07 eV and an A of around  $9 \times 10^{-14}$  can be calculated for Parylene-protected metal, resulting in an MTTF of over 67 years at a body temperature of 37 °C.

Samples with two different thicknesses of Parylene coating are tested under the active condition. Parylene breakdowns occur in samples with  $4.7-\mu m$  Parylene coating after a short period of soaking, followed by Parylene delaminations expanding gradually from the breakdown areas. The breakdown regions (Fig. 3) are analyzed using scanning electron microscopy (SEM) and energy-dispersive X-ray spectroscopy (EDS) (LEO 1550VP Field Emission SEM—Oxford EDS). The EDS spectra confirm that the Parylene is locally melted into a through hole over the metal and the embedded metal is exposed. Parylene cracks radiate from the breakdown hole, which is mainly caused by thermal stress. It is also noted that the breakdown only appears on one side of the sample, while the other side remains intact, indicating that the failure is initiated either at the interface of Parylene/metal or inside the Parylene film.

Although the mechanism of Parylene breakdown is not completely clear, it is possible that the failures are initiated from certain areas where large defects and particles reside. Electrochemical reactions are accelerated at these areas due to high electric field concentrations and the direct exposure of metal

Fig. 4. Microscope images of chip metal pads on (a) a chip with Parylene coating after six months of soaking and (b) a bare chip without Parylene coating after two days of soaking.

to the saline, resulting in local metal corrosion. The circular shape of breakdown crater is mainly confined by the shape of exposed metal [23], which is similar to the size of particles. In samples coated with 9.2- $\mu$ m Parylene C, without seeing Parylene breakdown, water bubbles are observed uniformly across the metal–Parylene interface. It is possible that thicker Parylene films may conformally coat particles and thus can prevent the unwanted particle-induced breakdown. The thickness of polymer films should be carefully selected in order to cover the majority of defects and particles while not compromising the flexibility of polymer package. Preliminary results suggest that flexible films with a thickness of approximately 10  $\mu$ m could cover most defects or particles generated under our cleanroom conditions (Class 1000).

# B. Parylene-Protected Chip

Similar ALSTs are performed using Parylene-coated IC chips. A die-form passive read-only radio-frequency identification (RFID) chip (EM 4100, EM Microelectronic, Switzerland) is selected as a test chip. This chip is a CMOS IC with exposed contact pads made of layered Al–Ni–Au metals. It can be powered with a pair of coils through an electromagnetic field. By turning the modulation current on and off, the chip sends back a 64-b sequence stored in the memory array, which can be detected with an oscilloscope. The operation frequency of the chip is between 100 and 150 kHz, with 125 kHz being typical.

Unpowered soak testing is performed in saline at 77 °C. Prior to soaking, RFID chips are cleaned with isopropanol and deionized water, and then completely coated with approximately  $10-\mu$ m Parylene C. During the soaking period, the samples are examined daily under a microscope. The soak lasts up to six months, and the samples are removed from saline for functionality measurement using a Wentworth Labs 11PO900 probe station (Wentworth Laboratories, Inc., Brookfield, CT). In order to access the contact pads, the Parylene coating on the pads is removed with oxygen plasma etching or probe tip scratching. Preliminary results show that the samples with Parylene protection have no observable metal damage on the contact pads even after six months of soaking (Fig. 4). The chip still functions, indicating that Parylene-protected IC circuits can remain intact in 77 °C saline for more than six months.

Parylene C packaging performances in liquid environments are studied using the long-term ALST. The test results suggest that Parylene C is very promising for metal and IC circuit

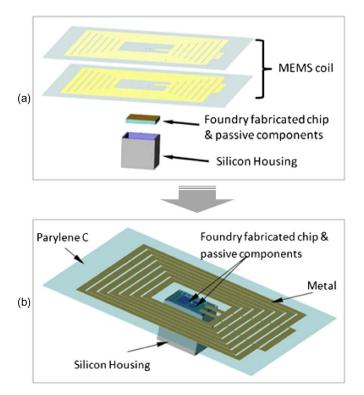

Fig. 5. Conceptual schematic of the embedded chip packaging. (a) Discrete components before integration. (b) Parylene-based MEMS RF coil is integrated with an IC chip embedded in a silicon shell.

protection in intraocular retinal prostheses, and pave the way for the development of the flexible Parylene-based chip integration technology. There are also outstanding issues that deserve future investigation. For example, the ovens used for testing have a temperature variation of +/-2 °C. Due to the exponential nature of the Arrhenius relation, this temperature change can significantly affect the accuracy of prediction. In addition, only a small sample set has been analyzed in the initial study because these tests are very time consuming. Continuous experiments will be necessary to collect more data in order to further refine our knowledge of Parylene packaging behavior.

# **III. RF-COILED CHIP INTEGRATION**

## A. Integrated System Design

An embedded chip integration technology is proposed, in which individual prefabricated chips and discrete components (e.g., capacitors) are embedded in a carrier silicon wafer and sealed with Parylene C. Other surface MEMS structures, such as electrode arrays and RF coils, can be constructed subsequently on the same platform. All interconnections between MEMS devices and chips can be made simultaneously, using standard photolithography and metal patterning process. Fig. 5 shows a conceptual schematic of the embedded chip packaging technology, showing how a prefabricated IC chip is directly integrated with a dual-metal-layer MEMS coil.

The same EM 4100 read-only RFID chip is integrated with an RF MEMS coil for the demonstration of this integration scheme. To determine the dimensions of Si housings, these chips are imaged with a WYKO interferometer (Veeco Instrument Inc., Woodbury, NY) and are measured to have mean dimensions of 1 mm in length, 0.98 mm in width, and 182  $\mu$ m in thickness. A planar microcoil is designed for wireless power and data transmission, which has two metal layers with 22 turns on each layer and an overall size of 2 cm by 2 cm. Having known the coil geometries, the electrical characteristics of the coil, including its self-inductance, series resistance, and parasitic capacitance, can be predicted using established analytical models, as discussed in [24]–[28]. Because of the low power consumption of the RFID chip, only the coil is needed to power the circuit, and no extra capacitor is required.

# B. Fabrication

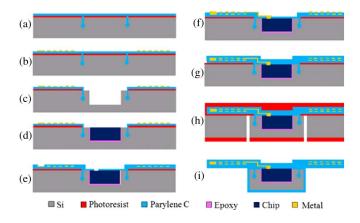

Fig. 6 shows the detailed fabrication process, starting with a standard 4-in wafer that is  $\sim 550 \ \mu m$  thick and coated with a layer of sacrificial photoresist. A 5- $\mu$ m layer of Parylene C is then deposited on top of the photoresist. To secure Parylene on the substrate, Parylene anchors surrounding the chip housings are etched into silicon using Bosch process in a deep RIE system (Unaxis Corporation, St. Petersburg, FL) [29]. After Parylene deposition, a 500-nm layer of gold is deposited in an e-beam evaporator and patterned to form the first layer of coil wires. Next, cavities matching the chip dimensions are etched into the Parylene and silicon using RIE and the Bosch process, and the chips are then dropped into the cavities with an average lateral displacement of less than 10  $\mu$ m. During this procedure, epoxy is applied to the bottom of the cavities as needed in order to compensate for cavity depth inaccuracy and to fill the gaps surrounding the chips. A metal pole with a flat silicon piece attached on one end is used to push the chips into the cavities and to level the surface. After the chips are fitted into the cavities, Parylene deposition is performed again to seal the chips in place and to form an insulation layer between two metal layers, followed by oxygen plasma etching to properly open interconnection vias. A second 500-nm layer of gold is then deposited and patterned as the top layer of coil wires and chip interconnects. Another 5- $\mu$ m layer of Parylene C is coated on top, followed by oxygen plasma patterning to define the profile of devices. Through-wafer trenches surrounding the chips are then etched from the backside of the wafer using the Bosch process, and the Parylene-based coils are released from the substrate, carrying the chips that are completely encapsulated in silicon housings. Lastly, the entire device can be sealed with Parylene for extra protection.

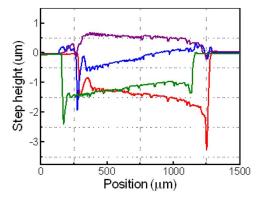

In this integration method, minimizing the vertical displacement of the chip from the wafer surface is crucial for subsequent photolithography and metallization steps. Large vertical displacements can lead to broken wires and open circuits. The surface heights of the chips are measured with a stylus profilometer P-15 (KLA-Tencor, San Jose, CA) after the chips are anchored in place in the silicon shell. Fig. 7 shows the surface profiles of four successfully integrated chips with respect to the surrounding substrate. The overall vertical displacements from the wafer surface are within 6  $\mu$ m, providing sufficient flatness for subsequent processes.

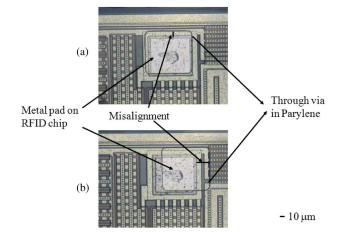

Another important aspect is the horizontal alignment of perimeter interconnects to the embedded chips, which limits the

Fig. 6. Detailed process flow of the embedded chip integration scheme.

Fig. 7. Vertical displacements of four successfully integrated chips: The wafer surface corresponds to 0- $\mu$ m step height.

Fig. 8. (a) Example of < 10- $\mu$ m lateral misalignment of the chip. (b) Example of > 10- $\mu$ m lateral misalignment of the chip.

interconnection density of the integration. By design, the chips should be self-aligned in the silicon housing to within 10  $\mu$ m of lateral displacement; however, some chips were misaligned by more than 10  $\mu$ m due to the dimension variation of the chips themselves (Fig. 8). With tighter tolerance on cavity sidewalls, or with more precise chip-alignment lithography, this alignment deviation can be reduced in the future to achieve high-lead-count integration.

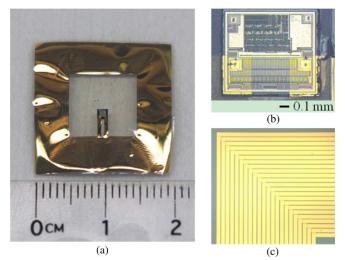

Fig. 9. Integrated RFID tag. (a) Overall view of the device. (b) Close-up view of the embedded RFID chip. (c) Close-up view of the metal traces of the MEMS coil.

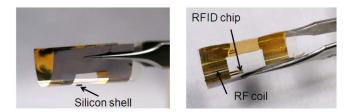

Fig. 10. Flexibility of the Parylene-metal-Parylene thin-film structure.

### C. Fabrication Results

We have successfully integrated the RFID chip with the Parylene-based RF coil, and Fig. 9 shows an example of a fabricated embedded RFID tag. In this device, the self-inductance of the receiver coil is approximately 16  $\mu$ H, and the dc resistance is around 275  $\Omega$ . The quality factor (*Q*-factor) of the coil is calculated with a value of approximately 0.05 at 125 kHz. The total thickness of the Parylene–metal–Parylene thin film is approximately 20  $\mu$ m.

Because of the excellent mechanical strength and intermediate flexibility (Young's modulus  $\approx$ 4 GPa) of Parylene C, this final device is very flexible and foldable, allowing the device to be placed in direct contact with delicate tissue during surgical implantation (Fig. 10). The coil area is puckered due to thermal stress, which can be allayed with a postfabrication annealing process. During this treatment, the devices are sandwiched between two metal plates and annealed typically at 200 °C. The annealing treatment can also be used to reshape Parylene–metal–Parylene thin films into geometries of interest for target applications [11], [12].

## D. Testing Results and Discussion

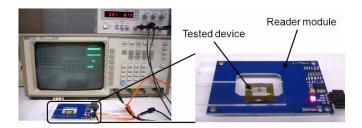

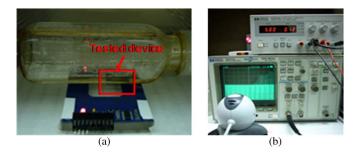

The functionality of the embedded RFID chip is tested with a commercially available RFID reader module (Parallax Inc., Rocklin, CA). This module contains an integrated coil to transmit RF energy and receive the data from the RFID chip. The transmission coil has dimensions of 60 mm by 66 mm. Fig. 11

Fig. 11. Test setup to verify the function of the integrated RFID tag. The tested device is placed on top of a commercially available RFID reader module, and the output signal is observed using an oscilloscope.

Fig. 12. Typical signal readout from the RFID reader module.

Fig. 13. (a) Test setup to evaluate the function of the integrated RFID tag in saline solution, showing a test unit heated in the convection oven. (b) Real-time monitoring of the signal readout using a webcam.

shows a typical test setup, in which the reader module is driven by a 5-V dc voltage power supply and the output port of the reader is connected to an oscilloscope in order to monitor the signal readout. When the RFID tag is placed within the reading distance of the reader, the information stored in the chip will be sent back to the reader, and an 8-b transistor–transistor logic signal sequence can be observed on the oscilloscope (Fig. 12). The spatial separation between the primary and secondary coils is varied during the measurement, and a maximal detectable range of 3–4 mm is found. This reading distance is mainly limited by the low Q-factor of the receiver coil, which can result in low power transfer efficiency through the electromagnetic field.

The function of the integrated RFID tags is also validated in saline solution to simulate *in vivo* conditions (Fig. 13). From the aforementioned soak testing results, we can deduce that thicker Parylene films can cover small defects and particles and thus prevent unwanted particle-induced Parylene breakdown.

Fig. 14. Typical SEM image shows Parylene cracks along the edges of the embedded chips after active soak testing.

In this experiment, the integrated device is coated with an additional layer of Parylene C that is approximately 12  $\mu$ m thick and placed in a plastic container filled with saline. The reader module is placed externally with respect to the container and continuously transfers power and data through inductive coupling. The RFID tag is heated in a convection oven at 77 °C, and the signal readout is monitored using a webcam in order to determine the device lifetime. Similar output signal has been observed, indicating the successful power and data transmission in saline. Unfortunately, the devices only functioned for a short time period, and no output could be detected after two to three days of soaking. Parylene microcracks are found along the edges of the embedded chips when examining the failed samples under SEM (Fig. 14). Although the mechanisms that cause these cracks are not entirely understood, it is believed that the coefficient of thermal expansion (CTE) mismatch between the Parylene package (linear CTE of Parylene C  $\sim 10^{-5}/^{\circ}$ C) and the embedded silicon chip (linear CTE of silicon  $\sim 10^{-6}/^{\circ}$ C) plays an important role. Consequently, the Parylene coating is torn from the silicon substrate when the device is heated to 77 °C. In addition, the heat generated during intensive active operation could accumulate due to poor heat dissipation in hot saline, which could possibly result in thermal stress concentration along the edges. More experiments are expected to enable a complete understanding of failure mechanisms and shed insight on methods to mitigate them. Further modifications can include using a thicker Parylene coating combined with epoxy or silicone to smooth out the sharp corners of the chip.

## **IV. CONCLUSION**

Long-term ALST has been done in hot saline, which shows positive results for Parylene-protected metal and Paryleneprotected chips, respectively. A Parylene-based embedded chip integration technology has been developed and successfully demonstrated by integrating a flexible MEMS RF coil with a commercially available read-only RFID chip. The functionality of the embedded chip is validated using an RFID reader module in both air and liquid environments. The preliminary results of active soak testing suggest that the integrated devices can withstand high-temperature soaking with intensive electrical stressing for a few days. Further modifications will be needed in order to improve the reliability and stability of the integrated system. Although specifically tailored to the needs of retinal prostheses, this technology can also be used for other biomedical or IC applications by varying circuitry and passive components to achieve different system functionalities.

### ACKNOWLEDGMENT

The authors would also like to thank T. Roper and other members of the Caltech Micromachining Laboratory for the assistance with fabrication.

#### REFERENCES

- J. F. Rizzo, J. L. Wyatt, J. Loewenstein, S. Montezuma, D. B. Shire, L. Theogarajan, and S. K. Kelly, "Development of a wireless, AB externo retinal prosthesis," *Invest. Ophthalmol. Vis. Sci.*, vol. 45, no. 5, p. 3399, 2004.

- [2] M. Javaheri, D. S. Hahn, R. R. Lakhanpal, J. D. Weiland, and M. S. Humayun, "Retinal prostheses for the blind," *Annu. Acad. Med.*, vol. 35, no. 3, pp. 137–144, Mar. 2006.

- [3] T. Stieglitz, "Development of a micromachined epiretinal vision prosthesis," J. Neural Eng., vol. 6, no. 6, pp. 065 005–065 016, Dec. 2009.

- [4] J. D. Weiland, W. Liu, and M. S. Humayun, "Retinal prosthesis," Annu. Biomed. Eng., vol. 7, no. 1, pp. 361–401, 2005.

- [5] W. Daum, W. E. Burdick, and R. A. Fillion, "Overlay high-density interconnect: A chips-first multichip module technology," *Computer*, vol. 26, no. 4, pp. 23–29, Apr. 1993.

- [6] J. T. Butler, V. M. Bright, and J. H. Comtois, "Multichip module packaging of microelectromechanical systems," *Sens. Actuators A, Phys.*, vol. 70, no. 1/2, pp. 15–22, Oct. 1998.

- [7] Y. Xu, Y.-C. Tai, A. Huang, and C.-M. Ho, "IC-integrated flexible shearstress sensor skin," *J. Microelectromech. Syst.*, vol. 12, no. 5, pp. 740–747, Oct. 2003.

- [8] J.-U. Meyer, T. Stieglitz, O. Scholz, W. Haberer, and H. Beutel, "High density interconnects and flexible hybrid assemblies for active biomedical implants," *IEEE Trans. Adv. Packag.*, vol. 24, no. 3, pp. 366–374, Aug. 2001.

- [9] T. J. Harpster, S. A. Nikles, M. R. Dokmeci, and K. Najafi, "Long-term hermeticity and biological performance of anodically bonded glass-silicon implantable packages," *IEEE Trans. Device Mater. Rel.*, vol. 5, no. 3, pp. 458–466, Sep. 2005.

- [10] D. C. Rodger, J. D. Weiland, M. S. Humayun, and Y. C. Tai, "Scalable high lead-count Parylene package for retinal prostheses," *Sens. Actuators B, Chem.*, vol. 117, no. 1, pp. 107–114, Sep. 2006.

- [11] D. C. Rodger, A. J. Fong, W. Li, H. Ameri, A. K. Ahuja, C. Gutierrez, I. Lavrov, H. Zhong, P. R. Menon, E. Meng, J. W. Burdick, R. R. Roy, V. R. Edgerton, J. D. Weiland, M. S. Humayun, and Y. C. Tai, "Flexible Parylene-based multielectrode array technology for high-density neural stimulation and recording," *Sens. Actuators B, Chem.*, vol. 132, no. 2, pp. 449–460, 2008.

- [12] W. Li, D. C. Rodger, and Y. C. Tai, "Implantable RF-coiled chip packaging," in *Proc. IEEE Int. Conf. MEMS*, Tucson, AZ, 2008, pp. 108–111.

- [13] L. Wolgemuth, "Assessing the performance and suitability of Parylene coating," *Med. Device Diagn. Ind.*, vol. 22, pp. 42–49, 2000.

- [14] J. J. Licari and L. A. Hughes, Handbook of Polymer Coating for Electronics: Chemistry, Technology, and Applications, 2nd ed. Park Ridge, NJ: Noves, 1990.

- [15] U. K. Mudali, T. M. Sridhar, and B. Raj, "Corrosion of bio implants," Sadhana, vol. 28, no. 3/4, pp. 601–637, Jun. 2003.

- [16] W. Li, D. C. Rodger, P. R. Menon, and Y. C. Tai, "Corrosion behavior of Parylene–metal–Parylene thin films in saline," *ECS Trans.*, vol. 11, no. 18, pp. 1–6, 2008.

- [17] W. Li, D. C. Rodger, P. R. Menon, and Y. C. Tai, "Accelerated-lifetime soak testing of Parylene packaging," in *Proc. ACS 235th Nat. Meeting*, New Orlean, LA, 2008.

- [18] Y. C. Tai, F. Jiang, Y. Xu, M. Liger, S. Ho, and C. M. Ho, "Flexible MEMS skins: technologies and applications," presented at the Pacific Rim MEMS Workshop, Xiamen, China, 2002.

- [19] P. R. Menon, W. Li, A. Tooker, and Y. C. Tai, "Characterization of water vapor permeation through thin film Parylene C," in *Proc. Int. Conf. Solid-State Sens., Actuators, Microsyst. TRANSDUCERS*, Denver, CO, 2009, pp. 1892–1895.

- [20] T. Harder, T. J. Yao, Q. He, C. Y. Shih, and Y. C. Tai, "Residual stress in thin-film Parylene C," in *Proc. IEEE Int. Conf. MEMS*, 2002, pp. 435–438.

- [21] H. Noh, P. J. Hesketh, and G. C. Frye-Mason, "Parylene gas chromatographic column for rapid thermal cycling," J. Microelectromech. Syst., vol. 11, no. 6, pp. 718–725, Dec. 2002.

- [22] P. Singh and P. Viswanadham, Failure Modes and Mechanisms in Electronic Packages. New York: Springer-Verlag, 1997.

- [23] S. Ul-Haq and G. Raju, "Breakdown pattern identification in high temperature dielectric films using scanning electron microscopy (SEM)," in *Annu. Rep. CEIDP*, 2003, pp. 265–268.

- [24] O. Akar, T. Akin, and K. Najafi, "A wireless batch sealed absolute capacitive pressure sensor," *Sens. Actuators A, Phys.*, vol. 95, no. 1, pp. 29–38, Dec. 2001.

- [25] F. E. Terman, Radio Engineers' Handbook. New York: McGraw-Hill, 1943.

- [26] T. H. Lee, *The Design of CMOS Radio-Frequency Integrated Circuits*, 2nd ed. New York: Cambridge Univ. Press, 2004.

- [27] P. J. Chen, D. C. Rodger, S. Saati, M. S. Humayun, and Y. C. Tai, "Microfabricated implantable Parylene-based wireless passive intraocular pressure sensors," *J. Microelectromech. Syst.*, vol. 17, no. 6, pp. 1342– 1351, Dec. 2008.

- [28] C. Wu, C. Tang, and S. Liu, "Analysis of on-chip spiral inductors using the distributed capacitance model," *IEEE J. Solid-State Circuits*, vol. 38, no. 6, pp. 1040–1044, Jun. 2003.

- [29] M. Liger, D. C. Rodger, and Y. C. Tai, "Robust Parylene-to-silicon mechanical anchoring," in *Proc. IEEE Int. Conf. MEMS*, Kyoto, Japan, 2003, pp. 602–605.

Wen Li (S'03–M'09) received the B.S. degree in material science and engineering and the M.S. degree in microelectronics from Tsinghua University, Beijing, China, in 2001 and 2003, respectively, and the M.S. and Ph.D. degrees in electrical engineering from the California Institute of Technology, Pasadena, in 2004 and 2008, respectively.

She is currently an Assistant Professor of electrical and computer engineering at the Michigan State University, East Lansing. Her research interests include MEMS/NEMS technologies and systems, microsen-

sors and actuators, biomimetic devices and systems, microfluidic and lab-onchip systems, and microsystem integration and packaging technologies.

Dr. Li is a member of Eta Kappa Nu and the American Chemical Society.

**Damien C. Rodger** (S'97–M'08) received the B.S. degree in electrical engineering (magna cum laude with honors) from Cornell University, Ithaca, NY, in 2000, the Ph.D. degree in bioengineering from the California Institute of Technology, Pasadena, in 2008, and the M.D. degree from the Keck School of Medicine, University of Southern California, Los Angeles, in 2009.

He conducts research on microtechnologies for retinal and spinal cord prostheses and on other novel bioMEMS for ophthalmic use. He will be pursuing a residency in ophthalmology at the Doheny Eye Institute, Los Angeles.

Dr. Rodger was the recipient of a Whitaker Foundation Graduate Fellowship from 2003 to 2006. He is a member of the IEEE Engineering in Medicine and Biology Society and the Association for Research in Vision and Ophthalmology.

Ellis Meng (M'02–SM'09) received the B.S. degree in engineering and applied science and the M.S. and Ph.D. degrees in electrical engineering from the California Institute of Technology (Caltech), Pasadena, in 1997, 1998, and 2003, respectively.

She is currently with the University of Southern California, Los Angeles, where she has been an Assistant Professor in the Department of Biomedical Engineering since 2004, holds a joint appointment in the Ming Hsieh Department of Electrical Engineering, is currently the Thrust Leader for interface

technology with the National Science Foundation Biomimetic MicroElectronic Systems Engineering Research Center, and the Viterbi Early Career Chair in the Viterbi School of Engineering. Her research interests include bioMEMS, implantable biomedical microdevices, microfluidics, multimodality integrated microsystems, and packaging.

Dr. Meng is a member of Tau Beta Pi, the Biomedical Engineering Society, the Society of Women Engineers, and the American Society for Engineering Education. She was the recipient of the Intel Women in Science and Engineering Scholarship, the Caltech Alumni Association Donald S. Clark Award, and a Caltech Special Institute Fellowship. She has also received the NSF CAREER and Wallace H. Coulter Foundation Early Career Translational Research Awards.

James D. Weiland (SM'08) received the B.S. degree, M.S. degree in biomedical engineering, M.S. degree in electrical engineering, and the Ph.D. degree in biomedical engineering from the University of Michigan, Ann Arbor, in 1988, 1993, 1995, and 1997, respectively.

He was with Pratt and Whitney Aircraft Engines for four years. He joined the Wilmer Ophthalmological Institute, The Johns Hopkins University, Baltimore, MD, in 1997 as a Postdoctoral Fellow, where he was appointed an Assistant Professor of

ophthalmology in 1999. He was appointed an Assistant Professor at the Doheny Eye Institute, University of Southern California, Los Angeles, in 2001. He is currently an Associate Professor of ophthalmology and biomedical engineering at the University of Southern California. His research interests include retinal prostheses, neural prostheses, electrode technology, visual evoked responses, and implantable electrical systems.

Dr. Weiland is a member of the IEEE Engineering in Medicine and Biology Society, the Biomedical Engineering Society, Sigma Xi, and the Association for Research in Vision and Ophthalmology.

**Mark S. Humayun** (M'97) received the B.S. degree from Georgetown University, Washington, DC, in 1984, the M.D. degree from Duke University, Durham, NC, in 1989, and the Ph.D. degree from the University of North Carolina, Chapel Hill, in 1994.

He finished his training by completing an ophthalmology residency at Duke University and a fellowship in Vitreoretinal Diseases at Johns Hopkins Hospital. He is currently a Professor of ophthalmology, biomedical engineering, and cell and neurobiology at the University of Southern California,

Los Angeles, where he is the Director of the National Science Foundation Biomimetic MicroElectronic Systems Engineering Research Center. He is also the Director of the Department of Energy Artificial Retina Project that is a consortium of five Department of Energy laboratories and four universities, as well as industry.

Dr. Humayun is a member of the National Academies Institute of Medicine.

**Yu-Chong Tai** (M'97–SM'03–F'06) received the B.S. degree from National Taiwan University, Taiwan, and the M.S. and Ph.D. degrees in electrical engineering from the University of California at Berkeley in 1986 and 1989, respectively.

He developed the first electrically spun polysilicon micromotor at the University of California, Berkeley. He is currently a Professor of electrical engineering, mechanical engineering, and bioengineering at the California Institute of Technology (Caltech), Pasadena. At Caltech, his main research

interest is MEMS for biomedical applications, including lab-on-a-chip and neural implants. He has published more than 300 technical articles in the field of MEMS.

Prof. Tai is the recipient of the IBM Fellowship, the Ross Tucker Award, the Best Thesis Award (at Berkeley), the Presidential Young Investigator Award, the Packard Award, and the ALA Achievement Award.