# Wide-Band Two-Stage GaAs LNA for Radio Astronomy

Jim Kulyk<sup>1</sup>, Ge Wu<sup>2</sup>, Leonid Belostotski<sup>2, \*</sup>, and James W. Haslett<sup>2</sup>

Abstract—This paper presents the design, simulation and measurements of wideband two-stage LNAs using commercially available discrete components and targeting Square Kilometre Array (SKA) focalplane-array verification studies. The design optimization was implemented through simulations based on theoretical work that shows that low wide-band noise figures and power match are achievable by inner-stage component selection and device bias. In contrast to the conventional practice of having each stage of a discrete LNA matched to  $50 \Omega$ , the inner stage was designed with a mismatching capacitor between the two stages. The measured results are presented for 0.7–1.4 GHz and achieve noise figures below 0.4 dB, gain of at least 28 dB, mid-band input return loss of 7 dB, output P1 dB of 18.3 dBm, input-referred IP3 of -15.47 dBm, and power consumption of 500 mW with a supply voltage of 5 V.

# 1. INTRODUCTION

Low noise amplifier (LNA) design typically focuses on obtaining an optimal input admittance to produce a low noise figure over a relatively small bandwidth, usually in the range of ten percent of the operating frequency. In some applications, such as the Square Kilometre Array (SKA) radio telescope initiative [1], the bandwidth requirement is more demanding and involves an operating frequency range of an octave or more. Recent research has demonstrated LNAs with noise figures below 0.4 dB from 0.7 GHz to 1.4 GHz using CMOS technology [2–5]. This paper examines a wideband LNA design that uses off-theshelf Gallium Arsenide (GaAs) transistors. The design optimization is based on the on-chip techniques presented in [6, 7], in which capacitive loading at the output of first stage is used for noise matching the first stage by exploiting the intrinsic gate-drain parasitic capacitance of the transistors.

Section 2 presents an overview of the LNA circuit design. Section 3 discusses the LNA simulation and optimization. Section 4 presents the measured results, and Section 5 provides a summary and conclusion.

## 2. LNA OVERVIEW

The device selected for the two-stage LNA design is the MGA-16516 GaAs MMIC matched-pair dual transistor from Avago Technologies [8]. These components have a small package size and the performance is optimized for the required frequency range. Although these devices have two transistor sections in each device package for balanced amplifier applications, only one transistor from each package was used in the two-stage design to improve layout efficiency and to minimize interference with the radio frequency (RF) signal path. The LNAs are constructed on low-loss PCB material.

The MGA-16516 has an optimum operational frequency range of 500 MHz to 1.7 GHz. The manufacturer's data sheet [8] reports a noise figure of 0.4 dB (typical) at 850 MHz with a 5 V supply, while drawing 50 mA for a single transistor. The gate bias voltage is 0.48 V (typical).

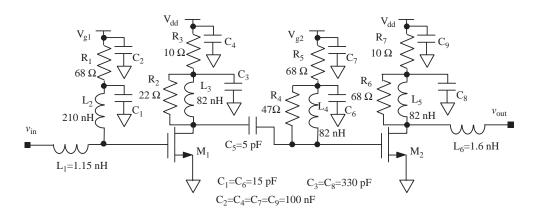

The circuit schematic for the proposed two-stage LNA is shown in Fig. 1. The input inductor,  $L_1$ , is a high Q inductor, which minimizes signal loss, resistive thermal noise, and contributes to the LNA

Received 15 January 2015, Accepted 13 February 2015, Scheduled 19 February 2015

<sup>\*</sup> Corresponding author: Leonid Belostotski (lbelosto@ucalgary.ca).

<sup>&</sup>lt;sup>1</sup> Kulyk Engineering, Canada. <sup>2</sup> Department of Electrical and Computer Engineering, University of Calgary, Canada.

Figure 1. Two-stage LNA schematic.

input match along with RF choke inductor,  $L_2$ , and capacitor  $C_1$ . Resistor  $R_1$  provides RF filtering, circuit stability, and a DC path for gate bias. Capacitors  $C_2$ ,  $C_4$ ,  $C_7$ , and  $C_9$  are large and decouple high-frequency signals and noise at the DC inputs for supply and gate bias voltages. Inductor  $L_3$  is an RF choke and together with capacitor  $C_3$ , provides output matching for the first stage. Resistor  $R_2$  is required for circuit stability and contributes to the first-stage output match. Resistor  $R_3$  provides RF filtering and a DC path for the supply voltage.

Capacitor  $C_5$  provides DC blocking between stages and is the main tuning component for the LNA noise figure and input return loss. Because the transistors are not unilateral, tuning  $C_5$  modifies the LNA input impedance but does not affect the LNA optimum impedance for minimum noise. Therefore, it is possible to use  $L_1$ ,  $L_2$ , and  $C_1$  for noise matching the LNA and tuning  $C_5$  to achieve reasonable input power match. Therefore,  $C_5$  allows the de-coupling between input power match and noise match. For a wide-band design, the LNA is optimized so that its noise figure (NF) approaches the minimum noise figure (NFmin) at the upper frequency band edge [5]. Inductor  $L_4$ , capacitor  $C_6$ , and resistor  $R_4$ control second-stage input match. Resistors  $R_4$  and  $R_5$  increase circuit stability and provide a DC path for gate bias. The second-stage output RF choke inductor,  $L_5$ , capacitor  $C_8$ , resistor  $R_6$ , and output inductor,  $L_6$ , control the output match for the LNA. Resistor  $R_6$  also serves to improve stability of the output stage. Resistor  $R_7$  provides RF filtering and a DC path for the second-stage supply voltage.

The PCB material is an important design choice and has a significant effect on LNA noise figure performance. Dissipative signal loss at the input sections of the PCB layout directly increases the noise figure and cannot be corrected in later stages of amplification. Rogers Corporation RO4003C material was selected for its low-loss characteristics and standard fabrication process. Electromagnetic (EM) simulation of the PCB material and layout was implemented using Momentum, a 2.5D EM simulator from Keysight. The EM simulation provided S-parameter data files that were used in the circuit simulation of the LNA designs.

#### **3. CIRCUIT SIMULATION**

The two-stage wideband LNA design was optimized using circuit simulation, which included vendorsupplied S-parameter data for the active and passive devices as well as the EM-simulated PCB sections. Keysight ADS simulation software was used to optimize noise figure, input and output return loss, forward gain, and circuit stability. Following the techniques described in [6, 7, 9], the noise figure performance at the high band edge (1.4 GHz) was optimized to obtain the best NF. Some attention was also given to the LNA input return loss across the operational frequency range to keep it as high as possible without affecting NF. Since for the intended application in an SKA focal-plane array, the antennas are designed to match the LNAs, the return loss of the LNA is not as critical as NF.

Simulation of the two-stage wideband LNA began by making the first stage and second stage stable. The first stage and second-stage sections were simulated independently to achieve stable operation before combining the two stages to optimize NF, input reflection coefficient  $(S_{11})$ , output return loss  $(S_{22})$ , and

#### Progress In Electromagnetics Research C, Vol. 56, 2015

| Frequency     | $700\mathrm{MHz}$ | $1.1\mathrm{GHz}$ | $1.4\mathrm{GHz}$ |

|---------------|-------------------|-------------------|-------------------|

| $S_{11}$ [dB] | -5.11             | -7.57             | -7.46             |

| $S_{21}$ [dB] | 32.22             | 30.81             | 29.06             |

| $S_{12}$ [dB] | -69.79            | -59.56            | -54.61            |

| S22 [dB]      | -12.57            | -12.73            | -10.62            |

| NF [dB]       | 0.53              | 0.49              | 0.53              |

| NFmin [dB]    | 0.50              | 0.47              | 0.50              |

Table 1. Two-stage LNA simulated S-parameters and noise figure.

forward gain  $(S_{21})$ . The S-parameter and noise-parameter data for the MGA-16516 were available for a bias range from  $3 \vee 0.50 \text{ mA}$  to  $5 \vee 0.60 \text{ mA}$ . The bias condition that provided the best minimum noise figure,  $5 \vee 0.50 \text{ mA}$ , was used for simulation. The simulated S-parameters, noise figure, and NFmin of the two-stage wideband LNA are shown in Table 1.

# 4. MEASURED RESULTS

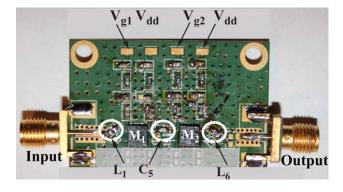

Two test boards for the wideband LNA were constructed and identified as Brd1 and Brd2. A photograph of the LNA is shown in Fig. 2. Test board Brd1 was modified by mechanically removing the solder mask along the RF signal path. Test board Brd2 was unaltered. The test boards did not have shielding and the circuitry was exposed to free space and inevitable interference.

Noise figure measurements were conducted in a shielded room at ambient with a Keysight N8973A Noise Figure Analyzer and N4000A Noise Source. The same N4000A Noise Source was used for all noise figure measurements to eliminate calibration variability. The LNA circuits present DC voltages at the input and output connectors and high-frequency DC blocking capacitors were used to prevent instrument damage during measurements. The losses associated with the DC blocking capacitors and test cables were de-embedded.

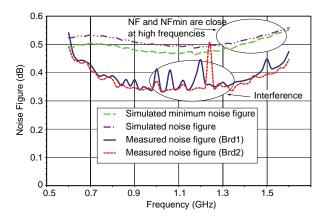

The two-stage wideband LNA simulated and measured NFs for Brd1 and Brd2 are shown in Fig. 3. The simulated NF and NFmin are similar in value near the high end of the frequency range, as desirable for wideband LNA noise matching, and are both higher than the measured NF (solid and dashed lines in the middle of the chart). Vendor-supplied noise parameters are dependent on measurement techniques and calibration accuracy and may result in conservative simulated noise figure performance as indicated by measured results.

The RF input and output connectors used in the LNA designs are SMA PCB edge-mount connectors. The SMA connector-to-PCB microstrip trace transition requires full 3D simulation to

Figure 2. Fabricated wideband LNA.

Figure 3. Two-stage LNA simulated and measured noise figures for test Brd1 and Brd2.

develop an accurate model. Instead, a direct measurement of the SMA/PCB transition was made using a test board and a Vector Signal Analyzer (VNA). A calibrated coaxial cable extension was soldered to the input pad of inductor  $L_1$  and the signal loss was measured from the input SMA connector to the inductor pad. The same procedure was used to measure the output inductor-pad-to-SMA-connector signal loss. The measurements showed that a significant amount (~0.1 dB) of noise is contributed by the input SMA and the PCB microstrip to the LNA noise.

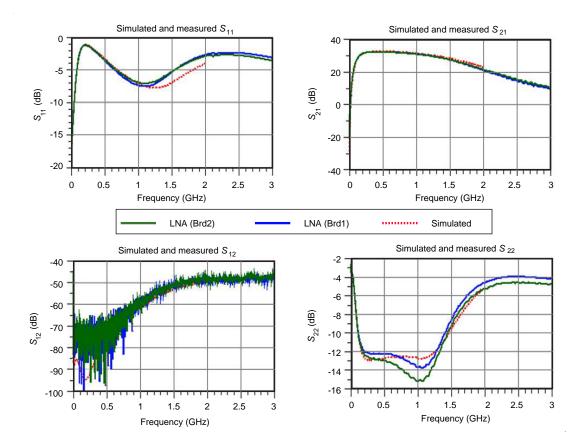

The two-stage wideband LNA simulated and measured S-parameters for Brd1 and Brd2 are shown in Fig. 4. In general, there is good agreement between simulated (dotted lines) and measured parameters.

Figure 4. Two-stage LNA simulated and measured S-parameters.

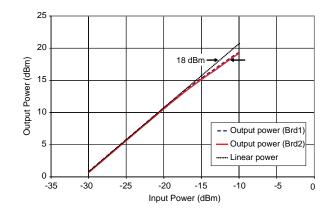

Figure 5. Two-stage LNA measured P1 dB at 1.1 GHz.

| Frequency          | $700\mathrm{MHz}$ |       | $1.1\mathrm{GHz}$ |             | $1.4\mathrm{GHz}$ |       |

|--------------------|-------------------|-------|-------------------|-------------|-------------------|-------|

|                    | Brd1              | Brd2  | Brd1              | Brd2        | Brd1              | Brd2  |

| $S_{11}$ (dB)      | -5.56             | -5.28 | -7.54             | -7.08       | -6.08             | -5.89 |

| $S_{21}$ (dB)      | 31.9              | 31.7  | 30.4              | 30.3        | 28.3              | 28.2  |

| $S_{12}$ (dB)      | -65.6             | -63.5 | -57.3             | -57.9       | -51.9             | -53.0 |

| $S_{22}$ (dB)      | -12.5             | -13.6 | -13.6             | -14.9       | -10.1             | -10.8 |

| NF (dB)            | 0.43              | 0.42  | 0.35              | 0.35        | 0.37              | 0.36  |

| $NF (dB)^{(1)}$    | 0.34              | 0.33  | 0.25              | 0.24        | 0.26              | 0.25  |

| P1dB (dBm)         | -                 | -     | 18.3              | 18.0        | -                 | -     |

| IIP3 $(dBm)^{(2)}$ | -                 | -     | -7.10             | -7.08       | -                 | -     |

| Power (W)          |                   |       | $0.5^{(3)}$       | $0.5^{(3)}$ |                   |       |

Table 2. Two-stage LNA measured results.

(1). Input SMA connector and PCB trace de-embedded.

(2). Average of the lower- and upper-band IP3 levels referred to the DUT input.

(3). Supply voltage of 5 V and total current draw of 100 mA for two stages with gate voltage  $V_{G1} = 0.47$  V and  $V_{G2} = 0.48$  V.

Table 3. Comparison with discrete LNAs designed for SKA and a commercial amplifier.

| Specifications              | This work | [12]  | [13]      | [14]      |

|-----------------------------|-----------|-------|-----------|-----------|

| Bandwidth (GHz)             | 0.7 - 1.4 | 1 - 2 | 0.7 - 1.8 | 1-2       |

| Min. Gain (dB)              | 28        | 42    | 28        | 45        |

| Max. Noise Temperature (K)  | 29        | 39    | 39        | 29        |

| Min. Noise Temperature (K)  | 16        | 30    | 33        | -         |

| Power consumption (W)       | 0.5       | -     | -         | 2.7       |

| Input IP3 (dBm)             | -7        | -17   | -         | $-22^{*}$ |

| Min. Input return loss (dB) | 5         | 7.5   | 6         | 10        |

\*Estimated from output P1 dB

The differences can be attributed to EM simulation accuracy and input-connector measurement errors. The measured results for the two test boards show very consistent performance. This validates the repeatability of the design.

The measured P1 dB results for Brd1 and Brd2 are shown in Fig. 5. The measurements were taken at mid-band, 1.1 GHz. The input-referred third-order intermodulation product levels, IIP3, were also measured at the mid-band frequency of 1.1 GHz. The two tones were spaced 1 MHz apart. The power level was -43 dBm per tone. The measured results are shown in Table 2.

Table 3 summarizes the LNA performance and presents measurement results for other LNAs targetting SKA specifications and one commercial amplifier. The presented LNA achieves lower noise figures than other discrete LNAs and therefore two such LNAs have been installed in one of the 7 Synthesis Telescope antennas operated by the Dominion Radio Astrophysical Observatory (DRAO), National Research Council of Canada. The same LNAs but on a slightly modified PCB have also been used in an Advanced Phased-Array Feed designed by DRAO [10, 11].

### 5. CONCLUSION

The simulated and measured results for two wideband LNAs have been presented. The LNAs used inter-stage mismatch to decouple input noise matching from power matching. The LNAs display low noise, an octave bandwidth, good input return loss, high gain, and moderate power consumption. The presented LNA achieves lower noise figures than other discrete LNAs designed for the same application.

### REFERENCES

- 1. Dewdney, P. E., et al., "The square kilometre array," *Proceedings of the IEEE*, Vol. 97, 1482–1496, 2009.

- 2. Belostotski, L., "Comparison of LNAs fabricated in 65-nm CMOS GP and LP processes for the square kilometre array," *IEICE Electronic Express*, Vol. 9, 636–641, Apr. 2012.

- Belostotski, L. and J. W. Haslett, "Sub-0.2 dB noise figure wideband room-temperature CMOS LNA with non-50 Ω signal-source impedance," *IEEE J. Solid-State Circuits*, Vol. 42, 2492–2502, Nov. 2007.

- 4. Belostotski, L., et al., "The first CMOS LNA on a radio telescope," *IEEE International Symposium* on Antenna Technology and Applied Electromagnetics, 1–3, 2014,

- Belostotski, L. and J. W. Haslett, "Wide band room temperature 0.35-dB noise figure LNA in 90-nm bulk CMOS," *IEEE Radio and Wireless Symposium*, 221–224, Long Beach, 2007.

- Hu, R., "An 8–20-GHz wide-band LNA design and the analysis of its input matching mechanism," IEEE Microwave and Wireless Components Letters, Vol. 14, 528–530, 2004.

- Belostotski, L., J. W. Haslett, and B. Veidt, "Wide-band CMOS low noise amplifier for applications in radio astronomy," *IEEE International Symposium on Circuits and Systems*, 1347–1350, Kos, Greece, 2006.

- 8. Avago Technologies, "MGA-16516 low noise, high linearity match pair low noise amplifier," AV02-1980EN Data Sheet, Jul. 7, 2009.

- 9. Belostotski, L. and J. W. Haslett, "Noise figure optimization of wide-band inductively-degenerated CMOS LNAs," *IEEE Midwest Symposium on Circuits and Systems*, 1002–1005, Montreal, 2007.

- Veidt, B., et al., "Development of a low-noise wide-band phased-array feed," URSI General Assembly and Scientific Symposium, 1–4, 2011.

- Gray, A. D., et al., "Activities of the Dominion radio astrophysical observatory," URSI General Assembly and Scientific Symposium, 1–4, 2011.

- De Vaate, J. G. B., et al., "Low cost low noise phased-array feeding systems for SKA pathfinders," International Symposium on Antenna Technology and Applied Electromagnetics and the Canadian Radio Science Meeting, 1–4, 2009.

- Bhaumik, S. and D. George, "Review of square kilometre array LNA technologies and topologies," Wide Field Astronomy & Technology for the Square Kilometre Array, 279–282, Chateau de Limelette, Belgium, 2009.

- 14. Miteq, AMF-3F-01000200-04-13P Datasheet, Online.