# Wide Bandgap Semiconductor Based Micro/Nano Devices

Edited by Jung-Hun Seo Printed Edition of the Special Issue Published in *Micromachines*

www.mdpi.com/journal/micromachines

# Wide Bandgap Semiconductor Based Micro/Nano Devices

## Wide Bandgap Semiconductor Based Micro/Nano Devices

Special Issue Editor Jung-Hun Seo

MDPI • Basel • Beijing • Wuhan • Barcelona • Belgrade

Special Issue Editor Jung-Hun Seo University at Buffalo, the State University of New York USA

Editorial Office MDPI St. Alban-Anlage 66 4052 Basel, Switzerland

This is a reprint of articles from the Special Issue published online in the open access journal *Micromachines* (ISSN 2072-666X) from 2018 to 2019 (available at: https://www.mdpi.com/journal/micromachines/special\_issues/Semiconductor\_Materials\_Micro\_nano\_Devices)

For citation purposes, cite each article independently as indicated on the article page online and as indicated below:

LastName, A.A.; LastName, B.B.; LastName, C.C. Article Title. *Journal Name* Year, Article Number, Page Range.

ISBN 978-3-03897-842-8 (Pbk) ISBN 978-3-03897-843-5 (PDF)

© 2019 by the authors. Articles in this book are Open Access and distributed under the Creative Commons Attribution (CC BY) license, which allows users to download, copy and build upon published articles, as long as the author and publisher are properly credited, which ensures maximum dissemination and a wider impact of our publications.

The book as a whole is distributed by MDPI under the terms and conditions of the Creative Commons license CC BY-NC-ND.

### Contents

| About the Special Issue Editor                                                                                                                                                                                                                                                                                                                        | vii |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Jung-Hun Seo<br>Editorial for the Special Issue on Wide Bandgap Semiconductor Based Micro/Nano Devices<br>Reprinted from: <i>Micromachines</i> <b>2019</b> , <i>10</i> , 213, doi:10.3390/mi10030213                                                                                                                                                  | 1   |

| Guanguang Zhang, Kuankuan Lu, Xiaochen Zhang, Weijian Yuan, Muyang Shi,<br>Honglong Ning, Ruiqiang Tao, Xianzhe Liu, Rihui Yao and Junbiao Peng<br>Effects of Annealing Temperature on Optical Band Gap of Sol-gel Tungsten Trioxide Films                                                                                                            |     |

| Reprinted from: <i>Micromachines</i> 2018, 9, 377, doi:10.3390/mi9080377                                                                                                                                                                                                                                                                              | 4   |

| <ul> <li>Yanrong Li</li> <li>An Improved Large Signal Model for 0.1 μm AlGaN/GaN High Electron Mobility Transistors (HEMTs) Process and Its Applications in Practical Monolithic Microwave Integrated Circuit (MMIC) Design in W band</li> <li>Reprinted from: <i>Micromachines</i> 2018, 9, 396, doi:10.3390/mi9080396</li> </ul>                    | 13  |

| Wojciech Wojtasiak, Marcin Góralczyk, Daniel Gryglewski, Marcin Zajac, Robert Kucharski,<br>Paweł Prystawko, Anna Piotrowska, Marek Ekielski, Eliana Kamińska, Andrzej Taube,<br>Marek Wzorek<br>AlGaN/GaN High Electron Mobility Transistors on Semi-Insulating Ammono-GaN Substrates                                                                |     |

| with Regrown Ohmic Contacts Reprinted from: <i>Micromachines</i> 2018, 9, 546, doi:10.3390/mi9110546                                                                                                                                                                                                                                                  | 25  |

| <b>Shuman Mao and Yuehang Xu</b><br>Investigation on the I–V Kink Effect in Large Signal Modeling of AlGaN/GaN HEMTs<br>Reprinted from: <i>Micromachines</i> <b>2018</b> , <i>9</i> , 571, doi:10.3390/mi9110571                                                                                                                                      | 39  |

| Hujun Jia, Mei Hu and Shunwei Zhu<br>An Improved UU-MESFET with High Power Added Efficiency<br>Reprinted from: <i>Micromachines</i> 2018, 9, 573, doi:10.3390/mi9110573                                                                                                                                                                               | 50  |

| <b>Myeongsun Kim, Jongmin Ha, Ikhyeon Kwon, Jae-Hee Han, Seongjae Cho and Il Hwan Cho</b><br>A Novel One-Transistor Dynamic Random-Access Memory (1T DRAM) Featuring Partially<br>Inserted Wide-Bandgap Double Barriers for High-Temperature Applications<br>Reprinted from: <i>Micromachines</i> <b>2018</b> , <i>9</i> , 581, doi:10.3390/mi9110581 | 55  |

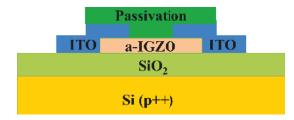

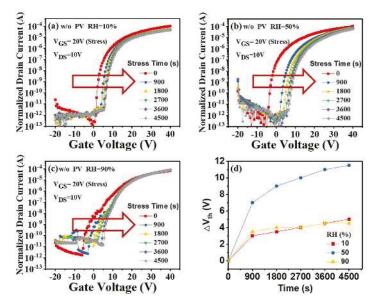

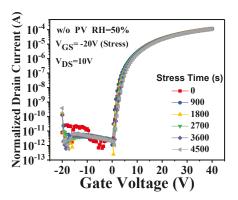

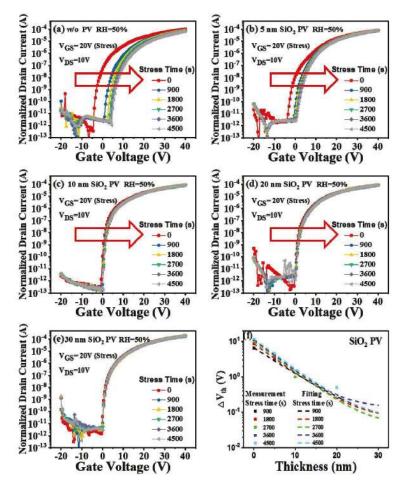

| Yan Zhou and Chengyuan Dong<br>Influence of Passivation Layers on Positive Gate Bias-Stress Stability of Amorphous InGaZnO<br>Thin-Film Transistors<br>Reprinted from: <i>Micromachines</i> 2018, 9, 603, doi:10.3390/mi9110603                                                                                                                       | 64  |

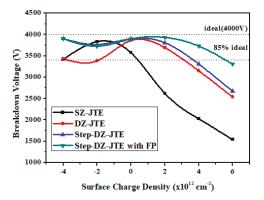

| Yifei Huang, Ying Wang, Xiaofei Kuang, Wenju Wang, Jianxiang Tang and Youlei Sun<br>Step-Double-Zone-JTE for SiC Devices with Increased Tolerance to JTE Dose and<br>Surface Charges<br>Reprinted from: <i>Micromachines</i> 2018, 9, 610, doi:10.3390/mi9120610                                                                                      | 72  |

### About the Special Issue Editor

Jung-Hun Seo received his BS degree in electronics and electrical engineering from Korea University, Seoul, Republic of Korea, in 2006. He received his MS and PhD degrees in Electrical and Computer Engineering from University of Wisconsin-Madison in 2011 and 2015, respectively. Since 2016, he has been an assistant professor at the Department of Materials Design and Innovation, University at Buffalo, the state university of New York. He is the author or coauthor of more than 80 peer-reviewed papers, book chapters, and patents. His research interests mainly focus on the synthesis of low dimensional wide bandgap semiconductors toward high performance flexible electronics and optoelectronics. Also, he is working on various high frequency and high power devices based on wide bandgap semiconductors.

### **Editorial Editorial for the Special Issue on Wide Bandgap Semiconductor Based Micro/Nano Devices**

### Jung-Hun Seo

Department of Materials Design and Innovation, University at Buffalo, The State University of New York, Buffalo, NY 14260, USA; junghuns@buffalo.edu

Received: 20 March 2019; Accepted: 25 March 2019; Published: 26 March 2019

While conventional group IV or III-V based device technologies have reached their technical limitations (e.g., limited detection wavelength range or low power handling capability), wide bandgap (WBG) semiconductors which have band-gaps greater than 3 eV have gained significant attention in recent years as a key semiconductor material in high-performance optoelectronic and electronic devices [1,2]. These WBG semiconductors have various definitive advantages for optoelectronic and electronic applications due to their large bandgap energy. WBG energy is suitable to absorb or emit ultraviolet (UV) light in optoelectronic devices [3]. It also provides a higher electric breakdown field, which allows electronic devices to possess higher breakdown voltages [4].

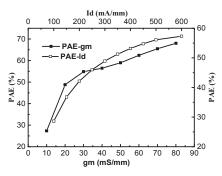

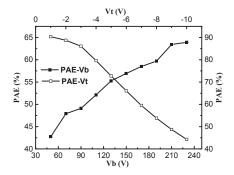

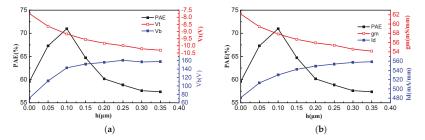

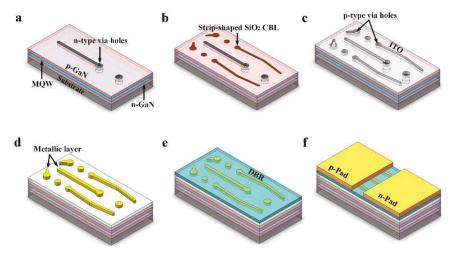

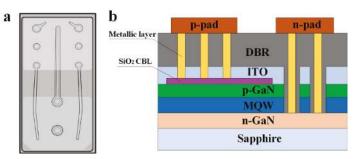

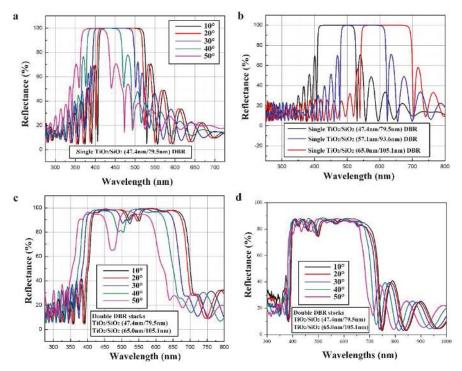

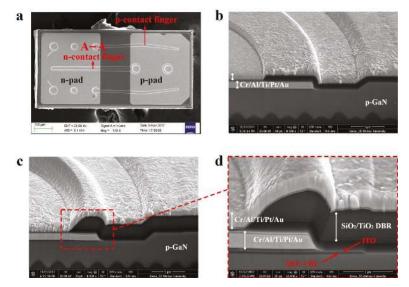

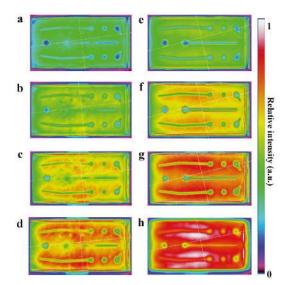

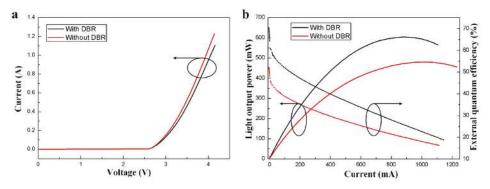

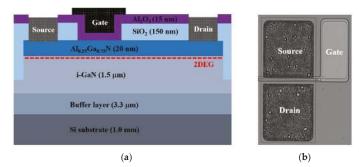

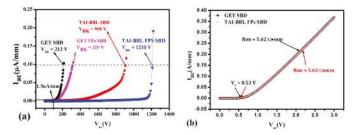

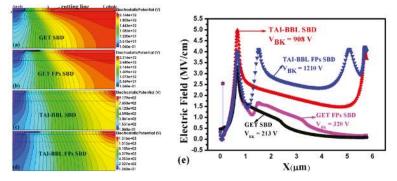

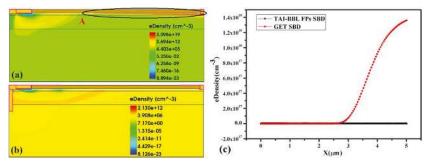

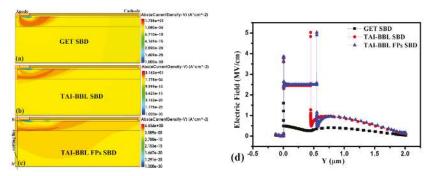

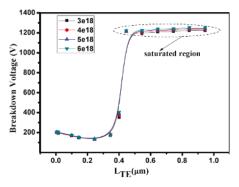

In this Special Issue, 13 papers published, including various AlGaN/GaN, SiC, and WO<sub>3</sub> based devices. More than half of papers reported recent progress on AlGaN/GaN high electron mobility transistors (HEMTs) and light emitting diodes (LEDs). Wojtasiak et al., and Sun et al, reported a structural modification of AlGaN/GaN HEMTs to improve turn-on voltage, contact resistance, and on-resistance [5]. Huang et al. investigated high-temperature characteristics of AlGaN/GaN HEMTs and successfully established the thermal model [6]. Mao et al. and Li et al. simulated AlGaN/GaN HEMTs with a large signal model to investigate the kink-effect [7,8]. All of these efforts toward AlGaN/GaN HEMTs enable readers to understand current issues in AlGaN/GaN HEMTs and offer various experimental and theoretical solutions. Beside transistor works, flip-chip GaN LEDs that were combined with TiO<sub>2</sub>/SiO<sub>2</sub> distributed Bragg reflectors (DBRs) was reported by Zhou et al [9]. An improved GaN HEMTs and their microwave performance by employing the asymmetric power-combining was reported by Kim et al [10]. Along with another GaN LED built on a modified micron-size patterned sapphire substrate by Hsu et al. [11]. These GaN LED works are also guided broad readers in the field of optoelectronics and biomedical areas toward future high-performance optogenetics and photonics applications. Also, Sun et al. reported an enhanced AlGaN/GaN Schottky Barrier by engineering the structure of the diode [12].

In addition to AlxGa1-xN system, two SiC simulation efforts have been made by Huang et al. and Jia et al. Huang. They focused on the improvement of higher added efficiency (PAE) factor in 4H-SiC metal semiconductor field effect transistors and breakdown voltage of 4H-SiC diodes, respectively [13,14].

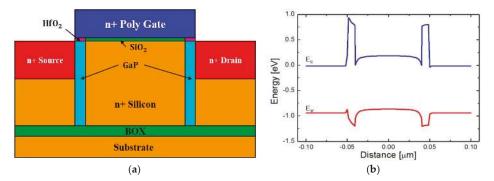

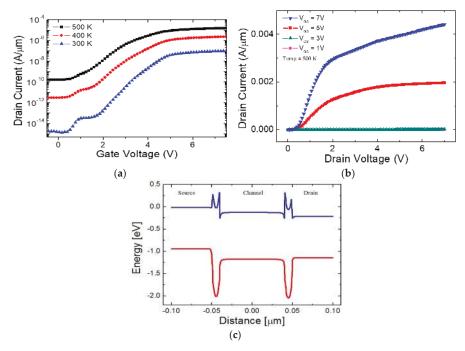

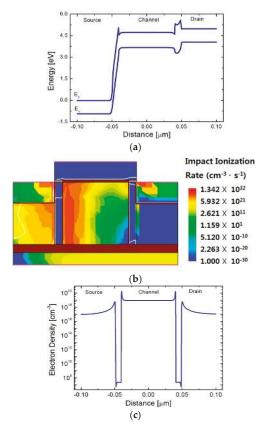

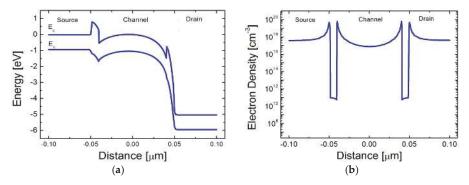

Besides popular AlxGa1-xN and SiC-based applications, three papers report InGaZnO thin-film transistors (TFTs), Si/GaP one-transistor dynamic random-access memory (1T DRAM), and WO<sub>3</sub> thin-film. Zhou et al. investigated a stress tolerance of InGaZnO TFTs with a SiO<sub>2</sub> or Al<sub>2</sub>O<sub>3</sub> passivation layer which shows a stable positive bias during the operation [15]. Kim et al. simulated a novel 1T DRAM design by inserting a GaP pillar which showed a stable high-temperature operation [16]. Finally, Zhang et al. reported the changes of the optical bandgap in Tungsten trioxide by thermal annealing which can be used for various electrochromic devices [17].

To the end, I would like to take this opportunity to thank all the authors for submitting their papers to this special issue. I also want to thank all the reviewers for dedicating their time and helping to improve the quality of the submitted papers.

### References

- Kim, M.; Seo, J.-H.; Singisetti, U.; Ma, Z. Recent advances in free-standing single crystalline wide band-gap semiconductors and their applications: GaN, SiC, ZnO, β-Ga<sub>2</sub>O<sub>3</sub>, and diamond. *J. Mater. Chem. C* 2017, *5*, 8338–8354. [CrossRef]

- Swinnich, E.; Dave, Y.J.; Pitman, E.B.; Broderick, S.; Mazumder, B.; Seo, J.-H. Prediction of optical band gap of β-(Al<sub>x</sub>Ga<sub>1-x</sub>)<sub>2</sub>O<sub>3</sub> using material informatics. *Mater. Discov.* 2018, 11, 1–5. [CrossRef]

- Liu, D.; Cho, S.J.; Park, J.; Gong, J.; Seo, J.-H.; Dalmau, R.; Zhao, D.; Kim, K.; Kim, M.; Kalapala, A.R.K.; et al. 226 nm AlGaN/AlN UV LEDs using p-type Si for hole injection and UV reflection. *Appl. Phys. Lett.* 2018, 113, 011111. [CrossRef]

- Swinnich, E.; Hasan, M.N.; Zeng, K.; Dove, Y.; Singisetti, U.; Mazumder, B.; Seo, J.-H. Flexible β-Ga<sub>2</sub>O<sub>3</sub> Nanomembrane Schottky Barrier Diodes. *Adv. Electron. Mater.* 2019, 5, 1800714. [CrossRef]

- Wojtasiak, W.; Góralczyk, M.; Gryglewski, D.; Zając, M.; Kucharski, R.; Prystawko, P.; Piotrowska, A.; Ekielski, M.; Kamińska, E.; Taube, A.; et al. AlGaN/GaN High Electron Mobility Transistors on Semi-Insulating Ammono-GaN Substrates with Regrown Ohmic Contacts. *Micromachines* 2018, 9, 546. [CrossRef] [PubMed]

- Huang, H.; Li, F.; Sun, Z.; Cao, Y. Model Development for Threshold Voltage Stability Dependent on High Temperature Operations in Wide-Bandgap GaN-Based HEMT Power Devices. *Micromachines* 2018, 9, 658. [CrossRef] [PubMed]

- Mao, S.; Xu, Y. Investigation on the I–V Kink Effect in Large Signal Modeling of AlGaN/GaN HEMTs. Micromachines 2018, 9, 571. [CrossRef] [PubMed]

- Li, J.; Mao, S.; Xu, Y.; Zhao, X.; Wang, W.; Guo, F.; Zhang, Q.; Wu, Y.; Zhang, B.; Chen, T.; et al. An Improved Large Signal Model for 0.1 μm AlGaN/GaN High Electron Mobility Transistors (HEMTs) Process and Its Applications in Practical Monolithic Microwave Integrated Circuit (MMIC) Design in W band. *Micromachines* 2018, 9, 396. [CrossRef] [PubMed]

- Zhou, S.; Xu, H.; Liu, M.; Liu, X.; Zhao, J.; Li, N.; Liu, S. Effect of Dielectric Distributed Bragg Reflector on Electrical and Optical Properties of GaN-Based Flip-Chip Light-Emitting Diodes. *Micromachines* 2018, 9, 650. [CrossRef] [PubMed]

- Kim, S.; Lee, M.-P.; Hong, S.-J.; Kim, D.-W. Ku-Band 50 W GaN HEMT Power Amplifier Using Asymmetric Power Combining of Transistor Cells. *Micromachines* 2018, *9*, 619. [CrossRef] [PubMed]

- Hsu, W.-Y.; Lian, Y.-C.; Wu, P.-Y.; Yong, W.-M.; Sheu, J.-K.; Lin, K.-L.; Wu, Y.S. Suppressing the initial growth of sidewall GaN by modifying micron-sized patterned sapphire substrate with H<sub>3</sub>PO<sub>4</sub>-based etchant. *Micromachines* 2018, 9, 622. [CrossRef] [PubMed]

- Sun, Y.; Wang, Y.; Tang, J.; Wang, W.; Huang, Y.; Kuang, X. A Breakdown Enhanced AlGaN/GaN Schottky Barrier Diode with the T-Anode Position Deep into the Bottom Buffer Layer. *Micromachines* 2019, 10, 91. [CrossRef] [PubMed]

- Huang, Y.; Wang, Y.; Kuang, X.; Wang, W.; Tang, J.; Sun, Y. Step-Double-Zone-JTE for SiC Devices with Increased Tolerance to JTE Dose and Surface Charges. *Micromachines* 2018, 9, 610. [CrossRef] [PubMed]

- Jia, H.; Hu, M.; Zhu, S. An Improved UU-MESFET with High Power Added Efficiency. *Micromachines* 2018, 9, 573. [CrossRef] [PubMed]

- 15. Zhou, Y.; Dong, C. Influence of Passivation Layers on Positive Gate Bias-Stress Stability of Amorphous InGaZnO Thin-Film Transistors. *Micromachines* **2018**, *9*, 603. [CrossRef] [PubMed]

- Kim, M.; Ha, J.; Kwon, I.; Han, J.-H.; Cho, S.; Cho, I. A Novel One-Transistor Dynamic Random-Access Memory (1T DRAM) Featuring Partially Inserted Wide-Bandgap Double Barriers for High-Temperature Applications. *Micromachines* 2018, 9, 581. [CrossRef] [PubMed]

- Zhang, G.; Lu, K.; Zhang, X.; Yuan, W.; Shi, M.; Ning, H.; Tao, R.; Liu, X.; Yao, R.; Peng, J. Effects of Annealing Temperature on Optical Band Gap of Sol-gel Tungsten Trioxide Films. *Micromachines* 2018, 9, 377. [CrossRef] [PubMed]

© 2019 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Article

### **Effects of Annealing Temperature on Optical Band Gap of Sol-gel Tungsten Trioxide Films**

### Guanguang Zhang, Kuankuan Lu, Xiaochen Zhang, Weijian Yuan, Muyang Shi, Honglong Ning \*, Ruiqiang Tao, Xianzhe Liu, Rihui Yao \* and Junbiao Peng

Institute of Polymer Optoelectronic Materials and Devices, State Key Laboratory of Luminescent Materials and Devices, South China University of Technology, Guangzhou 510640, China; msgg-zhang@mail.scut.edu.cn (G.Z.); mskk-lu@mail.scut.edu.cn (K.L.); mszhang\_xc@mail.scut.edu.cn (X.Z.); 201430320366@mail.scut.edu.cn (W.Y.); 201430320229@mail.scut.edu.cn (M.S.); 201510102158@mail.scut.edu.cn (R.T.); msliuxianzhe@mail.scut.edu.cn (X.L.); psjbpeng@scut.edu.cn (J.P.) \* Correspondence: ninghl@scut.edu.cn (H.N.); yaorihui@scut.edu.cn (R.Y.); Tel.: +86-20-8711-4525 (H.N.)

Received: 6 July 2018; Accepted: 25 July 2018; Published: 30 July 2018

**Abstract:** Tungsten trioxide (WO<sub>3</sub>) is a wide band gap semiconductor material that is used as an important electrochromic layer in electrochromic devices. In this work, the effects of the annealing temperature on the optical band gap of sol-gel WO<sub>3</sub> films were investigated. X-ray Diffraction (XRD) showed that WO<sub>3</sub> films were amorphous after being annealed at 100 °C, 200 °C and 300 °C, respectively, but became crystallized at 400 °C and 500 °C. An atomic force microscope (AFM) showed that the crystalline WO<sub>3</sub> films were rougher than the amorphous WO<sub>3</sub> films (annealed at 200 °C and 300 °C). An ultraviolet spectrophotometer showed that the optical band gap of the WO<sub>3</sub> films decreased from 3.62 eV to 3.30 eV with the increase in the annealing temperature. When the Li<sup>+</sup> was injected into WO<sub>3</sub> film in the electrochromic reaction, the optical band gap of the WO<sub>3</sub> films decreased. The correlation between the optical band gap and the electrical properties of the WO<sub>3</sub> films was found in the electrochromic test by analyzing the change in the response time and the current density. The decrease in the annealing temperature.

Keywords: optical band gap; tungsten trioxide film; annealing temperature; electrochromism

### 1. Introduction

Tungsten trioxide (WO<sub>3</sub>) is an important indirect band gap semiconductor material [1]. It is used as a functional layer in the applications of gas sensors [2], photocatalysis [3], solar cells [4], water splitting [5] and electrochromism [6]. Electrochromic devices, such as smart windows [7], can meet the market demand of energy-saving devices. Since WO<sub>3</sub>'s electrochromic properties were found, researchers have widely studied WO<sub>3</sub>-based electrochromic thin films and device applications [8].

There are various choices for preparing WO<sub>3</sub> films with the development of thin film technology. These include sputtering [9], chemical vapor deposition [10], vacuum evaporation [11], and sol-gel [12], among others. Currently, magnetron sputtering is a commercial technology that is used to prepare WO<sub>3</sub> films due to its uniformity of film and reliability. However, the high cost issue and problems in preparing large-size devices cannot be ignored. The sol-gel method is a feasible technology for reducing the cost even, though there are still some problems at the present stage, such as film inhomogeneity and poor process repeatability, among others. With the development of new sol-gel techniques, such as inkjet printing [13], sol-gel technology is promising for commercial applications in the future.

The optical and electrical properties of  $WO_3$  film are related to the parameters of the sol-gel technique, such as the solvent [14], precursor [15] and annealing temperature [16], among others.

In previous work, there was a significant difference in the band gap of the WO<sub>3</sub> films obtained using different processes [17,18]. Therefore, it is worthwhile to launch further investigations into the relationship between band gap and the optical and electrical properties of WO<sub>3</sub> films, especially in regards to electrochromic properties. In this paper, we conducted a study on the optical band gap of WO<sub>3</sub> films with different annealing temperatures. The crystallinity, response time morphology and conductivity were also analyzed together. A correlation between the optical band gap and the electrical properties (conductivity) was found.

#### 2. Materials and Methods

Tungsten powder (W, 99.5% metals basis, Macklin Biochemical Co. Ltd, Shanghai, China) and hydrogen peroxide (H<sub>2</sub>O<sub>2</sub>, Hydrogen peroxide 30%, Guangzhou chemical regent factory, Guangzhou, China) were mixed in a beaker with a water bath at 25 °C. After the reaction finished, an evaporative concentration treatment (at 150 °C) was conducted to remove the surplus H<sub>2</sub>O<sub>2</sub>. Finally, an appropriate anhydrous ethanol was added into the concentrated solution and the mixed solution was sealed and stirred for 3 h at 70 °C to obtain the sol-gel. A spin coating technique was used to prepare the WO<sub>3</sub> films (around 80 nm) on the indium tin oxide (ITO) glass. The thickness of the WO<sub>3</sub> film was optimized and controlled by the concentration of solution and spin coating parameters and it had an important influence on the electrochromic transmittance modulation ability [19]. In this work, the annealing temperature was focused on and other unrelated variables (sol concentration, spin coating parameters, substrate, electrolyte, etc.) were controlled. These as-deposited films were annealed at 100 °C, 200 °C, 300 °C, 400 °C and 500 °C for 60 min, respectively.

The crystallization of the film was analyzed by X-ray Diffraction (XRD, PANalytical Empyrean DY1577, PANalytical, Almelo, The Netherlands). The surface morphology was measured by atomic force microscopy (AFM, Being Nano-Instruments BY3000 Being Nano-Instruments, Beijing, China). The electrochromic test was performed using 0.8 mol/L of lithium perchlorate/propylene carbonate (LiClO<sub>4</sub>/PC) electrolyte and an electrode gap (~1 mm). The transmission spectra were measured by an Ultraviolet spectrophotometer (SHIMADZU UV2600, SHIMADZU, Tokyo, Japan), with ITO glass (Optical band gap: >4 eV) acting as a blank. The current of the electrochromic test was recorded by an electrochemical workstation (CH Instruments CHI600E, CH Instruments, Shanghai, China). The relationship between the change of transmittance and the time was measured by a micro-spectrometer (Morpho PG2000, Morpho, Shanghai, China), with ITO glass acting as a blank.

#### 3. Results and Discussions

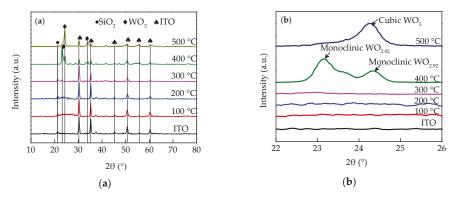

Figure 1 illustrates the X-ray patterns of the WO<sub>3</sub> films that were annealed at different temperatures. The crystalline structures of these films were further analyzed using Jade 6.0 and PDF#30-1387 and PDF#41-0905. In Figure 1a, there are diffraction peaks of WO<sub>3</sub> at the patterns of the WO<sub>3</sub> films annealed at 400 °C and 500 °C, which demonstrate that these films transformed from amorphous to crystalline when the annealing temperature is higher than 400 °C. Furthermore, the change of crystalline structure was analyzed in Figure 1b. The characteristic diffraction peaks of WO<sub>3</sub> films (400 °C) indicate that the WO<sub>3</sub> films initially transform from an amorphous to a monoclinic structure. When the annealing temperature reached 500 °C, there was only one diffraction peak of the WO<sub>3</sub> films turned into a cubic structure. Strictly speaking, the stoichiometric ratio of tungsten and oxygen was not fully satisfied with 1:3. Therefore, there was an oxygen vacancy which influenced the optical and electrical properties of WO<sub>3</sub> films [20].

**Figure 1.** X-ray patterns of WO<sub>3</sub> films annealed at different temperature. (**a**) The XRD patterns in a large range of  $2\theta$  ( $10^{\circ}$  to  $80^{\circ}$ ); (**b**) The XRD patterns in a small range of  $2\theta$  ( $22^{\circ}$  to  $26^{\circ}$ ). The amorphous WO<sub>3</sub> transformed into monoclinic structure and cubic structure at 400 °C and 500 °C, respectively.

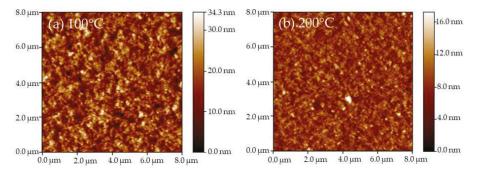

The surface morphology of these films was measured by AFM and the results are shown in Figure 2. Figure 2f shows a comparison of the roughness of these films at different annealing temperatures. The surface of the WO<sub>3</sub> film that was annealed at 100 °C is rougher than other films, which is confirmed by Figure 2a and its roughness. In this work, the solvent of sol was ethanol and water, which has a boiling point of around 80 °C. The 100 °C annealing treatment can remove the solvent, but it is not enough to remove the bound water in the tungsten acid [21]. In addition, solvent evaporation can cause defects in the surface, such as pores [22], and there is not enough energy to reduce these defects during annealing treatment. Therefore, among these samples, the WO<sub>3</sub> film annealed at 100 °C had the highest roughness.

The roughness of the films annealed at 200  $^{\circ}$ C and 300  $^{\circ}$ C was around 1.9 nm, which is less than that of the films (around 3.3 nm) annealed at 400  $^{\circ}$ C and 500  $^{\circ}$ C. This demonstrated that the crystalline film was rougher than the amorphous film because of its grain growth at a high temperature. The change in roughness indirectly revealed that the change in the WO<sub>3</sub> film composition and crystalline structure was due to the increase in the annealing temperature, which is consistent with the results of XRD.

Figure 2. Cont.

**Figure 2.** The atomic force microscope (AFM) images 8000 nm  $\times$  8000 nm) and the roughness of WO<sub>3</sub> films. (a) 100 °C; (b) 200 °C; (c) 300 °C; (d) 400 °C; (e) 500 °C; (f) the roughness of WO<sub>3</sub> films, which are read by the support software of AFM.

The band gap of  $WO_3$  film can be measured and analyzed by an ultraviolet spectrophotometer. The optical band gap is distinguished from the band gap measured by other methods. According to Equation (1), the optical band gap can be calculated [23].

$$xhv = A(hv - E_g)^n \tag{1}$$

where  $\alpha$  is the absorption coefficient, which can be measured by the ultraviolet spectrophotometer; *h* is the Planck constant; *v* is the light frequency; *A* is a proportionality constant; *E*<sub>g</sub> is the optical band gap; and *n* is a number which is 1/2 for the direct band gap semiconductor and 2 for the indirect band gap semiconductor. In this work, *n* is 2 because the WO<sub>3</sub> was an indirect band gap semiconductor.

To further investigate the electrochromic effects on the optical band gap of WO<sub>3</sub> film, the optical band gap of WO<sub>3</sub> film in a bleached state and colored state were analyzed. Electrochromism involves an electrochemical reaction, as shown in Equation (2) [24]:

$$WO_3(colorless) + xLi^+ + xe^- \leftrightarrow Li_xWO_3(blue)$$

(2)

At its bleached state, the WO<sub>3</sub> film is colorless. When both Li<sup>+</sup> and the electron are injected into the WO<sub>3</sub> film under an applied voltage, the bleached state of WO<sub>3</sub> turns into a colored state due to the generation of blue  $Li_xWO_3$ .

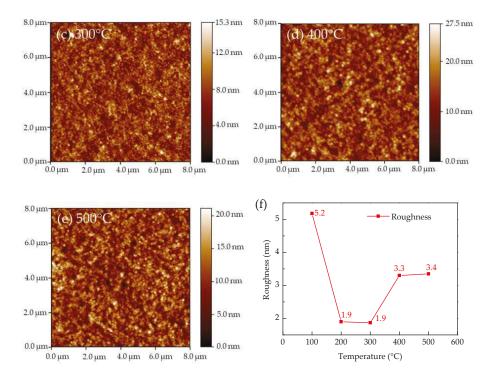

Figure 3a–e illustrates the curves of  $(\alpha h\nu)^{1/2}$  versus the photon energy  $h\nu$ , which are calculated using the transmission spectra of the WO<sub>3</sub> films in the colored state and the bleached state.  $E_g$  can be extracted through the onset of the optical transitions of the WO<sub>3</sub> films near the band edge, which is

equal to the value of the fitting line intercepts. Figure 3f shows a comparison of the optical band gap value of the WO<sub>3</sub> film that were annealed at different temperatures and electrochromic state (colored and bleached) and it indicates that the  $E_g$  of bleached WO<sub>3</sub> films decreases from 3.58 eV to 3.3 eV as the annealing temperature increases. Similarly, the  $E_g$  of the colored WO<sub>3</sub> film tends to decrease with an increased annealing temperature. In addition, the  $E_g$  of all the colored WO<sub>3</sub> films was less than that of their respective bleached WO<sub>3</sub> films.

**Figure 3.** Optical band gap energy of WO<sub>3</sub> films in a colored state and bleached state. (a) 100 °C; (b) 200 °C; (c) 300 °C; (d) 400 °C; (e) 500 °C; and (f) a comparison of optical band gap energy of WO<sub>3</sub> films annealed at different temperature and electrochromic state (colored and bleached).

As for  $E_g$ , which decreased when the annealing temperature increased, a reasonable explanation was that as the annealing temperature increased, the oxygen vacancies increased, which may have provided free electrons and enhanced the conductivity of the WO<sub>3</sub> films [25].

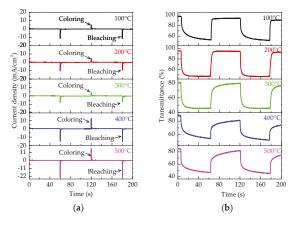

To further investigate the relationship between  $E_g$ , conductivity, and electrochromic response time, an electrochromic test was conducted. Figure 4a,b illustrates the current density of the different WO<sub>3</sub> films and the change of transmittance (at 600 nm) under  $\pm 2.5$  V voltage, respectively. The peak current density of these films in the coloring process increased when the annealing temperature increased (an increase from 2.6 mA/cm<sup>2</sup> at 100 °C to 16.1 mA/cm<sup>2</sup> at 500 °C). This indicated that the conductivity enhanced with the increase in the annealing temperature. Similarly, the peak current density of these films in the bleaching process shows a similar change (increase from 11.0 mA/cm<sup>2</sup> at 100 °C to 22.2 mA/cm<sup>2</sup> at 500 °C). These were attributed to the decrease of  $E_g$  and the increase of free electrons. In addition, Figure 4a illustrates that the peak current density of the bleaching process was larger than that of coloring process, which results from the good conductivity of Li<sub>x</sub>WO<sub>3</sub> [26]. This is related to the decrease of  $E_g$  after WO<sub>3</sub> film coloring.

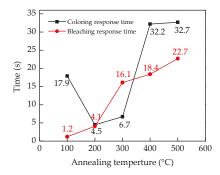

Figure 4b illustrates an intuitive change of transmittance response curves. The response time is defined by the time corresponding to 90% of the total transmittance change. Figure 5 shows a specific comparison of the response time in the electrochromic test. The curve of the bleaching response time in Figure 5 shows that the bleaching response time increases from 1.2 s to 22.7 s, when the annealing temperature increased. In the bleaching process, the applied voltage drop is mainly across the electrolyte and the Li<sub>x</sub>WO<sub>3</sub> layer. The extraction of Li<sup>+</sup> depends largely on the voltage across the  $Li_xWO_3$  layer [27]. The  $E_g$  of the WO<sub>3</sub> film at the colored state reduced with the increase in the annealing temperature, which was attributed to the increase in the number of free electrons. In other words, the conductivity enhanced with the increase in annealing temperature. Therefore, the voltage across the  $Li_xWO_3$  layer reduced with the increase in annealing temperature, which resulted in the increase of the bleaching response time. However, there was no similar trend in the coloring response time. The influence factors are not only the conductivity of the  $WO_3$  film, but also the interface barrier of electrolyte-film [28]. The coloring response time increased when the WO<sub>3</sub> film changed from amorphous into crystalline, which resulted from the decrease in the voltage drop at the WO<sub>3</sub> layers, due to the increase in the conductivity. The band gap mainly influenced the transmission of the electrons, but the transmission of Li<sup>+</sup> depended more on the structure of films (such as crystallinity, morphology, etc.) [29].

**Figure 4.** (a) Current change of WO<sub>3</sub> films at different annealing temperature. The applied voltage was  $\pm 2.5$  V and the WO<sub>3</sub> films were placed in the cathode; (b) change of transmittance (at 600 nm) of WO<sub>3</sub> films at different annealing temperature.

Figure 5. The curves of coloring and bleaching response time versus annealing temperature. The time corresponding to 90% of the total transmittance change is defined as the electrochromic response time.

### 4. Conclusions

The effects of the annealing temperature on the  $E_g$  of the WO<sub>3</sub> films were investigated. When the annealing temperature was higher than 400 °C, the crystalline structure of the WO<sub>3</sub> film changed from amorphous to monoclinic (400 °C), and then to cubic (500 °C). The  $E_g$  of the WO<sub>3</sub> films decreased from 3.62 eV to 3.30 eV when the annealing temperature was increased. In addition, the  $E_g$  of the colored WO<sub>3</sub> films was less than that of the bleached WO<sub>3</sub> films. The relationship between the  $E_g$ , conductivity, and electrochromic response time of the WO<sub>3</sub> film with different annealing temperatures demonstrates that the conductivity of the WO<sub>3</sub> film enhanced with the decrease in  $E_g$ , while the high conductivity increased the electrochromic response time.

Author Contributions: Conceptualization, G.Z.; Data curation, G.Z., K.L., W.Y., M.S. and X.L.; Formal analysis, G.Z., K.L., W.Y., R.T. and X.L.; Funding acquisition, H.N. and R.Y.; Investigation, X.Z. and M.S.; Methodology, X.Z., R.T. and X.L.; Project administration, H.N., R.Y. and J.P.; Supervision, H.N.; Writing—original draft, G.Z.; Writing—review & editing, K.L., H.N., R.T., X.L., R.Y. and J.P.

Acknowledgments: This work was supported by National Natural Science Foundation of China (Grant.51771074, 51521002 and U1601651), National Key R&D Program of China (No.2016YFB0401504 and 2016YFF0203600), National Key Basic Research and Development Program of China (973 program, Grant No.2015CB655004) Founded by Ministry of Science and Technology (MOST), Guangdong Natural Science Foundation (No.2016A030313459 and 2017A030310028), Guangdong Science and Technology Project (No.2016B090907001, 2016A040403037, 2016B090906002, 2017B090907016 and 2017A050503002), Guangzhou Science and Technology Project (201804020033).

Conflicts of Interest: The authors declare no conflicts of interest.

#### References

- Hill, J.C.; Choi, K.S. Effect of electrolytes on the selectivity and stability of n-type WO<sub>3</sub> photoelectrodes for use in solar water oxidation. J. Phys. Chem. C 2012, 116, 7612–7620. [CrossRef]

- Leidinger, M.; Huotari, J.; Sauerwald, T.; Lappalainen, J.; Schütze, A. Selective detection of naphthalene with nanostructured WO<sub>3</sub> gas sensors prepared by pulsed laser deposition. *J. Sens. Syst.* 2016, 5, 147–156. [CrossRef]

- Sotelo-Vazquez, C.; Quesada-Cabrera, R.; Ling, M.; Scanlon, D.O.; Kafizas, A.; Thakur, P.K.; Lee, T.L.; Taylor, A.; Watson, G.W.; Palgrave, R.G. Photocatalysis: Evidence and effect of photogenerated charge transfer for enhanced photocatalysis in WO<sub>3</sub>/TiO<sub>2</sub> heterojunction films: A computational and experimental study. *Adv. Funct. Mater.* 2017, 27, 1605413. [CrossRef]

- Hara, K.; Zhao, Z.G.; Cui, Y.; Miyauchi, M.; Miyashita, M.; Mori, S. Nanocrystalline electrodes based on nanoporous-walled WO<sub>3</sub> nanotubes for organic-dye-sensitized solar cells. *Langmuir* 2011, 27, 12730–12736. [CrossRef] [PubMed]

- Wang, F.; Valentin, C.D.; Pacchioni, G. Doping of WO<sub>3</sub> for photocatalytic water splitting: Hints from density functional theory. J. Phys. Chem. C 2012, 116, 8901–8909. [CrossRef]

- Cai, G.; Cui, M.; Kumar, V.; Darmawan, P.; Wang, J.; Wang, X.; Eh, L.S.; Qian, K.; Lee, P.S. Ultra large optical modulation of electrochromic porous WO<sub>3</sub> film and the local monitoring of redox activity. *Chem. Sci.* 2016, 7, 1373–1382. [CrossRef] [PubMed]

- Yang, W.; Runnerstrom, E.L.; Milliron, D.J. Switchable materials for smart windows. Annu. Rev. Chem. Biomol. Eng. 2016, 7, 283–304.

- Granqvist, C.G. Electrochromic tungsten oxide films: Review of progress 1993–1998. Sol. Energy Mat. Sol. Cells 2000, 60, 201–262. [CrossRef]

- 9. Lemire, C.; Lollman, D.B.B.; Mohammad, A.A.; Gillet, E.; Aguir, K. Reactive R.F. magnetron sputtering deposition of WO<sub>3</sub> thin films. *Sens. Actuators B Chem.* **2002**, *84*, 43–48. [CrossRef]

- Davazoglou, D.; Leveque, G.; Donnadieu, A. Study on the optical and electrochromic properties of polycrystalline WO<sub>3</sub> thin films prepared by CVD. *Sol. Energy Mater.* **1988**, *17*, 379–390. [CrossRef]

- Reichman, B.; Bard, A.J. The Electrochromic process at WO<sub>3</sub> electrodes prepared by vacuum evaporation and anodic oxidation of W. J. Electrochem. Soc. 2016, 126, 583–591. [CrossRef]

- Zayim, E.O. Optical and electrochromic properties of sol-gel made anti-reflective WO<sub>3</sub>-TiO<sub>2</sub> films. Sol. Energy Mate. Sol. Cells 2005, 87, 695–703. [CrossRef]

- Wojcik, P.; Cruz, A.; Santos, L.; Pereira, L.; Martins, R.; Fortunato, E. Microstructure control of dual-phase inkjet-printed a-WO<sub>3</sub>/TiO<sub>2</sub>/WO<sub>X</sub> films for high-performance electrochromic applications. *J. Mater. Chem.* 2012, 22, 13268–13278. [CrossRef]

- Santos, L.; Wojcik, P.; Pinto, J.V.; Elangovan, E.; Viegas, J.; Pereira, L.; Martins, R.; Fortunato, E. Structure and morphologic influence of WO<sub>3</sub> nanoparticles on the electrochromic performance of dual-phase a-WO<sub>3</sub>/WO<sub>3</sub> inkjet printed films. *Adv. Electron. Mater.* 2015, *1*, 1–2. [CrossRef]

- 15. Mukherjee, R.; Sahay, P.P. Effect of precursors on the microstructural, optical, electrical and electrochromic properties of WO<sub>3</sub> nanocrystalline thin films. *J. Mater. Sci-Mater. Electron.* **2015**, *26*, 1–13. [CrossRef]

- Chai, Y.N.; Razak, K.A.; Lockman, Z. Effect of annealing on acid-treated WO<sub>3</sub>·H<sub>2</sub>O nanoplates and their electrochromic properties. *Electrochimica Acta* 2015, 178, 673–681.

- Gonzalez-Borrero, P.P.; Sato, F.; Medina, A.N.; Baesso, M.L.; Bento, A.C.; Baldissera, G.; Persson, C.; Niklasson, G.A.; Granqvist, C.G.; Silva, A.J.D. Optical band-gap determination of nanostructured WO<sub>3</sub> film. *Appl. Phys. Lett.* 2010, *96*, 201. [CrossRef]

- Vemuri, R.S.; Engelhard, M.H.; Ramana, C.V. Correlation between surface chemistry, density, and band gap in nanocrystalline WO<sub>3</sub> thin films. ACS Appl.Mater. Interfaces 2012, 4, 1371–1377. [CrossRef] [PubMed]

- Min, H.K.; Choi, H.W.; Kim, K.H. Thickness dependence of WO<sub>3-x</sub> thin films for electrochromic device application. *Mol. Cryst. Liquid Cryst.* 2014, 598, 54–61.

- 20. Arfaoui, A.; Ouni, B.; Touihri, S.; Mannoubi, T. Investigation into the optoelectrical properties of tungsten oxide thin films annealed in an oxygen air. *Mater. Res. Bull.* **2014**, *60*, 719–729. [CrossRef]

- Szilágyi, I.M.; Santala, E.; Heikkilä, M.; Kemell, M.; Nikitin, T.; Khriachtchev, L.; Räsänen, M.; Ritala, M.; Leskelä, M. Thermal study on electrospun polyvinylpyrrolidone/ammonium metatungstate nanofibers: Optimising the annealing conditions for obtaining WO<sub>3</sub> nanofibers. *J. Therm. Anal. Calorim.* 2011, 105, 73. [CrossRef]

- Badilescu, S.; Ashrit, P.V. Study of sol-gel prepared nanostructured WO<sub>3</sub> thin films and composites for electrochromic applications. *Solid State Ion.* 2003, 158, 187–197. [CrossRef]

- Zou, Y.S.; Zhang, Y.C.; Lou, D.; Wang, H.P.; Gu, L.; Dong, Y.H.; Dou, K.; Song, X.F.; Zeng, H.B. Structural and optical properties of WO<sub>3</sub> films deposited by pulsed laser deposition. *J. Alloy Compd.* 2014, 583, 465–470. [CrossRef]

- Haro-Poniatowski, E.; Jouanne, M.; Morhange, J.F.; Julien, C.; Diamant, R.; Fernández-Guasti, M.; Fuentes, G.A.; Alonso, J.C. Micro-raman characterization of WO<sub>3</sub> and MoO<sub>3</sub> thin films obtained by pulsed laser irradiation. *Appl. Surf. Sci.* 1998, 127–129, 674–678. [CrossRef]

- 25. Chai, Y.; Tam, C.W.; Beh, K.P.; Yam, F.K.; Hassan, Z. Effects of thermal treatment on the anodic growth of tungsten oxide films. *Thin Solid Films* **2015**, *588*, 44–49. [CrossRef]

- Badot, J.C.; Beluze, L.; Dubrunfaut, O. Particle size effect on the electronic conductivity of electroactive Li<sub>x</sub>WO<sub>3</sub>·H<sub>2</sub>O powders: A study from 10<sup>3</sup> to 10<sup>10</sup> Hz. J. Phys. Chem. C 2009, 112, 14549–14554. [CrossRef]

- 27. Faughnan, B.W.; Crandall, R.S.; Lampert, M.A. Model for the bleaching of WO<sub>3</sub> electrochromic films by an electric field. *Appl. Phys. Lett.* **1975**, *27*, 275–277. [CrossRef]

- Srivastava, A.K.; Deepa, M.; Singh, S.; Kishore, R.; Agnihotry, S.A. Microstructural and electrochromic characteristics of electrodeposited and annealed WO<sub>3</sub> films. *Solid State Ion.* 2005, 176, 1161–1168. [CrossRef]

- Koo, B.R.; Ahn, H.J. Fast-switching electrochromic properties of mesoporous WO<sub>3</sub> films with oxygen vacancy defects. *Nanoscale* 2017, 9, 17788–17793. [CrossRef] [PubMed]

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Article

### An Improved Large Signal Model for 0.1 $\mu$ m AlGaN/GaN High Electron Mobility Transistors (HEMTs) Process and Its Applications in Practical Monolithic Microwave Integrated Circuit (MMIC) Design in W band

Junfeng Li <sup>1</sup>, Shuman Mao <sup>1</sup>, Yuehang Xu <sup>1,\*</sup>, Xiaodong Zhao <sup>1</sup>, Weibo Wang <sup>2</sup>, Fangjing Guo <sup>2</sup>, Qingfeng Zhang <sup>1</sup>, Yunqiu Wu <sup>1</sup>, Bing Zhang <sup>2</sup>, Tangsheng Chen <sup>2</sup>, Bo Yan <sup>1</sup>, Ruimin Xu <sup>1</sup> and Yanrong Li <sup>1</sup>

- <sup>1</sup> School of Electronic Science and Engineering (National Exemplary School of Microelectronics), University of Electronic Science and Technology of China, Chengdu 611731, China; lijunfeng\_EE@163.com (J.L.); maoshuman@163.com (S.M.); zhaoxiaodong@std.uestc.edu.cn (X.Z.); a2277462594@163.com (Q.Z.); yqwu@uestc.edu.cn (Y.W.); yanbo@ee.uestc.edu.cn (B.Y.); rmxu@uestc.edu.cn (R.X.); yrli@uestc.edu.cn (Y.L.)

- <sup>2</sup> Nanjing Electronic Devices Institute, Nanjing 210016, China; bobommic@163.com (W.W.); fjiguo@163.com (F.G.); binzhang\_cetc55@aliyun.com (B.Z.); chentsh@vip.sina.com (T.C.)

- \* Correspondence: yuehangxu@uestc.edu.cn

Received: 28 June 2018; Accepted: 8 August 2018; Published: 10 August 2018

MDP

**Abstract:** An improved empirical large signal model for 0.1 µm AlGaN/GaN high electron mobility transistor (HEMT) process is proposed in this paper. The short channel effect including the drain induced barrier lowering (DIBL) effect and channel length modulation has been considered for the accurate description of DC characteristics. In-house AlGaN/GaN HEMTs with a gate-length of 0.1 µm and different dimensions have been employed to validate the accuracy of the large signal model. Good agreement has been achieved between the simulated and measured S parameters, I-V characteristics and large signal performance at 28 GHz. Furthermore, a monolithic microwave integrated circuit (MMIC) power amplifier from 92 GHz to 96 GHz has been designed for validation of the proposed model. Results show that the improved large signal model can be used up to W band.

Keywords: AlGaN/GaN HEMT; DIBL effect; channel length modulation; power amplifier; W band

### 1. Introduction

Wide band gap semiconductor Gallium Nitride (GaN) high electron mobility transistors (HEMTs) are excellent candidates in high frequency power electronics due to their unique advantages of higher breakdown voltage and higher output power density [1]. With the rapid development of process, the feature size of GaN HEMTs have been shrinking to less than 0.1 µm. GaN HEMTs with good performance for application in W band have been reported [2–5]. Also, over the past few years, several GaN HEMT based monolithic microwave integrated circuits (MMICs) up to W-band have been developed, due to their applications in high speed wireless communications or radar systems [6]. A GaN MMIC power amplifier at 91 GHz was reported to have 1.7 W output power that is associated with 11% power added efficiency [7]. A W-Band MMIC power amplifier with 3.46 W/mm output power density and 21% associated power added efficiency was then reported. The associated power gain is 13.7 dB. It offers a peak small signal gain of 16.7 dB over 90–97 GHz [2].

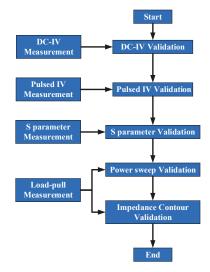

For applications of these devices in circuit design, compact nonlinear device modeling plays an important role in practical design. Recently, a few physical based compact models have sprung up due

to their advantages in less fitting parameters and good accuracy up to the Ka band [8–11]. However, things will be different when the frequency is up to W band. Firstly, the parasitic effect will become obvious with the increasing of frequency and make the parameter extraction more difficult [12,13]. This problem can be solved by FW-EM (Full-wave electromagnetic) simulation [14]. Secondly, along with the reduction of feature size, the short channel effect becomes obvious. This phenomenon will in the end give rise to shift of threshold voltage. Thirdly, the gradual channel approximation (GCA) that is used in many kinds of physical based compact model [15,16] is no more effective as the channel length modulation is obvious in short channel devices. These effects will largely decrease the accuracy of physical based compact model. The empirical modeling method has been widely used due to their excellent performance in convergence and accuracy [17–22]. An effective validation of large signal model is validated by on-wafer load-pull measurement [23,24]. However, due to the complication of load-pull measurement, only one input/output impedance is validated. Nevertheless, more input/output impedances need to be validated for a large signal model in practical MMIC power amplifier design [25].

In this paper, the short channel effect, including the DIBL effect and channel length modulation, is studied. An improvement for the accuracy of the area near the pinch-off region in IV curve is performed based on an empirical modeling method as the GCA is no more effective in most physical based model. In-house AlGaN/GaN HEMTs with gate length of 0.1  $\mu$ m is used for validation of the model. Performance, including S parameters, DC characteristics, and large signal characteristics at 28 GHz is validated by on-wafer measurement. Finally, a MMIC power amplifier is designed based on the proposed model for further validation.

This paper is organized as follows. In Section 2, the investigation on short channel effect is presented. The modeling method of it, which is based on an empirical method, is given in detail. In Section 3, the proposed large signal model is validated with two GaN HEMTs with different gate width. In Section 4, a MMIC power amplifier based on the large signal model in this work is designed for further validation of the model in W band. Finally, in Section 5, the conclusion of this work is presented.

#### 2. Model Description

#### 2.1. Short Channel Effects

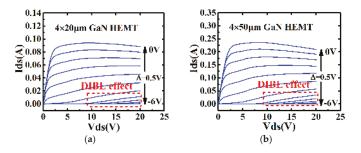

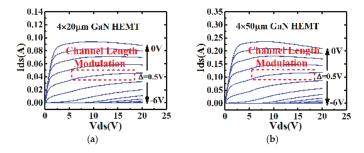

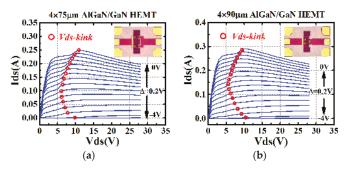

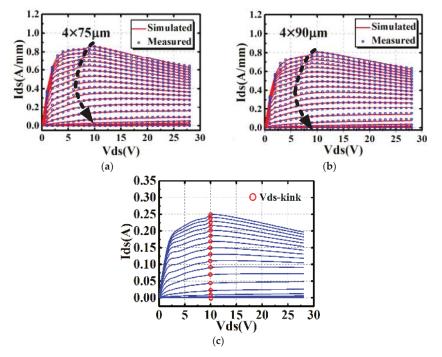

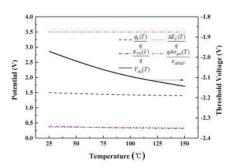

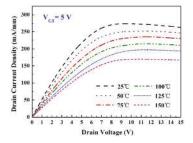

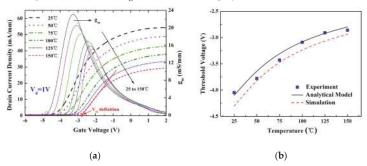

Along with the decrease of gate length, the short channel effect, such as the drain induced barrier lowering (DIBL) effect will become obvious. The thickness of the barrier will not only be modulated by gate voltage, but also drain voltage. This will, in the end, lead to the drift of threshold voltage along with the drain voltage. This phenomenon can be easily captured in the static IV curve of 0.1 µm AlGaN/GaN HEMTs with different gate width in this work, which have been shown in Figure 1.

**Figure 1.** Drain induced barrier lowering (DIBL) effect in Static IV curves of 0.1  $\mu$ m AlGaN/GaN high electron mobility transistor (HEMT) with different gate width: (a) 4  $\times$  20  $\mu$ m and (b) 4  $\times$  50  $\mu$ m.

It can be seen from Figure 1 that the DIBL effect will weaken the effect that is brought by gate voltage. The device will be turned from off-state to on-state with the rise of drain voltage. This phenomenon must be taken into consideration, especially for high efficiency power amplifier or switching applications.

In order to accurately describe the output performance of AlGaN/GaN HEMTs with short gate length in large signal modeling, the short channel effect, including the DIBL effect and channel length modulation, should be taken into consideration. An empirical method that is based on the Angelov model is employed for the devices in this work. As we know that the coefficients of the  $\psi$  polynomial in Angelov model, which is shown in Equation (1), mainly affect the accuracy of the region close to pinch-off state.

$$\psi = P_1 \times (V_{gs} - V_{pk1}) + P_2 \times \left(V_{gs} - V_{pk2}\right)^2 + P_3 \times \left(V_{gs} - V_{pk3}\right)^3 \tag{1}$$

where  $V_{gs}$  refers to the gate-source voltage.  $V_{pkn}$  (n = 1, 2, 3) are fitting parameters.  $P_n$  (n = 1, 2, 3) are fitting coefficients of the  $\psi$  polynomial.

To accurately model the DIBL effect, the drain-source voltage  $V_{ds}$  has been included in  $P_n$  (n = 1, 2, 3) to take the modulation effect of  $V_{ds}$  into consideration, as shown in Equation (2).

$$P_n = P_{n0} + (P_{n1} \times V_{ds} - P_{n0}) \times \tanh(\alpha P_{n2} \times V_{ds}) \quad (n = 1, 2, 3)$$

(2)

where  $P_{n0}$ ,  $P_{n1}$ ,  $P_{n2}$  and  $\alpha$  are all fitting parameters.

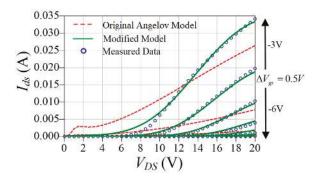

The modification was validated by a comparison between simulation results and measured data. The comparison between the original Angelov model and modified one are shown in Figure 2. The gate-source voltage  $V_{gs}$  is from -6 V to -3 V and the drain source voltage  $V_{ds}$  is from 0 V to 20 V.

Figure 2. Comparison between simulated and measured results when  $V_{gs}$  is close to pinch-off voltage.

It is clear in Figure 2 that the original Angelov model cannot accurately describe the DC characteristics when  $V_{gs}$  is close to the pinch-off voltage. The DIBL effect can be successfully modeled by using proposed model.

Apart from the DIBL effect, the channel length modulation can also be captured in the static IV curves, as shown in Figure 3.

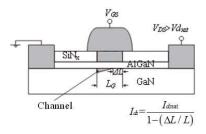

It clearly shows that the partial derivative of  $I_{ds}$  to  $V_{ds}$  is not equal to zero due to channel length modulation. The channel length effect is mainly induced by expanding of the depletion region towards the source. The effective channel is then shortened. This phenomenon is shown in Figure 4.

Figure 3. Channel length modulation effect in Static IV curves of 0.1  $\mu$ m AlGaN/GaN HEMT with different gate width: (a) 4  $\times$  20  $\mu$ m and (b) 4  $\times$  50  $\mu$ m.

Figure 4. The schematic diagram of the short channel modulation effect.

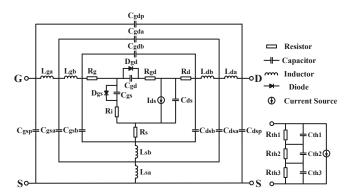

### 2.2. Large Signal Model up to W Band

With the frequency up to W band, the RF dispersion will become more and more obvious due to the parasitic effects inside devices. A wide band small signal model [14], which has been proved to be able to cover the frequency band from 0.2–110 GHz, is employed in this work. The topology of the large signal model is shown in Figure 5.

Figure 5. Topology of Large signal model up to W band.

The main part of the nonlinear current model as well as the capacitance model, including  $C_{gs}$  and  $C_{gd}$  mentioned in [21], is employed in this work. The improvement for accurate characterization of short channel effect, which is mentioned in the previous section, has also been included in the nonlinear current model. In order to accurately characterize the self-heating effect in AlGaN/GaN HEMT. The three-pole thermal network in [25] is used. Thermal resistances as well as the thermal

capacitances are extracted by a method based on FEM simulation in ANSYS. The trapping effect is modeled by the equivalent voltage method in [26]. The scalability of the model parameters, including the  $I_{pk0}$ ,  $R_{th}$ , and  $C_{th}$  has been realized with the method that is mentioned in [22] for practical monolithic microwave integrated circuit design. With the help of MATLAB coding, model parameters, except the coefficients in Equation (2), are all extracted with the method in [27]. In terms of parameters in Equation (2), they are all extracted by fitting the transfer characteristics curve with the least square method.

### 3. Model Validation

### 3.1. Small Signal Characterization

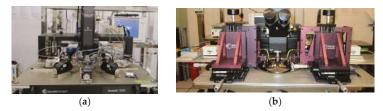

The large signal model was embedded into Keysight ADS (Advanced Design System) by a symbolically defined device (SDD) tool. Small signal characteristics of the devices are measured by cascade probe station (Summit 11000B, FormFactor, Livermore, CA, USA), which is shown in Figure 6. The vector network analyzer is Keysight N5247A (Keysight Technologies, Santa Rosa, CA, USA). The frequency extenders close to probes are used to achieve the S parameters ranging from 75 GHz to 110 GHz as the vector network analyzer can only reach up to 67 GHz.

Figure 6. On-wafer measurement system for small signal characteristics.

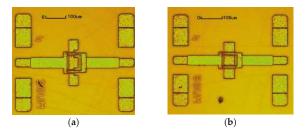

The proposed model was validated by 0.1  $\mu$ m AlGaN/GaN HEMTs with different gate width. AlGaN/GaN HEMTs were all fabricated on a 4-inch SiC substrate. T-shape-gate technology was introduced to reduce the contact resistance. The  $f_T$  of the 0.1  $\mu$ m GaN process is 90 GHz, while  $f_{max}$  is 220 GHz. The peak power density for a specific device can reach up to 3.46 W/mm. The photography of devices is shown in Figure 7.

Figure 7. 0.1  $\mu m$  AlGaN/GaN HEMTs: (a)  $4\times 20~\mu m$  and (b)  $4\times 50~\mu m.$

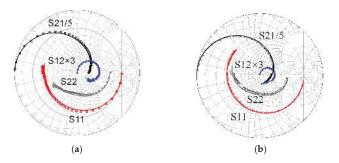

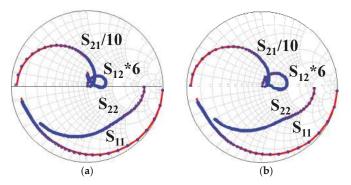

The comparison of simulated and measured S parameters is shown in Figure 8. Results show that the proposed model can predict the small signal characteristics ranging from 0.2 GHz to 110 GHz for devices with different gate width and under different bias.

**Figure 8.** Comparison of simulated and measured S-parameters: (a)  $4 \times 20 \text{ }\mu\text{m}$  at Vgs = -2 V, Vds = 10 V and (b)  $4 \times 50 \text{ }\mu\text{m}$  at Vgs = -1 V, Vds = 15 V.

### 3.2. The Large Signal Model Validation

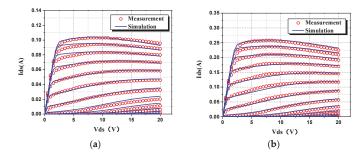

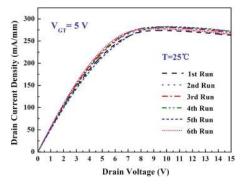

The DC characteristics for the proposed scalable large signal model was validated by different gate width, including  $4 \times 20 \ \mu\text{m}$  and  $4 \times 50 \ \mu\text{m}$ , as shown in Figure 9. The gate-source voltage  $V_{gs}$  is investigated from  $-6 \ V$  to  $0 \ V$ , while the drain-source voltage  $V_{ds}$  is from  $0 \ V$  to  $20 \ V$  for these two devices.

Figure 9. Comparison of simulated and measured DC characteristics of 0.1  $\mu$ m AlGaN/GaN HEMTs: (a) 4 × 20  $\mu$ m and (b) 4 × 50  $\mu$ m.

Figure 9 shows that the DIBL effect is accurately characterized based on the improvement in Equation (2). The channel length modulation effect is also the same.

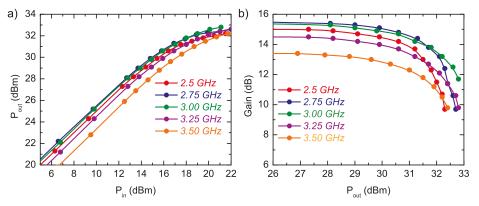

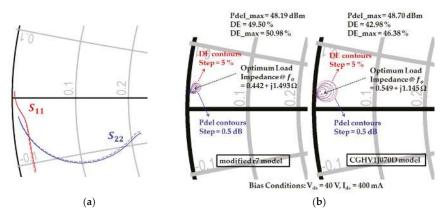

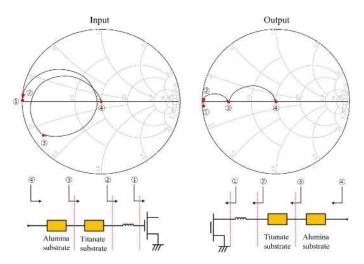

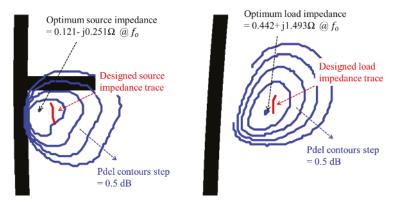

Due to the absent of W band load-pull system, the load pull performance at 28 GHz was used to validate the large signal model first, as shown in Figure 10. The system is on cascade probe station (Summit 12000, FormFactor, Livermore, CA, USA), the input signal generator is Agilent E8257D (Keysight Technologies, Santa Rosa, CA, USA), and the output power is detected by power meter Agilent N1912A (Keysight Technologies, Santa Rosa, CA, USA) and Vector Network Analyzer (Keysight Technologies, Santa Rosa, CA, USA).

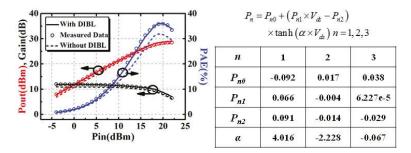

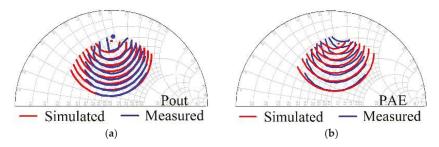

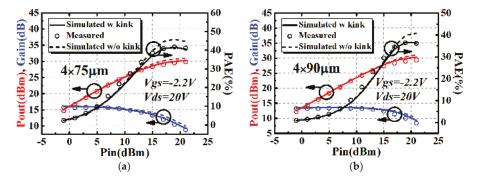

The maximum output power load-pull measurement is performed. The bias is chosen at  $V_{gs} = -2.6 \text{ V}$ ,  $V_{ds} = 15 \text{ V}$ , which is at deep class AB working state. The quiescent drain current is 82 mA at this bias. The optimum source and load resistance for the maximum output power are  $Z_S = (13.44 + 12.41 \times \text{j}) \Omega$  and  $Z_L = (27.19 + 27.44 \times \text{j}) \Omega$ . The power sweep was then performed based on the optimum resistance with the input power ranging from -4 dBm to 22 dBm. The comparison between the simulated and measured results, including output power (Pout), gain, and power added efficiency (PAE) are shown in Figure 11. Also, the influence that is brought by the DIBL effect has also been investigated in Figure 11. Results show that the DIBL effect will lead to the reduction of Pout, gain, and PAE. This can be explained by the variation of static bias point due to the DIBL effect.

Figure 10. Photograph of on-wafer load-pull system setup.

Figure 11. Investigation on the influence brought by DIBL effect on large signal performance.

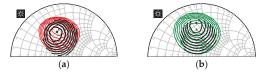

The simulated and measured impedance charts achieved by maximum Pout and PAE load-pull measurement are presented in Figure 12.

Figure 12. Comparison between simulated impedance chart and measured one: (a) maximum Pout and (b) maximum power added efficiency (PAE).

### 4. W Band MMIC Power Amplifier Design

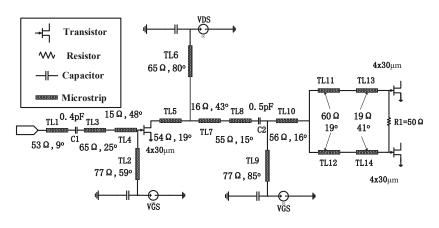

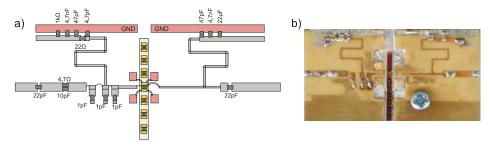

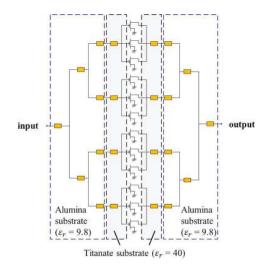

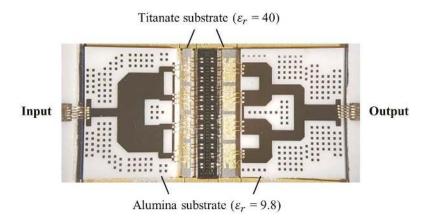

For further validation of the proposed large signal model for applications in the W band, a MMIC power amplifier whose operation frequency is 92 GHz–96 GHz was designed. Based on the above large signal model, a W-band power amplifier is designed. Figure 13 presents the schematic of the W band amplifier.

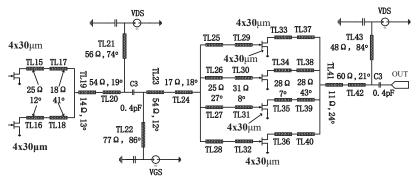

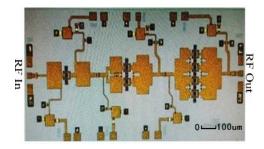

The output stage used the planar spatial power combiner to realize the impedance transformation and combine the four-way power element. The millimeter wave GaN device is very easy to oscillation at low frequency due to the high gain. Multi-order RC network was used to improve the stability of the circuit. In order to enable the former stage to have enough power to drive the latter stage, the driving ratio of amplifier circuit is 1:2:4. Passive components include micro-strip line, MIM (Metal-insulator-Metal) capacitance, and resistor. All of the passive components were simulated by EM simulator in ADS. Figure 14 shows photograph of a W-band GaN MMIC amplifier.

(b)

Figure 13. Schematic of W band amplifier: (a) Preceding stage and (b) Post stage.

Figure 14. Photograph of a W-band Gallium Nitride (GaN) monolithic microwave integrated circuits (MMIC) amplifer.

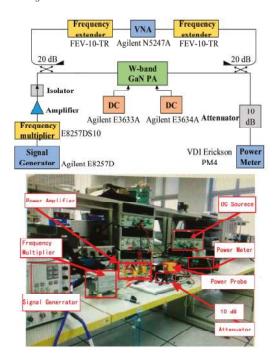

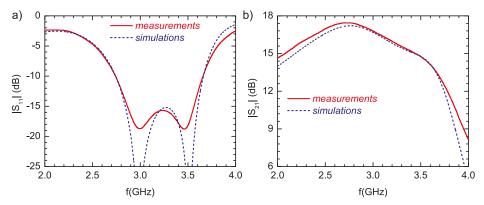

The chip was loaded into a jig for measurement. The schematic of the measurement setup for large-signal measurements is shown in Figure 15. The large signal measurement was performed at room temperature. The commercial amplifier, frequency multiplier, and signal analyzer in Figure 15 are used to assistant the measurement. Other instruments including power meter (VDI Erickson, Virginia Diodes, Inc., Charlottesville, VA, USA), DC sources (Agilent E3633A and E3634A, Keysight Technologies, Santa Rosa, CA, USA), and attenuator (Rebes, Suzhou, China) were also employed. The amplifier is measured in CW (Continuous Wave) mode over 90 GHz–97 GHz frequency. The device was bias at  $V_{ds} = 15$  V and  $V_{gs} = -2$  V.

Figure 15. Photograph of the measurement setup for the W band MMIC power amplifier.

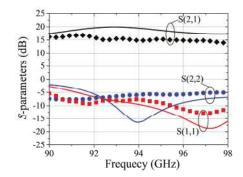

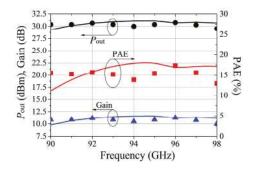

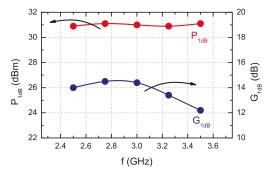

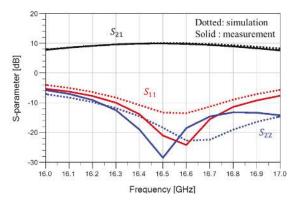

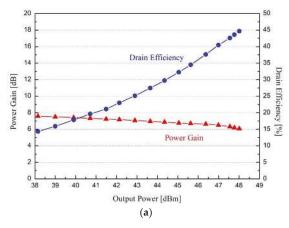

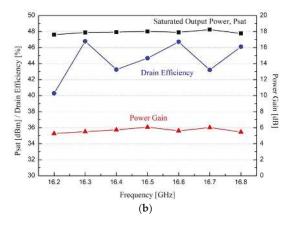

Figure 16 displays measured and simulated S-parameters of the MMIC amplifier. The difference in Figure 16 may come from the cavity and gold wire used for assisting the measurement. Their influence on frequency shift has not been taken into consideration during the MMIC design. However, this accuracy is sufficient for the application of practical circuit design. Figure 17 shows Gain, PAE, and output power. Over 90 GHz–97 GHz frequency range, the output power is greater than 1 W. The peak output power is 1.2 W. Except for 94 GHz and 98 GHz, the measured PAE was greater than 15%.

Figure 16. Measured (solid) and simulated (Symbol) S parameters of W band MMIC amplifier.

Figure 17. Measured (Symbol) and simulated (solid) large-signal characteristics of the W-band MMIC PA.

### 5. Conclusions

In this paper, an improved large signal model for AlGaN/GaN HEMT up to the W band is presented. The short channel effects including the DIBL effect and channel length modulation are added in the Angelov model. In-house AlGaN/GaN HEMTs with gate length of 0.1  $\mu$ m are used for the validation of the model. A MMIC power amplifier is designed based on the proposed model for further validation. Results show that the large signal model can give good accuracy up to W band. The results of this paper can provide guidance to many other kinds FET (Field Effect Transistor) devices modeling in the W band. Also, they are useful for the improvement of the GaN process and also are helpful for the practical MMIC design in the W band.

Author Contributions: Investigation—J.L., S.M. and X.Z.; Methodology—Y.X.; Supervision—Y.X., B.Z., T.C., B.Y., R.X. and Y.L.; Validation—W.W., F.G., Q.Z. and Y.W.; Writing original draft—J.L. and S.M.; Writing review & editing—Y.X., J.L. and S.M. contributed equally to this work.

**Funding:** This research was funded by National Natural Science Foundation of China (Grant No. 61474020), the Fundamental Research Funds for the Central Universities (Grant No. ZYGX2016J036), and the National Key Project of Science and Technology.

**Conflicts of Interest:** The authors declare that there is no conflict of interests regarding the publication of this article.

### References

- Mishra, U.K.; Shen, L.; Kazior, T.E.; Wu, Y.F. Gan-based RF power devices and amplifiers. *Proc. IEEE*. 2008, 96, 287–305. [CrossRef]

- 2. Shaobing, W.; Jianfeng, G.; Weibo, W.; Junyun, Z. W-band MMIC PA with ultrahigh power density in 100-nm AlGaN/GaN technology. *IEEE Trans. Electron Devices* **2016**, *63*, 3882–3886. [CrossRef]

- Wienecke, S.; Romanczyk, B.; Guidry, M.; Li, H.; Ahmadi, E.; Hestroffer, K.; Zheng, X.; Keller, S.; Mishra, U.K. N-polar gan cap mishemt with record power density exceeding 6.5 W/mm at 94 GHz. *IEEE Electron Device Lett.* 2017, 38, 359–362. [CrossRef]

- Xing, W.; Liu, Z.; Ranjan, K.; Ng, G.I.; Palacios, T. Planar nanostrip-channel Al<sub>2</sub>O<sub>3</sub>/InAIN/GaN MISHEMTs on Si with improved linearity. *IEEE Electron Device Lett.* 2018, 39, 947–950. [CrossRef]

- Romanczyk, B.; Wienecke, S.; Guidry, M.; Li, H.; Ahmadi, E.; Zheng, X.; Keller, S.; Mishra, U.K. Demonstration of constant 8 W/mm power density at 10, 30, and 94 GHz in state-of-the-art millimeter-wave N-polar GaN MISHEMTs. *IEEE Trans. Electron Devices* 2018, 65, 45–50. [CrossRef]

- Niida, Y.; Kamada, Y.; Ohki, T.; Ozaki, S.; Makiyama, K.; Minoura, Y.; Okamoto, N.; Sato, M.; Joshin, K.; Watanabe, K. 3.6 W/mm high power density W-band InAlGaN/GaN HEMT MMIC power amplifier. In Proceedings of the 2016 IEEE Topical Conference on Power Amplifiers for Wireless and Radio Applications (PAWR), Austin, TX, USA, 24–27 January 2016; pp. 24–26.

- Brown, A.; Brown, K.; Chen, J.; Hwang, K.C.; Kolias, N.; Scott, R. W-band GaN power amplifier MMICs. In Proceedings of the 2011 IEEE MTT-S International Microwave Symposium, Baltimore, MD, USA, 5–10 June 2011; pp. 1–4.

- 8. Cheng, X.; Wang, Y. A surface-potential-based compact model for AlGaN/GaN MODFETs. *IEEE Trans. Electron Devices* **2011**, *58*, 448–454. [CrossRef]

- 9. Khandelwal, S.; Chauhan, Y.S.; Fjeldly, T.A. Analytical modeling of surface-potential and intrinsic charges in AlGaN/GaN HEMT devices. *IEEE Trans. Electron Devices* **2012**, *59*, 2856–2860. [CrossRef]

- 10. Deng, W.; Huang, J.; Ma, X.; Liou, J.J. An explicit surface potential calculation and compact current model for AlGaN/GaN HEMTs. *IEEE Electron Device Lett.* **2015**, *36*, 108–110. [CrossRef]

- Radhakrishna, U.; Choi, P.; Grajal, J.; Peh, L.S.; Palacios, T.; Antoniadis, D. Study of RF-circuit linearity performance of GaN HEMT technology using the MVSG compact device model. In Proceedings of the 2016 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016.

- 12. Dambrine, G.; Cappy, A.; Heliodore, F.; Playez, E. A new method for determining the FET small-signal equivalent circuit. *IEEE Trans. Microw. Theory Tech.* **1988**, *36*, 1151–1159. [CrossRef]

- 13. Jarndal, A.; Kompa, G. A new small-signal modeling approach applied to GaN devices. *IEEE Trans. Microw. Theory Tech.* **2005**, *53*, 3440–3448. [CrossRef]

- Jia, Y.; Xu, Y.; Xu, R.; Li, Y. An accurate parasitic parameters extraction method based on FW-EM for AlGaN/GaN HEMT up to 110 GHz. Int. J. Numer. Model. Electron. Netw. Devices Fields 2018, 31, e2270. [CrossRef]

- Wen, Z.; Xu, Y.; Chen, Y.; Tao, H.; Ren, C.; Lu, H.; Wang, Z.; Zheng, W.; Zhang, B.; Chen, T.; et al. A quasi-physical compact large-signal model for AlGaN/GaN HEMTs. *IEEE Trans. Microw. Theory Tech.* 2017, 65, 5113–5122. [CrossRef]

- 16. Wu, Q.; Xu, Y.; Chen, Y.; Wang, Y.; Fu, W.; Yan, B.; Xu, R. A scalable multiharmonic surface-potential model of AlGaN/GaN HEMTs. *IEEE Trans. Microw. Theory Tech.* **2018**, *66*, 1192–1200. [CrossRef]

- Crupi, G.; Xiao, D.; Schreurs, D.M.M.P.; Limiti, E.; Caddemi, A.; Raedt, W.D.; Germain, M. Accurate multibias equivalent-circuit extraction for GaN HEMTs. *IEEE Trans. Microw.Theory Tech.* 2006, 54, 3616–3622. [CrossRef]

- Jardel, O.; Groote, F.D.; Reveyrand, T.; Jacquet, J.C.; Charbonniaud, C.; Teyssier, J.P.; Floriot, D.; Quere, R. An electrothermal model for AlGaN/GaN power HEMTs including trapping effects to improve large-signal simulation results on high VSWR. *IEEE Trans. Microw. Theory Tech.* 2007, *55*, 2660–2669. [CrossRef]

- Liu, L.S.; Ma, J.G.; Ng, G.I. Electrothermal large-signal model of III–V FETs including frequency dispersion and charge conservation. *IEEE Trans. Microw. Theory Tech.* 2009, 57, 3106–3117.

- Zhao, X.; Xu, Y.; Jia, Y.; Wu, Y.; Xu, R.; Li, J.; Hu, Z.; Wu, H.; Dai, W.; Cai, S. Temperature-dependent access resistances in large-signal modeling of millimeter-wave AlGaN/GaN HEMTs. *IEEE Trans. Microw. Theory Tech.* 2017, 65, 2271–2278. [CrossRef]

- Wang, C.; Xu, Y.; Yu, X.; Ren, C.; Wang, Z.; Lu, H.; Chen, T.; Zhang, B.; Xu, R. An electrothermal model for empirical large-signal modeling of AlGaN/GaN HEMTs including self-heating and ambient temperature effects. *IEEE Trans. Microw. Theory Tech.* 2014, 62, 2878–2887. [CrossRef]

- Xu, Y.; Wang, C.; Sun, H.; Wen, Z.; Wu, Y.; Xu, R.; Yu, X.; Ren, C.; Wang, Z.; Zhang, B.; et al. A scalable large-signal multiharmonic model of AlGaN/GaN HEMTs and its application in C-band high power amplifier MMIC. *IEEE Trans. Microw. Theory Tech.* 2017, 65, 2836–2846. [CrossRef]

- Joshin, K.; Ozaki, S.; Ohki, T.; Okamoto, N.; Niida, Y.; Makiyama, K. Millimeter-wave GaN HEMT model with VDS dependence of CDS for power amplifier applications. In Proceedings of the 2014 Asia-Pacific Microwave Conference, Sendai, Japan, 4–7 November 2014; pp. 582–584.

- Cutivet, A.; Altuntas, P.; Defrance, N.; Okada, E.; Avramovic, V.; Lesecq, M.; Hoel, V.; Jaeger, J.C.D.; Boone, F.; Maher, H. Large-signal modeling up to W-band of AlGaN/GaN based high-electron-mobility transistors. In Proceedings of the 2015 10th European Microwave Integrated Circuits Conference (EuMIC), Paris, France, 7–8 September 2015; pp. 93–96.

- King, J.B.; Brazil, T.J. Nonlinear electrothermal GaN HEMT model applied to high-efficiency power amplifier design. *IEEE Trans. Microw. Theory Tech.* 2013, 61, 444–454. [CrossRef]

- Yuk, K.S.; Branner, G.R.; McQuate, D.J. A wideband multiharmonic empirical large-signal model for high-power GaN HEMTs with self-heating and charge-trapping effects. *IEEE Trans. Microw. Theory Tech.* 2009, 57, 3322–3332. [CrossRef]

- Wen, Z.; Xu, Y.; Wang, C.; Zhao, X.; Chen, Z.; Xu, R. A parameter extraction method for GaN HEMT empirical large-signal model including self-heating and trapping effects. *Int. J. Numer. Model. Electron. Netw. Devices Fields* 2017, 30, e2137. [CrossRef]

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Article

### AlGaN/GaN High Electron Mobility Transistors on Semi-Insulating Ammono-GaN Substrates with Regrown Ohmic Contacts

Wojciech Wojtasiak <sup>1,\*</sup>, Marcin Góralczyk <sup>1</sup>, Daniel Gryglewski <sup>1</sup>, Marcin Zając <sup>2</sup>, Robert Kucharski <sup>2</sup>, Paweł Prystawko <sup>3,4</sup>, Anna Piotrowska <sup>5,\*</sup>, Marek Ekielski <sup>5</sup>, Eliana Kamińska <sup>5,\*</sup>, Andrzej Taube <sup>5</sup> and Marek Wzorek <sup>5</sup>

- <sup>1</sup> Institute of Radioelectronics and Multimedia Technology, Warsaw University of Technology, Nowowiejska 15/19, 00-662 Warsaw, Poland; M.Goralczyk@ire.pw.edu.pl (M.G.); dgrygle@ire.pw.edu.pl (D.G.)

- <sup>2</sup> Ammono Lab, Institute of High Pressure Physics, Polish Academy of Sciences, Sokołowska 29/37, 01-142 Warsaw, Poland; zajac@ammono.com (M.Z.); kucharski@ammono.com (R.K.)

- <sup>3</sup> TopGaN Ltd., Sokołowska 29/37, 01-142 Warsaw, Poland; pawel.prystawko@unipress.waw.pl

- <sup>4</sup> Institute of High Pressure Physics, Polish Academy of Sciences, Sokołowska 29/37, 01-142 Warsaw, Poland

- <sup>5</sup> Institute of Electron Technology, Al. Lotników 32/46, 02-668 Warsaw, Poland; ekielski@ite.waw.pl (M.E.); ataube@ite.waw.pl (A.T.); mwzorek@ite.waw.pl (M.W.)

- \* Correspondence: wwojtas@ire.pw.edu.pl (W.W.); ania@ite.waw.pl (A.P.); eliana@ite.waw.pl (E.K.); Tel.: +48-22-548-7940 (A.P.)

Received: 30 September 2018; Accepted: 21 October 2018; Published: 25 October 2018

MDP

**Abstract:** AlGaN/GaN high electron mobility transistors on semi-insulating bulk ammonothermal GaN have been investigated. By application of regrown ohmic contacts, the problem with obtaining low resistance ohmic contacts to low-dislocation high electron mobility transistor (HEMT) structures was solved. The maximum output current was about 1 A/mm and contact resistances was in the range of 0.3–0.6  $\Omega$ ·mm. Good microwave performance was obtained due to the absence of parasitic elements such as high access resistance.

**Keywords:** high electron mobility transistors; high electron mobility transistor (HEMT); AlGaN/GaN; ohmic contact; regrown contact; ammonothermal GaN; power amplifier

### 1. Introduction

There is a consensus in the nitride community that, although several GaN-based devices have already reached the market, their properties are still inferior with respect to predicted performance [1]. There are still many technological issues to be faced in order to fully exploit the enormous potential of these materials. The main limitations come from the lack of large area native bulk GaN substrates of reasonable cost and quality for homoepiaxial growth; some other issues concern device processing. Here, reliable low resistance homogeneous Ohmic contacts being fundamental building blocks of GaN devices are highly required.

In the quest to push the performance limit of AlGaN/GaN high electron mobility transistors (HEMTs), our work on advanced devices focuses on two main areas: development of epitaxial growth of HEMT structures on low defect density and high quality bulk ammonothermal semiinsulating GaN and fabrication of compatible nonalloyed ohmic contacts with subcontact  $n^+$ -In<sub>x</sub>Ga<sub>1-x</sub>N:Si epilayer regrown by metal organic vapor phase epitaxy (MOVPE).

The AlGaN/GaN HEMT structures for high power applications are usually grown on silicon carbide substrates [2], but recently there has been significant progress in developing high quality

GaN substrates with low defect density using hydride vapor phase epitaxy and ammonothermal growth techniques [3–7]. In particular, truly bulk ammonothermal GaN substrates could be used for homoepitaxy of transistor active layers characterized by excellent crystal quality and low surface roughness due to low threading dislocation density at the order of  $1 \times 10^4$  cm<sup>-2</sup> [8] and negligible bow. This can lead to improved reliability, radiation hardness, high yield and repeatability of the parameters of the final devices [9–12].

In addition, due to the reliability and performance issues, the problem of self-heating and heat dissipation inside the epitaxial structure of GaN-based HEMTs is especially important for high power devices. While the thermal conductivity is higher for 4H-SiC than for bulk GaN, the heat flow inside typical GaN-based HEMT on the SiC substrate is significantly limited because of the presence of nucleation layers (e.g., AIN) between epilayers and SiC substrate. This effect is commonly called thermal boundary resistance (TBR) [13]. Dislocations at the interfaces have a large share in the TBR [14]. In the case of AlGaN/GaN structure grown on the bulk gallium nitride, the thermal resistance of GaN-based HEMT is only determined by the thermal conductivity of bulk GaN, and temperature rise under operating conditions can be comparable to that in devices on SiC substrates [15].

While preliminary results on some aspects of device technology were reported [16], AlGaN/GaN HEMTs on ammonothermal GaN substrates with satisfying DC and RF parameters have not yet been published. Moreover, difficulties in obtaining low resistivity ohmic contacts to HEMT structures made on a substrate with a lower dislocation density were reported [17]. In this work, we present AlGaN/GaN high electron mobility transistors on semi-insulating bulk ammonothermal GaN substrates with nonalloyed regrown ohmic contacts. By using metal organic vapor phase epitaxy (MOVPE)-regrown highly-doped n<sup>+</sup>-In<sub>x</sub>Ga<sub>1-x</sub>N:Si layers, low resistivity ohmic contacts ( $R_c \sim 0.3-0.6 \ \Omega \cdot mm$ ) and high output current (1 A/mm) along with satisfying RF parameters are obtained.

### 2. Experimental Details

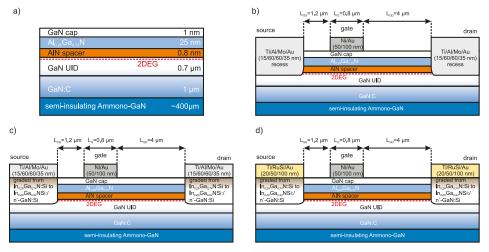

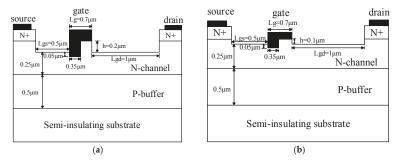

HEMT structures used in this study (see Figure 1a) were grown on a 1-inch c-plane, ~400  $\mu$ m thick, semi-insulating ammonothermal bulk GaN (SI Ammono-GaN) substrates. The resistivity of semi-insulating Ammono-GaN is typically no less than 10<sup>9</sup>  $\Omega$ ·cm in paralel direction to the c-axis, as measured by frequency domain capacitive technique [18,19], and over 1 × 10<sup>6</sup>  $\Omega$ ·cm (above the measurement method range) in the perpendicular direction to c-axis, as determined by microwave methods [19,20].

High resistivity of SI Ammono-GaN substrates are obtained by compensation of residual oxygen, incorporated during ammonothermal growth, by deep acceptors i.e., transition metal ions or by Mg shallow acceptors. It is worth to noting that a low level of impurities ( $\sim 2 \times 10^{18}$  cm<sup>-3</sup>) contributes to the high value of room temperature thermal conductivity of semi-insulating Ammono-GaN ( $\kappa \sim 230$  W/mK) [21]. The HEMT structure was grown by MOVPE. It consists of 1 nm GaN-cap, 25 nm Al<sub>0.26</sub>Ga<sub>0.73</sub>N barrier layer, 0.8 nm AlN spacer, 0.7 µm unintentionally doped (UID) GaN and 1 µm GaN:C highly resistive buffer. As shown in Figure 1a a dotted line indicates the position of two-dimensional electron gas (2DEG) formed in the quantum well at AlN spacer/UID GaN interface.

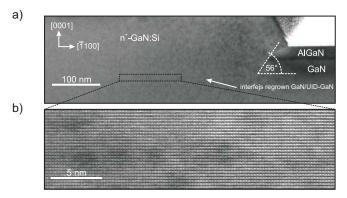

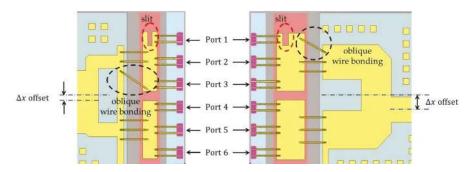

The high resolution  $2\theta - \omega$  and rocking curve X-ray diffraction (XRD) scans of epilayers (Figure 2a) prove the excellent crystal quality of epilayers grown on SI Ammono-GaN with FWHM = 0.007°. Atomic force microscopy (AFM) scans (5 µm × 5 µm) of the top of AlGaN/GaN HEMT structure shows an atomically smooth surface with a root mean square roughness of about 0.12–0.14 nm (Figure 2b). Electrical parameters of 2DEG were obtained by Hall effect and C-V measurements. Sheet resistivity ( $R_{sh}$ ), sheet carrier concentration ( $n_s$ ) and Hall mobility ( $\mu$ ) were 315  $\Omega/\Box$ , 1.64 × 10<sup>13</sup> cm<sup>-2</sup> and 1210 cm<sup>2</sup>/Vs, respectively.

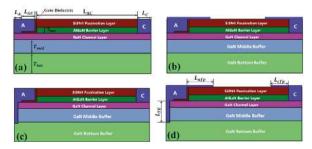

**Figure 1.** Cross-sectional schematics of the AlGaN/GaN-on-Ammono GaN high electron mobility transistors (HEMTs) under study: semiconductor device structure (**a**) and HEMT layouts with recessed Ti/Al/Mo/Au ohmic contact; (**b**) with subcontact  $n^+$ -In<sub>x</sub>Ga<sub>1-x</sub>N:Si regrown epilayer and Ti/Al/Mo/Au ohmic contact (**c**), and with subcontact  $n^+$ -In<sub>x</sub>Ga<sub>1-x</sub>N:Si regrown epilayer and Ti/RuSi/Au ohmic contact (**d**).

**Figure 2.** (a)  $2\theta$ - $\omega$  high resolution X-ray diffraction (XRD) scan and XRD rocking curve along with (b) AFM image of the surface of AlGaN/GaN HEMT structure on SI Ammono-GaN substrate.

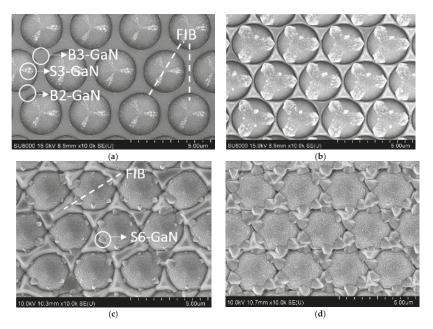

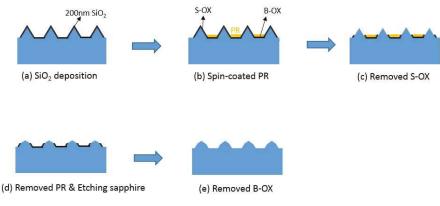

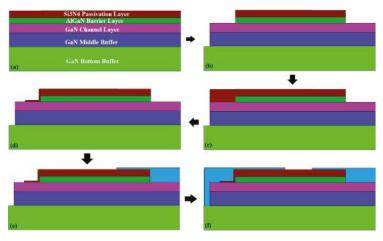

The first step of HEMT processing was the deposition on the semiconductor device structure a double-layer SiO<sub>x</sub> (200 nm)/AlN (35 nm) mask and its patterning for the selective recess etching of AlGaN/GaN followed by selective MOVPE regrowth of n<sup>+</sup>-In<sub>x</sub>Ga<sub>1-x</sub>N:Si/n<sup>+</sup>-GaN:Si subcontact regions of source and drain. The SiO<sub>x</sub> film was deposited using plasma-enhanced chemical vapor deposition (PECVD) and AlN layer was grown by MOVPE. Mask patterning was performed by BCl<sub>3</sub>/Ar and CHF<sub>3</sub>/CF<sub>4</sub> plasma etching. The depth of recess etching was 20 nm below the AlGaN layer. The doping and thickness of subcontact regrown region was as follows: n<sup>+</sup>-GaN:Si (Si:  $1.7 \times 10^{19}$  cm<sup>-3</sup>-40 nm,  $5 \times 10^{19}$  cm<sup>-3</sup>-7 nm) and graded (*x* from 8% to 26% at the top) n<sup>+</sup>-In<sub>x</sub>Ga<sub>1-x</sub>N:Si (Si:  $5 \times 10^{19}$  cm<sup>-3</sup>-10 nm). Schematic cross-section is presented in Figure 1c,d. To lower the surface barrier, doping of the first n<sup>+</sup>-GaN:Si layer was kept below Mott concentration, while the next 7 nm n<sup>+</sup>-GaN:Si layer was doped to the higher level of Si. For further lowering the surface barrier, n<sup>+</sup>-In<sub>x</sub>Ga<sub>1-x</sub>N:Si graded layer was doped to  $5 \times 10^{19}$  cm<sup>-3</sup> of Si and indium

composition was chosen in such a way that with 26% of In, the Fermi level is pinned to the conduction band.

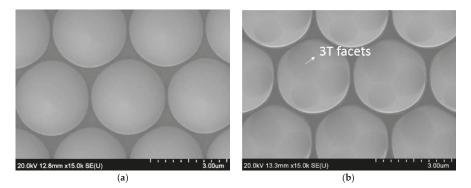

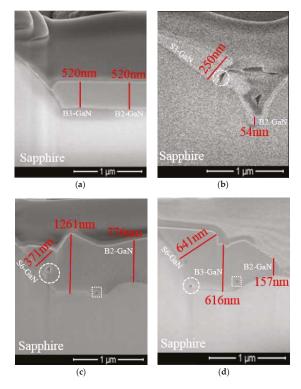

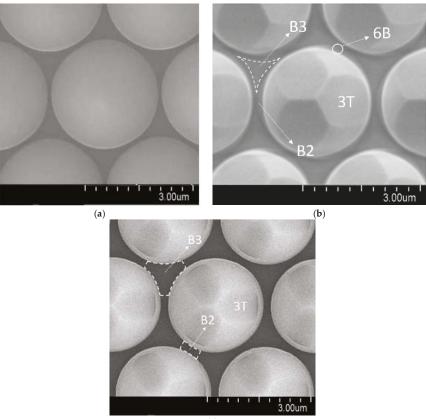

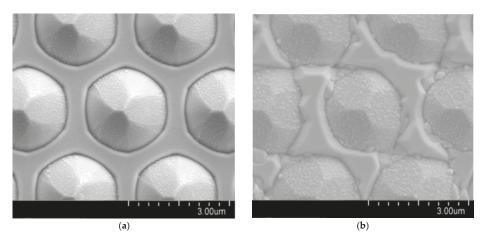

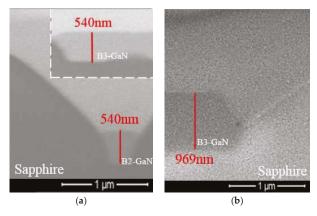

The AlN/SiO<sub>2</sub> mask was removed by soaking in hydrofluoric acid solution while regrown nitride films remained in contact regions. Figure 3 shows a cross-sectional transmission electron microscope (TEM) images of regrown GaN on top of a low-dislocation GaN homoepitaxial epilayer. High resolution imaging (HR-TEM) at Figure 3b reveals a smooth, dislocation-free n<sup>+</sup>-GaN/UID GaN interface, the key attribute of GaN on GaN technology. The etched sidewalls are at a 56° angle to the c-plane (0001). The sidewall angle is close to the optimal 62° angle at which the density of dangling bonds on the etched surface is similar to a c-plane surface [22].

Figure 3. (a) TEM image of  $n^+$ -In<sub>x</sub>Ga<sub>1-x</sub>N:Si/n<sup>+</sup>-GaN:Si subcontact region and (b) HR-TEM image of  $n^+$ -GaN:Si/UID GaN interface.

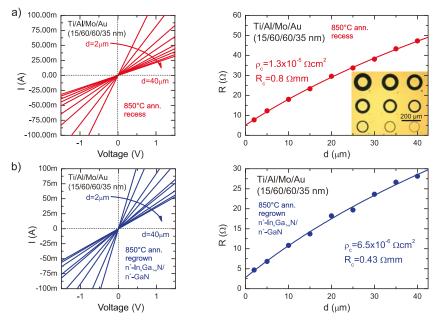

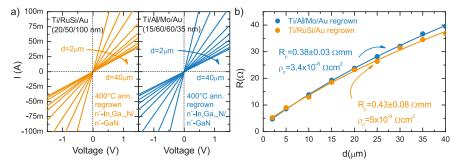

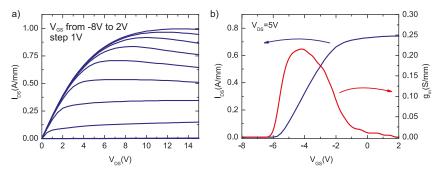

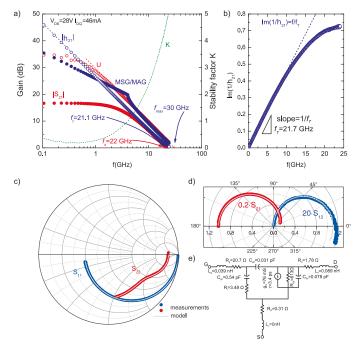

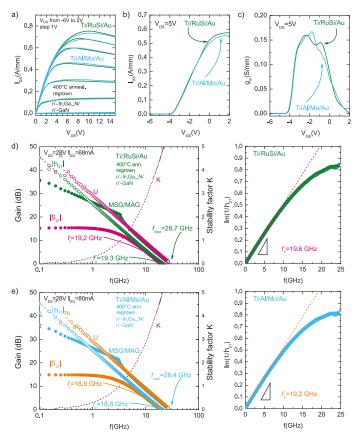

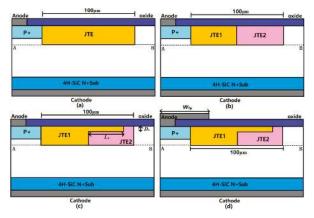

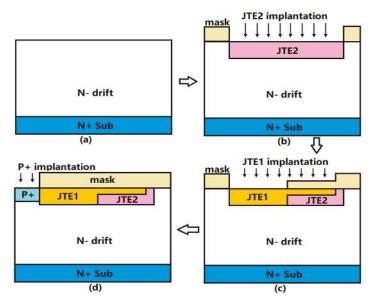

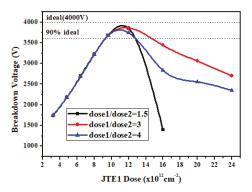

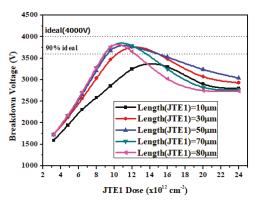

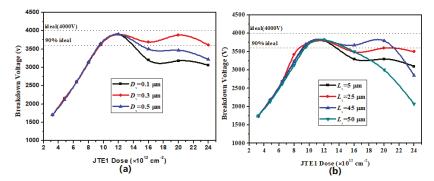

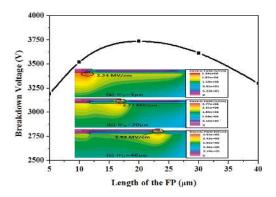

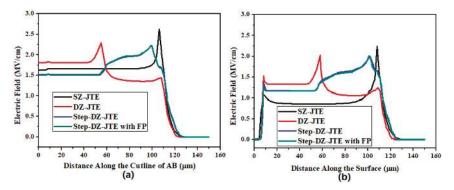

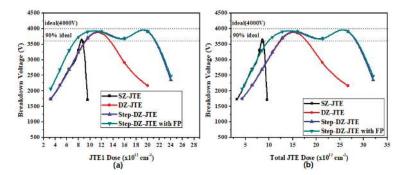

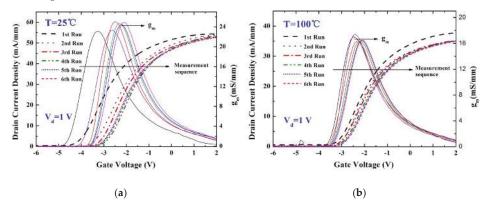

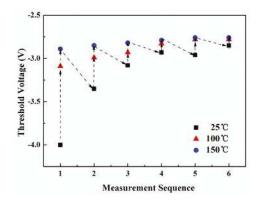

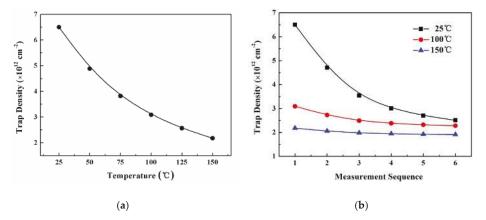

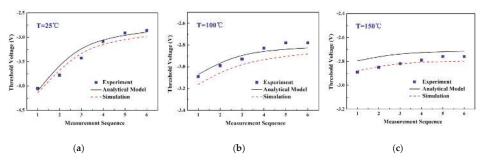

Next, the ohmic contact metallization was sputter-deposited and annealed. To compare the properties of alloyed and ohmic contacts, we studied the characteristics of conventional recessed Ti/Al/Mo/Au (15/60/60/35 nm) metallization annealed at 850 °C for 30 s in a nitrogen flow (Figure 1b) with contacts with subcontact n<sup>+</sup>-In<sub>x</sub>Ga<sub>1-x</sub>N:Si regrown epilayer metallized using conventional Ti/Al/Mo/Au (15/60/60/35 nm) (Figure 1c) or thermally stable Ti/RuSi/Au (20/50/100 nm) metallizations(Figure 1d).