## Worst-Case Execution Time Guarantees for Runtime-Reconfigurable Architectures

Zur Erlangung des akademischen Grades eines **Doktors der Ingenieurwissenschaften** der Fakultät für Informatik des Karlsruher Instituts für Technologie (KIT)

genehmigte

**Dissertation** von

Marvin Damschen aus Moers

| Tag der mündlichen Prüfung: | 19. Dezember 2018                         |

|-----------------------------|-------------------------------------------|

| Referent:                   | Prof. DrIng. Jörg Henkel                  |

|                             | Karlsruher Institut für Technologie (KIT) |

| Korreferent:                | Prof. Frank Mueller, Ph.D.                |

|                             | North Carolina State University (NCSU)    |

Marvin Damschen Burgstr. 110 76356 Weingarten (Baden)

Hiermit erkläre ich an Eides statt, dass ich die von mir vorgelegte Arbeit selbstständig verfasst habe, dass ich die verwendeten Quellen, Internetquellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit — einschließlich Tabellen, Karten und Abbildungen — die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

Marvin Damschen

## Acknowledgments

I would like to express my deep gratitude to my advisor Prof. Dr.-Ing. Jörg Henkel for believing in me from the beginning and providing an environment that was challenging and full of opportunities. I am thankful for his support and guidance, and the invaluable experience that he shared. By asking the right questions and supporting my ideas, he had a strong impact not only on the quality of my work, but especially on my development as a researcher.

I want to thank Prof. Frank Mueller from the North Carolina State University for agreeing to co-advise my thesis. I deeply appreciate our collaboration, which began when he welcomed me as a guest to his research lab, and his continuing support ever since.

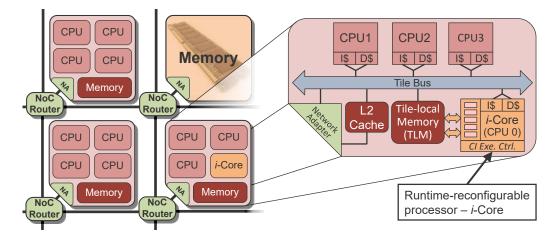

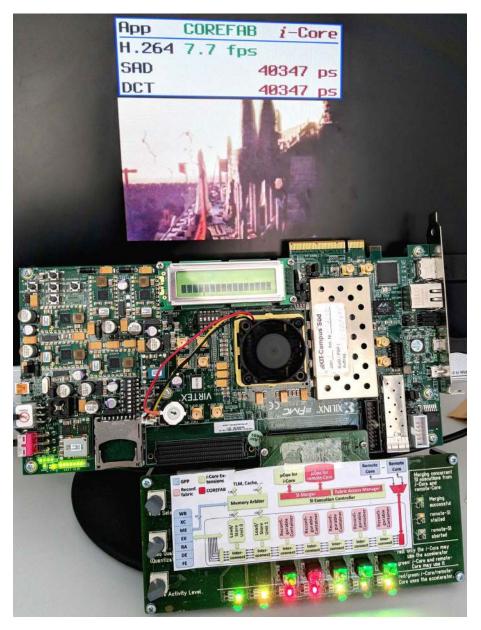

Dr.-Ing. Lars Bauer also had a big impact on my Ph.D. research and I want to express my sincere gratitude for all the time he invests into research projects that provide a great environment for doctoral researchers. The contributions he made during his Ph.D. are the basis for the evaluation platform that was used in this work. I also want to thank Dr.-Ing. Artjom Grudnisky for being a great help in technical and general aspects during the first months of my Ph.D. and helping me to kick-start my Ph.D. research. I further want to thank Dr.-Ing. Farzad Samie for answering all my questions about the Ph.D. defense and Martin Rapp for providing comments to my thesis.

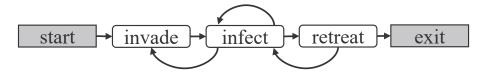

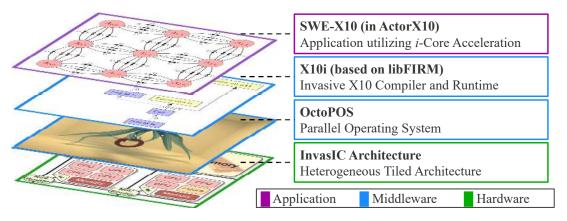

I was fortunate to be part of the Transregional Collaborative Research Center "Invasive Computing" (SFB/TR 89), which is funded by the German Research Foundation (DFG), and was a great source of experiences, collaborations and inspirations for me. In this context I want to express my gratitude to Andreas Fried, Dr.-Ing. Manuel Mohr, Alexander Pöppl, Sven Rheindt, Florian Schmaus and everyone else taking part in the integration of research ideas into a common prototype. The outstanding collaboration eventually allowed us to demonstrate a prototype of the full invasive computing technology stack during the review phase of Invasive Computing.

My thanks also go to Dr. Enrico Rossi, at the time a Ph.D. student of Prof. Dr. Giorgio Buttazzo from the Scuola Superiore Sant'Anna in Pisa, for visiting us and being a great collaborator in the area of runtime-reconfigurable real-time systems.

During my Ph.D. research I was able to supervise multiple student works and I want to thank all the students for the work that they put in and their contributions to prototypes.

Finally, I want to thank my family. I want to express my gratitude to my parents, who supported my interests and education however they could. My wife Katharina was not only understanding, but a continuing support during this journey. I want to express my deepest appreciation for her love and support.

Karlsruhe, January 2019

Thank you! Marvin Damschen

I should like to say two things, one intellectual and one moral:

The intellectual thing I should want to say to them is this: When you are studying any matter or considering any philosophy, ask yourself only what are the facts and what is the truth that the facts bear out. Never let yourself be diverted either by what you wish to believe or by what you think would have beneficent social effects if it were believed, but look only and solely at what are the facts. That is the intellectual thing that I should wish to say.

The moral thing I should wish to say to them is very simple. I should say: Love is wise, hatred is foolish. In this world, which is getting more and more closely interconnected, we have to learn to tolerate each other. We have to learn to put up with the fact that some people say things that we don't like. We can only live together in that way, and if we are to live together and not die together we must learn a kind of charity and a kind of tolerance which is absolutely vital to the continuation of human life on this planet.

- Bertrand Russel, Face to Face (BBC, 1959)

## Kurzfassung

Echtzeitsysteme sind in unserem Alltag allgegenwärtig, beispielsweise in sicherheitskritischen Umgebungen wie der Automobil- und Luftfahrtelektronik oder der Robotik. Die Korrektheit eines Echtzeitsystems hängt nicht nur von der Korrektheit der durchgeführten Berechnungen, sondern auch von der nicht-funktionalen Anforderung der Einhaltung von Deadlines ab. Wird eine Deadline nicht eingehalten, kann dies zu ernsthaften Fehlfunktionen führen. Daher müssen maximale Ausführungszeiten (*worst-case execution times*, WCET) garantiert werden. Trotz signifikanter wissenschaftlicher Fortschritte, können lediglich Mikroarchitekturen im Hinblick auf WCET Garantien analysiert werden, die der Entwicklung von aktuellen hochperformanten Mikroarchitekturen um Jahre hinterher sind. Zur Erfüllung der wachsenden Anforderung an Performance in Echtzeitsystemen, sind *analysierbare bare* Funktionen zur Performancesteigerung erforderlich. Um dem Mangel an analysierbaren Funktionen zur Performance unter WCET Garantien auf einem Field-Programmable Gate Array (FPGA) mit dem Ziel Performance unter WCET Garantien zu erreichen. Hierbei wird die Flexibilität des Systems aufrechterhalten und nicht etwa im Hinblick auf einen einzigen Anwendungsbereich eingeschränkt.

Zunächst trägt diese Dissertation in einer ausführlichen Analyse davon, wie (durchschnittliche) Performance auf *fused CPU-GPU Architekturen* erreicht wird, neuartige Ablaufplanungsansätze zur Arbeitsverteilung auf CPU und GPU bei. Fused CPU-GPU Architekturen sind aktuell eine der Hauptrichtungen innerhalb der Entwicklung von aktuellen hochperformanten Mikroarchitekturen, die eine CPU und eine GPU auf einem einzigen Chip vereint. Architekturen dieser Art für die Realisierung von Echzeitsystemen einsetzen zu können wäre überaus wünschenswert, da sie hohe Performance innerhalb eines beschränkten Flächen- und Leistungsbudgets bieten. Ein Ergebnis der präsentierten Analyse ist jedoch die Entdeckung eines Flaschenhalses in der Cache-Kohärenz von aktuellen fused CPU-GPU Architekturen, die den Last-Level-Cache zwischen CPU und GPU teilen. Dies führt dazu, dass (i) Performancevorhersagen erschwert werden und so (ii) ein geteilter Last-Level-Cache zwischen CPU und GPU der wachsenden Liste von Mikroarchitekturfunktionen hinzugefügt wird, die der durchschnittlichen Laufzeit nutzen, aber die Analyse von WCET Garantien auf hochperformanten Architekturen praktisch unmöglich machen. Somit wird der Bedarf an neuartigen Mikroarchitekturfunktionen für *vorhersagbare* Performance, die zugänglich für die Analyse von WCET Garantien sind, weitergehend motiviert.

Diesem Ziel folgend, wird ein Kontroller zur Steuerung von Laufzeitrekonfigurationen namens "Command-based Reconfiguration Queue" (CoRQ) präsentiert, der für seine Operationen garantierte Latenzen bietet. Dies gilt insbesondere für den *Rekonfigurationsdelay*, der Zeit die benötigt wird um einen Hardwarebeschleuniger auf einer rekonfigurierbaren Fläche (FPGA) zu konfigurieren. CoRQ ermöglicht das Design von zeitlich analysierbaren Architekturen, die WCET Garantien unterstützen. Basierend auf dem –nun möglichen– garantierten Rekonfigurationsdelay von Beschleunigern wird eine WCET Analyse eingeführt, die es Tasks ermöglicht applikationsspezifische *Spezialinstruktionen* (CIs) zur Laufzeit zu rekonfigurieren. CIs werden von einer Prozessorpipeline ausgeführt und stoßen die Ausführung von einem oder mehreren Beschleunigern an. Verschiedene Maßnahmen zur Behandlung von Rekonfigurationsdelay werden im Hinblick auf ihren Einfluss auf WCET Garantien und Überabschätzungen verglichen. Die *Timinganomalie der Laufzeitrekonfiguration* wird identifiziert und sicher beschränkt: einen Fall in dem das schnellere Ausführen von Iterationen eines Berechnungskernels als in WCET Garantien analysierbar sind die Laufzeitrekonfiguration von CIs durchführen, stellt sich die Frage *welche* CIs auf einer beschränkten rekonfigurierbaren Fläche zur Optimierung der WCET konfiguriert werden sollen. Diese Frage wird für Systeme behandelt, in denen mehrere CIs mit jeweils unterschiedlichen Implementierungen (die einen Trade-off zwischen Latenz und Flächenbedarf erlauben) ausgewählt werden können. Dies ist üblicherweise der Fall, beispielsweise wenn von High-Level Synthese Gebrauch gemacht wird. Dieses sogenannte Instruktionsselektionsproblem zur Optimierung der WCET wird basierend auf der Implicit Path Enumeration Technique (IPET) modelliert. IPET ist die Pfadanalysemethode auf die sich Timing Analyseprogramme stützen, die dem Stand der Technik entsprechen. Nach unserem Wissen ist dies der erste Ansatz von WCET Optimierung, der den Gebrauch von globalen Programmflussinformationen (und Informationen über Rekonfigurationsdelays) ermöglicht. Ein optimaler Algorithmus (der Branch-and-Bound ähnelt) und ein schneller heuristischer Algorithmus (der auf Greedy basiert und in den meisten Fällen die optimale Lösung erzielt) werden vorgestellt. Schließlich wird ein Ansatz präsentiert, der es erstmals ermöglicht die Optimierung von statischen WCET Garantien und die Optimierung der durchschnittlichen Ausführung zur Laufzeit (unter Einhaltung von WCET Garantien) mittels Laufzeitrekonfiguration von Hardwarebeschleunigern zu vereinen. Der Ansatz besteht aus einer Analyse von Schranken für Laufzeitslack (der Menge an Ausführungszeit, die ein Programmteil schneller als in WCET ausgeführt wird), die es auf sichere Weise ermöglichen Beschleuniger für die Optimierung durchschnittlicher Performance zu rekonfigurieren. Bestehende WCET Garantien bleiben hierbei erhalten. Weiterhin wird ein Mechanismus präsentiert, der es auf Basis von einfachen Performancezählern ermöglicht den Laufzeitslack zu überwachen. Die benötigten Performancezähler sind üblicherweise in vielen aktuellen Mikroprozessoren verfügbar.

Zusammenfassend zeigt diese Dissertation, dass Laufzeitrekonfiguration eine Schlüsselfunktionalität für das Erreichen von vorhersagbarer Performance ist.

## Abstract

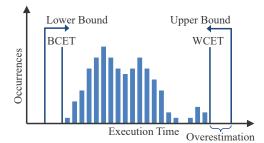

Real-time systems are ubiquitous in our everyday life, e.g., in safety-critical domains such as automotive, avionics or robotics. The correctness of a real-time system does not only depend on the correctness of its calculations, but also on the non-functional requirement of adhering to deadlines. Failing to meet a deadline may lead to severe malfunctions, therefore worst-case execution times (WCET) need to be guaranteed. Despite significant scientific advances, however, timing analysis of WCET guarantees lags years behind current high-performance microarchitectures with out-of-order scheduling pipelines, several hardware threads and multiple (shared) cache layers. To satisfy the increasing performance demands of real-time systems, analyzable performance features are required. In order to escape the scarcity of timing-analyzable performance features, the main contribution of this thesis is the introduction of runtime reconfiguration of hardware accelerators onto a field-programmable gate array (FPGA) as a novel means to achieve performance that is amenable to WCET guarantees. Instead of designing an architecture for a specific application domain, this approach preserves the flexibility of the system.

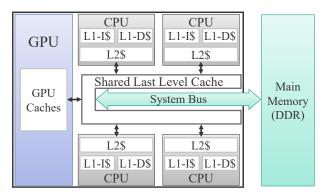

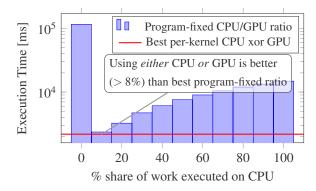

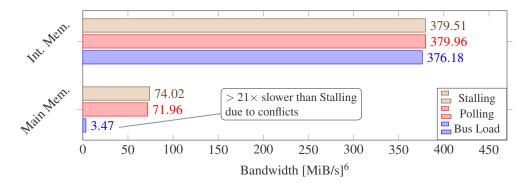

First, this thesis contributes novel co-scheduling approaches to distribute work among CPU and GPU in an extensive analysis of how (average-case) performance is achieved on *fused CPU-GPU architectures*, a main trend in current high-performance microarchitectures that combines a CPU and a GPU on a single chip. Being able to employ such architectures in real-time systems would be highly desirable, because they provide high performance within a limited area and power budget. As a result of this analysis, however, a cache coherency bottleneck is uncovered in recent fused CPU-GPU architectures that share the last level cache between CPU and GPU. This insight (i) complicates performance predictions and (ii) adds a shared last level cache between CPU and GPU to the growing list of microarchitectural features that benefit average-case performance, but render the analysis of WCET guarantees on high-performance architectures virtually infeasible. Thus, further motivating the need for novel microarchitectural features that provide *predictable* performance and are amenable to timing analysis.

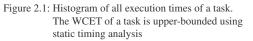

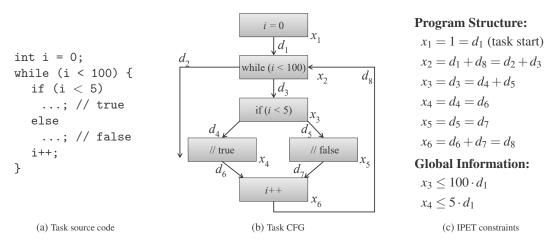

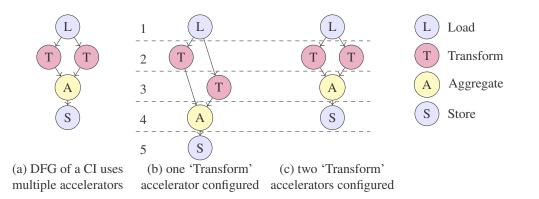

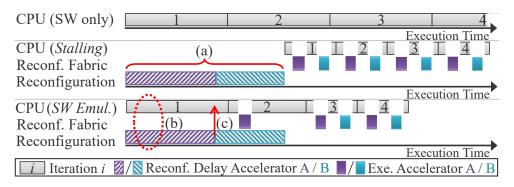

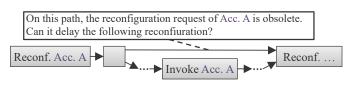

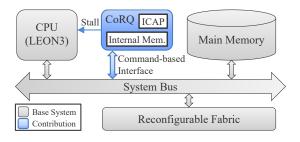

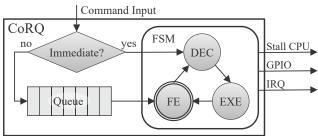

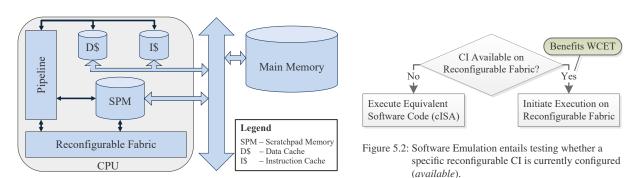

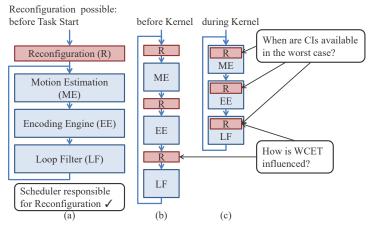

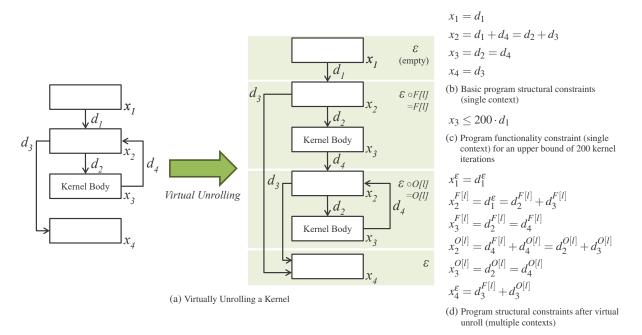

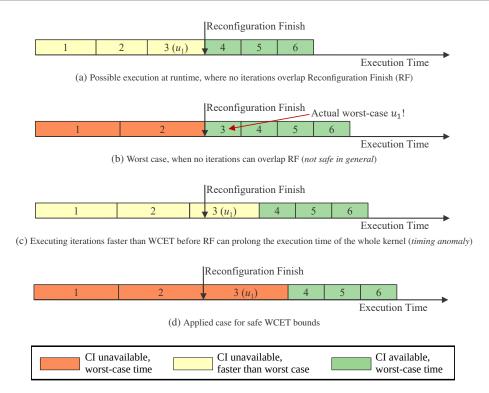

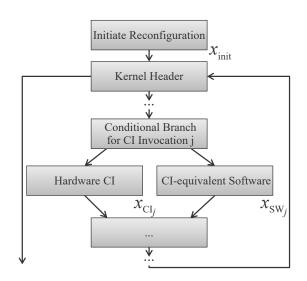

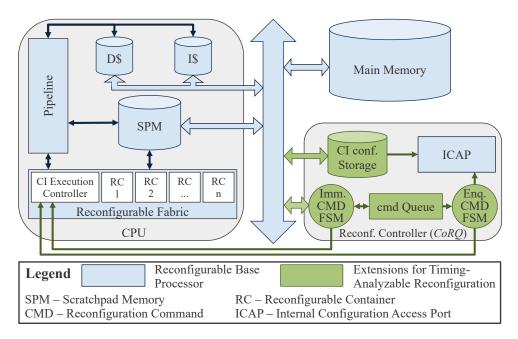

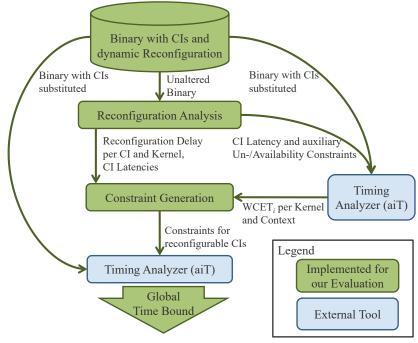

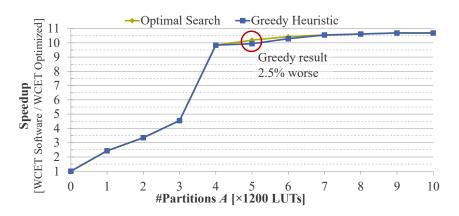

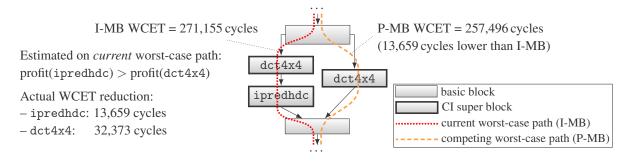

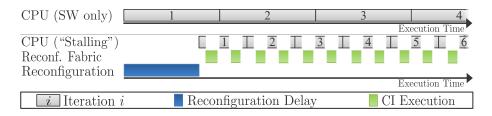

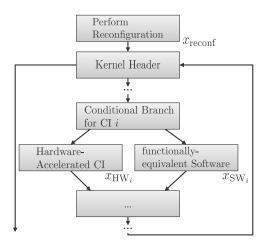

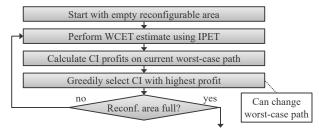

Towards this end, a runtime reconfiguration controller called "Command-based Reconfiguration Queue" (CoRQ) is presented that provides guaranteed latencies for its operations, especially for the *reconfiguration delay*, i.e., the time it takes to reconfigure a hardware accelerator onto a reconfigurable fabric (e.g., FPGA). CoRQ enables the design of timing-analyzable runtime-reconfigurable architectures that support WCET guarantees. Based on the -now feasible- guaranteed reconfiguration delay of accelerators, a WCET analysis is introduced that enables tasks to reconfigure application-specific custom instructions (CIs) at runtime. CIs are executed by a processor pipeline and invoke execution of one or more accelerators. Different measures to deal with reconfiguration delays are compared for their impact on accelerated WCET guarantees and overestimation. The timing anomaly of runtime reconfiguration is identified and safely bounded: a case where executing iterations of a computational kernel faster than in WCET during reconfiguration of CIs can prolong the total execution time of a task. Once tasks that perform runtime reconfiguration of CIs can be analyzed for WCET guarantees, the question of which CIs to configure on a constrained reconfigurable area to optimize the WCET is raised. The question is addressed for systems where multiple CIs with different implementations each (allowing to trade-off latency and area requirements) can be selected. This is generally the case, e.g., when employing high-level synthesis. This so-called WCET-optimizing instruction set selection problem is modeled based on the Implicit Path Enumeration Technique (IPET), which is the path analysis technique state-of-the-art timing analyzers rely on. To our knowledge, this is the first approach that enables WCET optimization with support for making use of global program flow information (and information about reconfiguration delay). An optimal algorithm (similar to Branch and Bound) and a fast greedy heuristic

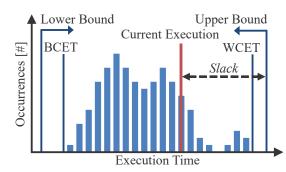

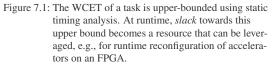

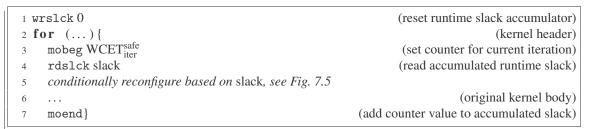

algorithm (that achieves the optimal solution in most cases) are presented. Finally, an approach is presented that, for the first time, combines optimized static WCET guarantees *and* runtime optimization of the average-case execution (maintaining WCET guarantees) using runtime reconfiguration of hardware accelerators by leveraging *runtime slack* (the amount of time that program parts are executed faster than in WCET). It comprises an analysis of runtime slack bounds that enable safe reconfiguration for average-case performance under WCET guarantees and presents a mechanism to monitor runtime slack using a simple performance counter that is commonly available in many microprocessors.

Ultimately, this thesis shows that runtime reconfiguration of accelerators is a key feature to achieve predictable performance.

## **Author's Contributions**

The following list enumerates journal, conference and workshop papers published by the author of this thesis while pursuing his doctorate at the Chair for Embedded Systems of the Karlsruhe Institute of Technology.

- Lars Bauer, Artjom Grudnitsky, Marvin Damschen, Srinivas Rao Kerekare, and Jörg Henkel. "Floating point acceleration for stream processing applications in dynamically reconfigurable processors". In: *IEEE Symp. on Embed. Syst. For Real-time Multimedia (ESTIMedia), Amsterdam, The Netherlands, October* 8-9, 2015. 2015, pp. 1–2. DOI: 10.1109/ESTIMedia.2015.7351762.

- [2] Marvin Damschen, Lars Bauer, and Jörg Henkel. "Extending the WCET Problem to Optimize for Runtime-Reconfigurable Processors". In: ACM Trans. on Archit. and Code Optim. (TACO) 13.4 (2016), 45:1–45:24. DOI: 10.1145/3014059.

- [3] Marvin Damschen, Lars Bauer, and Jörg Henkel. "CoRQ: Enabling Runtime Reconfiguration Under WCET Guarantees for Real-Time Systems". In: *IEEE Embedded Systems Letters (ESL)* 9.3 (2017), pp. 77– 80. DOI: 10.1109/LES.2017.2714844.

- [4] Marvin Damschen, Lars Bauer, and Jörg Henkel. "Timing Analysis of Tasks on Runtime Reconfigurable Processors". In: *IEEE Trans. on Very Large Scale Integration Syst. (TVLSI)* 25.1 (2017), pp. 294–307. DOI: 10.1109/TVLSI.2016.2572304.

- [5] Marvin Damschen, Frank Mueller, and Jörg Henkel. "Co-Scheduling on Fused CPU-GPU Architectures with Shared Last Level Caches". In: *IEEE Trans. on Comput.-Aided Design of Integrated Circuits and Syst.* (*TCAD*) (2018). ESWEEK Special Issue, to appear. DOI: 10.1109/TCAD.2018.2857042.

- [6] Tanja Harbaum, Christoph Schade, Marvin Damschen, Carsten Tradowsky, Lars Bauer, Jörg Henkel, and Jürgen Becker. "Auto-SI: An adaptive reconfigurable processor with run-time loop detection and acceleration". In: *IEEE Intl. System-on-Chip Conf., (SOCC), Munich, Germany, September 5-8, 2017.* 2017, pp. 153–158. DOI: 10.1109/SOCC.2017.8226027.

- [7] Alexander Pöppl, Marvin Damschen, Florian Schmaus, Andreas Fried, Manuel Mohr, Matthias Blankertz, Lars Bauer, Jörg Henkel, Wolfgang Schröder-Preikschat, and Michael Bader. "Shallow Water Waves on a Deep Technology Stack: Accelerating a Finite Volume Tsunami Model Using Reconfigurable Hardware in Invasive Computing". In: Workshop on UnConventional High Performance Computing (UCHPC), Santiago de Compostela, Spain, August 28-29, 2017, Revised Selected Papers. 2017, pp. 676–687. DOI: 10.1007/978-3-319-75178-8\_54.

- [8] Enrico Rossi, Marvin Damschen, Lars Bauer, Giorgio Buttazzo, and Jörg Henkel. "Preemption of the Partial Reconfiguration Process to Enable Real-Time Computing with FPGAs". In: ACM Trans. on Reconfig. Technol. and Syst. (TRETS) 11.2 (2018). to appear. DOI: 10.1145/3182183.

- [9] Stefan Wildermann, Michael Bader, Lars Bauer, Marvin Damschen, Dirk Gabriel, Michael Gerndt, Michael Gla

ß, J

örg Henkel, Johny Paul, Alexander P

öppl, Sascha Roloff, Tobias Schwarzer, Gregor Snelting, Walter Stechele, J

ürgen Teich, Andreas Weichslgartner, and Andreas Zwinkau. "Invasive computing for timing-predictable stream processing on MPSoCs". In: *it Information Technology* 58.6 (2016), pp. 267–280. DOI: 10.1515/itit-2016-0021.

The main focus of this thesis is on references [2–5], the contribution of Chapter 7 is currently under submission.

## **Selected Supervised Student Theses**

The following list enumerates selected student theses that were supervised by the author of this thesis and that contributed to prototyping and implementation of the evaluation platforms used in the following chapters.

- [i] Typke, Marc. "A SystemC/TLM-based Simulator for a Reconfigurable Heterogeneous Multi-core System", *Master Thesis*, 2016.

- [ii] Middelschulte, Leif. "Extending a WCET Estimation Tool for Runtime Reconfigurable Processors", *Master Thesis*, 2016.

- [iii] Eckhart, Artur. "A Command-Driven Reconfiguration Controller for Hard Real-Time Systems", *Bachelor Thesis*, 2016.

- [iv] Rapp, Martin. "A Mixed Criticality Architecture with Reconfigurable Accelerators", Master Thesis, 2016.

- [v] Blankertz, Matthias. "Extending the *i*-Core architecture for pipelined floating-point accelerators", *Diploma Thesis*, 2017.

- [vi] Maier, Eduard. "Heterogene Mehrkernprozessorunterstützung für i-Core", Diploma Thesis, 2017.

- [vii] Sader, Thomas. "Leveraging BCET Analysis to Improve WCET Estimates on Runtime Reconfigurable Processors", *Diploma Thesis*, 2017.

- [viii] Vutov, Petar. "A Linux Driver for the Reconfigurable Accelerator Queue Architecture", *Bachelor Thesis*, 2018.

- [ix] Münchbach, Florian. "Dynamic I/O configuration in a partially reconfigurable accelerator framework", *Master Thesis*, 2018.

# Contents

| 1.1       Thesis Contributions       2         2       Background       3         2.1       Real-Time Systems       3         2.2       Worst-Case Execution Time Analysis       4         2.1.1       Global Bound Analysis using IPET       5         2.3       Reconfigurable Computing       6         2.4       Evaluation Platform - <i>i</i> -Core       7         2.4.1       Microcoded Custom Instructions       7         2.5.2       SPP 1500       9         2.5.1       Invasive Computing       9         2.5.2       SPP 1500       10         3       Achieving Performance on Fused CPU-GPU Architectures with Shared Last Level Caches       11         3.1       Fused CPU-GPU Architectures       13         3.2.1       Co-Scheduling on Fused Architectures       13         3.2.1       Co-Scheduling on Fused Architectures       13         3.2.1       Co-Scheduling on Fused Architectures       13         3.2.2       Exploiting Shared Virtual Memory       13         3.3       Motivational Example       14         3.4.1       OpenCL       15         3.4.2       OpenCL 2.0       15         3.5.1       Memory Allocation       <                                                                                    | 1                             | Introduction |                                                                                   |           |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--------------|-----------------------------------------------------------------------------------|-----------|--|--|--|

| 2.1       Real-Time Systems       3         2.2       Worst-Case Execution Time Analysis       4         2.2.1       Global Bound Analysis using IPET       5         2.3       Reconfigurable Computing       6         2.4       Evaluation Platform – <i>i</i> -Core       7         2.4.1       Microcoded Custom Instructions       7         2.4.1       Microcoded Custom Instructions       7         2.5       Associated Research Projects       9         2.5.1       Invasive Computing       9         2.5.2       SPP 1500       10         3       Achieving Performance on Fused CPU-GPU Architectures with Shared Last Level Caches       11         3.1       Fused CPU-GPU Architectures       13         3.2.1       Co-Scheduling on Fused Architectures       13         3.2.2       Exploiting Shared Virtual Memory       13         3.3       Motivational Example       14         3.4       Background on Heterogeneous Execution using OpenCL       14         3.4.1       OpenCL 2.0       15         3.5.1       Memory Allocation       16         3.5.2       Kernel Launch and Synchronization       16         3.5.3       Overcheads of Fine-Grained SVM       17     <                                                 |                               | 1.1          | Thesis Contributions                                                              | 2         |  |  |  |

| 2.1       Real-Time Systems       3         2.2       Worst-Case Execution Time Analysis       4         2.2.1       Global Bound Analysis using IPET       5         2.3       Reconfigurable Computing       6         2.4       Evaluation Platform – <i>i</i> -Core       7         2.4.1       Microcoded Custom Instructions       7         2.4.1       Microcoded Custom Instructions       7         2.5       Associated Research Projects       9         2.5.1       Invasive Computing       9         2.5.2       SPP 1500       10         3       Achieving Performance on Fused CPU-GPU Architectures with Shared Last Level Caches       11         3.1       Fused CPU-GPU Architectures       13         3.2.1       Co-Scheduling on Fused Architectures       13         3.2.2       Exploiting Shared Virtual Memory       13         3.3       Motivational Example       14         3.4       Background on Heterogeneous Execution using OpenCL       14         3.4.1       OpenCL 2.0       15         3.5.1       Memory Allocation       16         3.5.2       Kernel Launch and Synchronization       16         3.5.3       Overcheads of Fine-Grained SVM       17     <                                                 | 0                             | Dee          | leave and                                                                         | 2         |  |  |  |

| 2.2       Worst-Case Execution Time Analysis       4         2.2.1       Global Bound Analysis using IPET       5         2.3       Reconfigurable Computing       6         2.4       Evaluation Platform - i-Core       7         2.4.1       Microcoded Custom Instructions       7         2.5       Associated Research Projects       9         2.5.1       Invasive Computing       9         2.5.2       SPP 1500       10         3       Achieving Performance on Fused CPU-GPU Architectures with Shared Last Level Caches       11         3.1       Fused CPU-GPU Architectures       11         3.2       Related Work       13         3.2.1       Co-Scheduling on Fused Architectures       13         3.2.2       Exploiting Shared Virtual Memory       13         3.3       Motivational Example       14         3.4       Background on Heterogeneous Execution using OpenCL       15         3.4.2       OpenCL 2.0       15         3.5.3       Utilizing Fine-Grained SVM on Fused CPU-GPU Architectures       16         3.5.1       Memory Allocation       16         3.5.2       Kernel Launch and Synchronization       16         3.5.3       Overcheads of Fine-Grained SVM                                                | 2                             |              |                                                                                   |           |  |  |  |

| 2.2.1       Global Bound Analysis using IPET       5         2.3       Reconfigurable Computing       6         2.4       Evaluation Platform – <i>i</i> -Core       7         2.4.1       Microcoded Custom Instructions       7         2.5       Associated Research Projects       9         2.5.1       Invasive Computing       9         2.5.2       SPP 1500       10         3       Achieving Performance on Fused CPU-GPU Architectures with Shared Last Level Caches       11         3.1       Fused CPU-GPU Architectures       11         3.2       Related Work       13         3.2.1       Co-Scheduling on Fused Architectures       13         3.2.2       Exploiting Shared Virtual Memory       13         3.3.3       Motivational Example       14         3.4       Background on Heterogeneous Execution using OpenCL       15         3.4.1       OpenCL       15         3.4.2       OpenCL 2.0       15         3.5.3       Utilizing Fine-Grained SVM on Fused CPU-GPU Architectures       16         3.5.1       Memory Allocation       16         3.5.2       Kernel Launch and Synchronization       16         3.5.3       Overheads of Fine-Grained SVM       17     <                                                 |                               |              |                                                                                   |           |  |  |  |

| 2.3Reconfigurable Computing62.4Evaluation Platform - $i$ -Core72.4.1Microcoded Custom Instructions72.5Associated Research Projects92.5.1Invasive Computing92.5.2SPP 1500103Achieving Performance on Fused CPU-GPU Architectures with Shared Last Level Caches113.1Fused CPU-GPU Architectures113.2Related Work133.2.1Co-Scheduling on Fused Architectures133.2.2Exploiting Shared Virtual Memory133.3Motivational Example143.4Background on Heterogeneous Execution using OpenCL143.4.1OpenCL153.4.2OpenCL 2.0153.5Utilizing Fine-Grained SVM on Fused CPU-GPU Architectures163.5.1Memory Allocation163.5.2Kernel Launch and Synchronization163.5.3Overheads of Fine-Grained SVM173.6Our Co-Scheduling Methods183.6.1Atomic Counting193.6.2Device-Side Enqueuing203.6.3Host-Side Profiling223.7.1Device-Side Enqueuing223.7.2Co-Scheduling Results of Rodinia-SVM223.7.3Cache Performance Bottlencek233.8Conclusion and Implications for Predictable Execution244Runtime Reconfiguration under WCET Guarantees274.1Challenges for a Guaranteed Reconf                                                                                                                                                                                                      |                               | 2.2          |                                                                                   |           |  |  |  |

| 2.4       Evaluation Platform - <i>l</i> -Core       7         2.4.1       Microcoded Custom Instructions       7         2.5       Associated Research Projects       9         2.5.1       Invasive Computing       9         2.5.2       SPP 1500       10         3       Achieving Performance on Fused CPU-GPU Architectures with Shared Last Level Caches       11         3.1       Fused CPU-GPU Architectures       11         3.2       Related Work       13         3.2.1       Co-Scheduling on Fused Architectures       13         3.2.2       Exploiting Shared Virtual Memory       13         3.3       Motivational Example       14         3.4       Background on Heterogeneous Execution using OpenCL       14         3.4.1       OpenCL 2.0       15         3.4.2       OpenCL 2.0       15         3.5.1       Memory Allocation       16         3.5.2       Kernel Launch and Synchronization       16         3.5.3       Overheads of Fine-Grained SVM       17         3.6       Our Co-Scheduling Methods       18         3.6.1       Atomic Counting       19         3.6.2       Device-Side Enqueuing       22         3.7.1       Dev                                                                               |                               |              |                                                                                   |           |  |  |  |

| 2.4.1       Microcoded Custom Instructions       7         2.5       Associated Research Projects       9         2.5.1       Invasive Computing       9         2.5.2       SPP 1500       10         3       Achieving Performance on Fused CPU-GPU Architectures with Shared Last Level Caches       11         3.1       Fused CPU-GPU Architectures       11         3.2       Related Work       13         3.2.1       Co-Scheduling on Fused Architectures       13         3.2.2       Exploiting Shared Virtual Memory       13         3.3       Motivational Example       14         3.4       Background on Heterogeneous Execution using OpenCL       14         3.4.1       OpenCL 2.0       15         3.4.2       QpenCL 2.0       15         3.5.1       Memory Allocation       16         3.5.2       Kernel Launch and Synchronization       16         3.5.3       Overheads of Fine-Grained SVM       17         3.6       Our Co-Scheduling Methods       18         3.6.1       Atomic Counting       19         3.6.2       Device-Side Enqueuing       20         3.6.3       Host-Side Profiling       21         3.7       Experimental                                                                                      |                               |              |                                                                                   |           |  |  |  |

| 2.5       Associated Research Projects       9         2.5.1       Invasive Computing       9         2.5.2       SPP 1500       10         3       Achieving Performance on Fused CPU-GPU Architectures with Shared Last Level Caches       11         3.1       Fused CPU-GPU Architectures       11         3.2       Related Work       13         3.2.1       Co-Scheduling on Fused Architectures       13         3.2.2       Exploiting Shared Virtual Memory       13         3.3       Motivational Example       14         3.4       Background on Heterogeneous Execution using OpenCL       14         3.4.1       OpenCL       15         3.4.2       OpenCL 2.0       15         3.5       Utilizing Fine-Grained SVM on Fused CPU-GPU Architectures       16         3.5.1       Memory Allocation       16         3.5.2       Kernel Launch and Synchronization       16         3.5.3       Overheads of Fine-Grained SVM       17         3.6       Our Co-Scheduling Methods       18         3.6.1       Atomic Counting       19         3.6.2       Device-Side Enqueuing       20         3.7.1       Device-Side Enqueuing       22         3.7.2 <th></th> <th colspan="4"></th>                                               |                               |              |                                                                                   |           |  |  |  |

| 2.5.1       Invasive Computing       9         2.5.2       SPP 1500       10         3       Achieving Performance on Fused CPU-GPU Architectures with Shared Last Level Caches       11         3.1       Fused CPU-GPU Architectures       11         3.2       Related Work       13         3.2.1       Co-Scheduling on Fused Architectures       13         3.2.2       Exploiting Shared Virtual Memory       13         3.3       Motivational Example       14         3.4       Background on Heterogeneous Execution using OpenCL       14         3.4.1       OpenCL       15         3.4.2       OpenCL 2.0       15         3.5       Utilizing Fine-Grained SVM on Fused CPU-GPU Architectures       16         3.5.1       Memory Allocation       16         3.5.2       Kernel Launch and Synchronization       16         3.5.3       Overheads of Fine-Grained SVM       17         3.6       Our Co-Scheduling Methods       18         3.6.1       Atomic Counting       19         3.6.2       Device-Side Enqueuing       20         3.7.1       Device-Side Enqueuing       22         3.7.2       Co-Scheduling Results of Rodinia-SVM       21         <                                                                        |                               |              |                                                                                   |           |  |  |  |

| 2.5.2       SPP 1500       10         3       Achieving Performance on Fused CPU-GPU Architectures with Shared Last Level Caches       11         3.1       Fused CPU-GPU Architectures       11         3.2       Related Work       13         3.2.1       Co-Scheduling on Fused Architectures       13         3.2.2       Exploiting Shared Virtual Memory       13         3.3       Motivational Example       14         3.4       Background on Heterogeneous Execution using OpenCL       14         3.4.1       OpenCL       15         3.4.2       OpenCL 2.0       15         3.5       Utilizing Fine-Grained SVM on Fused CPU-GPU Architectures       16         3.5.1       Memory Allocation       16         3.5.2       Kernel Launch and Synchronization       16         3.5.3       Overheads of Fine-Grained SVM       17         3.6       Our Co-Scheduling Methods       18         3.6.1       Atomic Counting       19         3.6.2       Device-Side Enqueuing       20         3.7.1       Device-Side Enqueuing       22         3.7.2       Co-Scheduling Results of Rodinia-SVM       22         3.7.3       Cache Performance Bottleneck       23      <                                                                |                               | 2.5          | 5                                                                                 | 9         |  |  |  |

| 3 Achieving Performance on Fused CPU-GPU Architectures with Shared Last Level Caches       11         3.1 Fused CPU-GPU Architectures       11         3.2 Related Work       13         3.2.1 Co-Scheduling on Fused Architectures       13         3.2.2 Exploiting Shared Virtual Memory       13         3.3 Motivational Example       14         3.4 Background on Heterogeneous Execution using OpenCL       14         3.4.1 OpenCL       15         3.4.2 OpenCL 2.0       15         3.5.1 Memory Allocation       16         3.5.2 Kernel Launch and Synchronization       16         3.5.2 Kernel Launch and Synchronization       16         3.5.3 Overheads of Fine-Grained SVM       17         3.6 Our Co-Scheduling Methods       18         3.6.1 Atomic Counting       20         3.6.2 Device-Side Enqueuing       20         3.7.1 Device-Side Enqueuing       22         3.7.2 Co-Scheduling Results of Rodinia-SVM       22         3.7.3 Cache Performance Bottleneck       23         3.8 Conclusion and Implications for Predictable Execution       24         4 Runtime Reconfiguration under WCET Guarantees       27         4.1 Challenges for a Guaranteed Reconfiguration Delay       27                                  |                               |              | 2.5.1 Invasive Computing                                                          | 9         |  |  |  |

| 3.1       Fused CPU-GPU Architectures       11         3.2       Related Work       13         3.2.1       Co-Scheduling on Fused Architectures       13         3.2.2       Exploiting Shared Virtual Memory       13         3.3       Motivational Example       14         3.4       Background on Heterogeneous Execution using OpenCL       14         3.4.1       OpenCL       15         3.4.2       OpenCL 2.0       15         3.5       Utilizing Fine-Grained SVM on Fused CPU-GPU Architectures       16         3.5.1       Memory Allocation       16         3.5.2       Kernel Launch and Synchronization       16         3.5.3       Overheads of Fine-Grained SVM       17         3.6       Our Co-Scheduling Methods       18         3.6.1       Atomic Counting       19         3.6.2       Device-Side Enqueuing       20         3.6.3       Host-Side Profiling       21         3.7       Experimental Evaluation       22         3.7.1       Device-Side Enqueuing       22         3.7.2       Co-Scheduling Results of Rodinia-SVM       22         3.7.3       Cache Performance Bottleneck       23         3.8       Conclusion an                                                                                     |                               |              | 2.5.2 SPP 1500                                                                    | .0        |  |  |  |

| 3.1       Fused CPU-GPU Architectures       11         3.2       Related Work       13         3.2.1       Co-Scheduling on Fused Architectures       13         3.2.2       Exploiting Shared Virtual Memory       13         3.3       Motivational Example       14         3.4       Background on Heterogeneous Execution using OpenCL       14         3.4.1       OpenCL       15         3.4.2       OpenCL 2.0       15         3.5       Utilizing Fine-Grained SVM on Fused CPU-GPU Architectures       16         3.5.1       Memory Allocation       16         3.5.2       Kernel Launch and Synchronization       16         3.5.3       Overheads of Fine-Grained SVM       17         3.6       Our Co-Scheduling Methods       18         3.6.1       Atomic Counting       19         3.6.2       Device-Side Enqueuing       20         3.6.3       Host-Side Profiling       21         3.7       Experimental Evaluation       22         3.7.1       Device-Side Enqueuing       22         3.7.2       Co-Scheduling Results of Rodinia-SVM       22         3.7.3       Cache Performance Bottleneck       23         3.8       Conclusion an                                                                                     | 3                             | Ach          | ieving Performance on Fused CPU-GPU Architectures with Shared Last Level Caches 1 | 1         |  |  |  |

| 3.2.1       Co-Scheduling on Fused Architectures       13         3.2.2       Exploiting Shared Virtual Memory       13         3.3       Motivational Example       14         3.4       Background on Heterogeneous Execution using OpenCL       14         3.4.1       OpenCL       14         3.4.2       OpenCL       15         3.4.2       OpenCL 2.0       15         3.5.1       Memory Allocation       16         3.5.2       Kernel Launch and Synchronization       16         3.5.3       Overheads of Fine-Grained SVM       17         3.6       Our Co-Scheduling Methods       18         3.6.1       Atomic Counting       19         3.6.2       Device-Side Enqueuing       20         3.6.3       Host-Side Profiling       21         3.7       Experimental Evaluation       22         3.7.1       Device-Side Enqueuing       22         3.7.2       Co-Scheduling Results of Rodinia-SVM       22         3.7.3       Cache Performance Bottleneck       23         3.8       Conclusion and Implications for Predictable Execution       24         4       Runtime Reconfiguration under WCET Guarantees       27         4.1       Chall                                                                                     |                               |              | -                                                                                 |           |  |  |  |

| 3.2.1       Co-Scheduling on Fused Architectures       13         3.2.2       Exploiting Shared Virtual Memory       13         3.3       Motivational Example       14         3.4       Background on Heterogeneous Execution using OpenCL       14         3.4.1       OpenCL       14         3.4.2       OpenCL 2.0       15         3.5.1       Memory Allocation       16         3.5.2       Kernel Launch and Synchronization       16         3.5.3       Overheads of Fine-Grained SVM       17         3.6       Our Co-Scheduling Methods       18         3.6.1       Atomic Counting       19         3.6.2       Device-Side Enqueuing       20         3.6.3       Host-Side Profiling       21         3.7       Experimental Evaluation       22         3.7.1       Device-Side Enqueuing       22         3.7.2       Co-Scheduling Results of Rodinia-SVM       22         3.7.3       Cache Performance Bottleneck       23         3.8       Conclusion and Implications for Predictable Execution       24         4       Runtime Reconfiguration under WCET Guarantees       27         4.1       Challenges for a Guaranteed Reconfiguration Delay       27                                                                    |                               | 3.2          | Related Work                                                                      | 3         |  |  |  |

| 3.2.2       Exploiting Shared Virtual Memory       13         3.3       Motivational Example       14         3.4       Background on Heterogeneous Execution using OpenCL       14         3.4.1       OpenCL       15         3.4.2       OpenCL 2.0       15         3.5.1       Utilizing Fine-Grained SVM on Fused CPU-GPU Architectures       16         3.5.1       Memory Allocation       16         3.5.2       Kernel Launch and Synchronization       16         3.5.3       Overheads of Fine-Grained SVM       17         3.6       Our Co-Scheduling Methods       18         3.6.1       Atomic Counting       20         3.6.2       Device-Side Enqueuing       20         3.6.3       Host-Side Profiling       21         3.7       Experimental Evaluation       22         3.7.1       Device-Side Enqueuing       22         3.7.2       Co-Scheduling Results of Rodinia-SVM       22         3.7.3       Cache Performance Bottleneck       23         3.8       Conclusion and Implications for Predictable Execution       24         4       Runtime Reconfiguration under WCET Guarantees       27         4.1       Challenges for a Guaranteed Reconfiguration Delay <td< th=""><th></th><th></th><th></th><th>3</th></td<> |                               |              |                                                                                   | 3         |  |  |  |

| 3.3       Motivational Example       14         3.4       Background on Heterogeneous Execution using OpenCL       14         3.4.1       OpenCL       15         3.4.2       OpenCL 2.0       15         3.5       Utilizing Fine-Grained SVM on Fused CPU-GPU Architectures       16         3.5.1       Memory Allocation       16         3.5.2       Kernel Launch and Synchronization       16         3.5.3       Overheads of Fine-Grained SVM       17         3.6       Our Co-Scheduling Methods       18         3.6.1       Atomic Counting       19         3.6.2       Device-Side Enqueuing       20         3.6.3       Host-Side Profiling       21         3.7       Experimental Evaluation       22         3.7.1       Device-Side Enqueuing       22         3.7.2       Co-Scheduling Results of Rodinia-SVM       22         3.7.3       Cache Performance Bottleneck       23         3.8       Conclusion and Implications for Predictable Execution       24         4       Runtime Reconfiguration under WCET Guarantees       27         4.1       Challenges for a Guaranteed Reconfiguration Delay       27                                                                                                               |                               |              |                                                                                   | 3         |  |  |  |

| 3.4       Background on Heterogeneous Execution using OpenCL       14         3.4.1       OpenCL       15         3.4.2       OpenCL 2.0       15         3.5       Utilizing Fine-Grained SVM on Fused CPU-GPU Architectures       16         3.5.1       Memory Allocation       16         3.5.2       Kernel Launch and Synchronization       16         3.5.3       Overheads of Fine-Grained SVM       17         3.6       Our Co-Scheduling Methods       18         3.6.1       Atomic Counting       19         3.6.2       Device-Side Enqueuing       20         3.6.3       Host-Side Profiling       21         3.7       Experimental Evaluation       22         3.7.1       Device-Side Enqueuing       22         3.7.2       Co-Scheduling Results of Rodinia-SVM       22         3.7.3       Cache Performance Bottleneck       23         3.8       Conclusion and Implications for Predictable Execution       24         4       Runtime Reconfiguration under WCET Guarantees       27         4.1       Challenges for a Guaranteed Reconfiguration Delay       27                                                                                                                                                               |                               | 3.3          |                                                                                   | 4         |  |  |  |

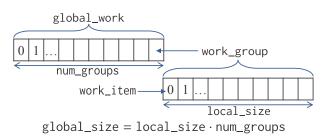

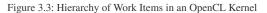

| 3.4.1       OpenCL       15         3.4.2       OpenCL 2.0       15         3.5       Utilizing Fine-Grained SVM on Fused CPU-GPU Architectures       16         3.5.1       Memory Allocation       16         3.5.2       Kernel Launch and Synchronization       16         3.5.3       Overheads of Fine-Grained SVM       17         3.6       Our Co-Scheduling Methods       18         3.6.1       Atomic Counting       19         3.6.2       Device-Side Enqueuing       20         3.6.3       Host-Side Profiling       21         3.7       Experimental Evaluation       22         3.7.1       Device-Side Enqueuing       22         3.7.2       Co-Scheduling Results of Rodinia-SVM       22         3.7.3       Cache Performance Bottleneck       23         3.8       Conclusion and Implications for Predictable Execution       24         4       Runtime Reconfiguration under WCET Guarantees       27         4.1       Challenges for a Guaranteed Reconfiguration Delay       27                                                                                                                                                                                                                                             |                               | -            |                                                                                   |           |  |  |  |

| 3.4.2OpenCL 2.0153.5Utilizing Fine-Grained SVM on Fused CPU-GPU Architectures163.5.1Memory Allocation163.5.2Kernel Launch and Synchronization163.5.3Overheads of Fine-Grained SVM173.6Our Co-Scheduling Methods183.6.1Atomic Counting193.6.2Device-Side Enqueuing203.6.3Host-Side Profiling213.7Experimental Evaluation223.7.1Device-Side Enqueuing223.7.2Co-Scheduling Results of Rodinia-SVM223.7.3Cache Performance Bottleneck233.8Conclusion and Implications for Predictable Execution244Runtime Reconfiguration under WCET Guarantees274.1Challenges for a Guaranteed Reconfiguration Delay27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                               |              |                                                                                   |           |  |  |  |

| 3.5       Utilizing Fine-Grained SVM on Fused CPU-GPU Architectures       16         3.5.1       Memory Allocation       16         3.5.2       Kernel Launch and Synchronization       16         3.5.3       Overheads of Fine-Grained SVM       17         3.6       Our Co-Scheduling Methods       18         3.6.1       Atomic Counting       19         3.6.2       Device-Side Enqueuing       20         3.6.3       Host-Side Profiling       21         3.7       Experimental Evaluation       22         3.7.1       Device-Side Enqueuing       22         3.7.2       Co-Scheduling Results of Rodinia-SVM       22         3.7.3       Cache Performance Bottleneck       23         3.8       Conclusion and Implications for Predictable Execution       24         4       Runtime Reconfiguration under WCET Guarantees       27         4.1       Challenges for a Guaranteed Reconfiguration Delay       27                                                                                                                                                                                                                                                                                                                         |                               |              |                                                                                   |           |  |  |  |

| 3.5.1Memory Allocation163.5.2Kernel Launch and Synchronization163.5.3Overheads of Fine-Grained SVM173.6Our Co-Scheduling Methods183.6.1Atomic Counting193.6.2Device-Side Enqueuing203.6.3Host-Side Profiling213.7Experimental Evaluation223.7.1Device-Side Enqueuing223.7.2Co-Scheduling Results of Rodinia-SVM223.7.3Cache Performance Bottleneck233.8Conclusion and Implications for Predictable Execution244Runtime Reconfiguration under WCET Guarantees274.1Challenges for a Guaranteed Reconfiguration Delay27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                               | *            |                                                                                   |           |  |  |  |

| 3.5.2       Kernel Launch and Synchronization       16         3.5.3       Overheads of Fine-Grained SVM       17         3.6       Our Co-Scheduling Methods       18         3.6.1       Atomic Counting       19         3.6.2       Device-Side Enqueuing       20         3.6.3       Host-Side Profiling       21         3.7       Experimental Evaluation       22         3.7.1       Device-Side Enqueuing       22         3.7.2       Co-Scheduling Results of Rodinia-SVM       22         3.7.3       Cache Performance Bottleneck       23         3.8       Conclusion and Implications for Predictable Execution       24         4       Runtime Reconfiguration under WCET Guarantees       27         4.1       Challenges for a Guaranteed Reconfiguration Delay       27                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                               | -            |                                                                                   |           |  |  |  |

| 3.5.3       Overheads of Fine-Grained SVM       17         3.6       Our Co-Scheduling Methods       18         3.6.1       Atomic Counting       19         3.6.2       Device-Side Enqueuing       20         3.6.3       Host-Side Profiling       21         3.7       Experimental Evaluation       22         3.7.1       Device-Side Enqueuing       22         3.7.2       Co-Scheduling Results of Rodinia-SVM       22         3.7.3       Cache Performance Bottleneck       23         3.8       Conclusion and Implications for Predictable Execution       24         4       Runtime Reconfiguration under WCET Guarantees       27         4.1       Challenges for a Guaranteed Reconfiguration Delay       27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                               |              |                                                                                   |           |  |  |  |

| 3.6       Our Co-Scheduling Methods       18         3.6.1       Atomic Counting       19         3.6.2       Device-Side Enqueuing       20         3.6.3       Host-Side Profiling       21         3.7       Experimental Evaluation       22         3.7.1       Device-Side Enqueuing       22         3.7.2       Co-Scheduling Results of Rodinia-SVM       22         3.7.3       Cache Performance Bottleneck       23         3.8       Conclusion and Implications for Predictable Execution       24         4       Runtime Reconfiguration under WCET Guarantees       27         4.1       Challenges for a Guaranteed Reconfiguration Delay       27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                               |              |                                                                                   |           |  |  |  |

| 3.6.1       Atomic Counting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.6 Our Co-Scheduling Methods |              |                                                                                   |           |  |  |  |

| 3.6.2       Device-Side Enqueuing       20         3.6.3       Host-Side Profiling       21         3.7       Experimental Evaluation       22         3.7.1       Device-Side Enqueuing       22         3.7.2       Co-Scheduling Results of Rodinia-SVM       22         3.7.3       Cache Performance Bottleneck       23         3.8       Conclusion and Implications for Predictable Execution       24         4       Runtime Reconfiguration under WCET Guarantees       27         4.1       Challenges for a Guaranteed Reconfiguration Delay       27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                               |              |                                                                                   |           |  |  |  |

| 3.6.3 Host-Side Profiling       21         3.7 Experimental Evaluation       22         3.7.1 Device-Side Enqueuing       22         3.7.2 Co-Scheduling Results of Rodinia-SVM       22         3.7.3 Cache Performance Bottleneck       23         3.8 Conclusion and Implications for Predictable Execution       24         4 Runtime Reconfiguration under WCET Guarantees       27         4.1 Challenges for a Guaranteed Reconfiguration Delay       27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                               |              |                                                                                   |           |  |  |  |

| 3.7 Experimental Evaluation       22         3.7.1 Device-Side Enqueuing       22         3.7.2 Co-Scheduling Results of Rodinia-SVM       22         3.7.3 Cache Performance Bottleneck       23         3.8 Conclusion and Implications for Predictable Execution       24         4 Runtime Reconfiguration under WCET Guarantees       27         4.1 Challenges for a Guaranteed Reconfiguration Delay       27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                               |              |                                                                                   |           |  |  |  |

| 3.7.1       Device-Side Enqueuing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                               | 27           |                                                                                   |           |  |  |  |

| 3.7.2       Co-Scheduling Results of Rodinia-SVM       22         3.7.3       Cache Performance Bottleneck       23         3.8       Conclusion and Implications for Predictable Execution       24         4       Runtime Reconfiguration under WCET Guarantees       27         4.1       Challenges for a Guaranteed Reconfiguration Delay       27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                               | 5.7          | -                                                                                 |           |  |  |  |

| 3.7.3       Cache Performance Bottleneck       23         3.8       Conclusion and Implications for Predictable Execution       24         4       Runtime Reconfiguration under WCET Guarantees       27         4.1       Challenges for a Guaranteed Reconfiguration Delay       27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                               |              |                                                                                   |           |  |  |  |

| 3.8       Conclusion and Implications for Predictable Execution       24         4       Runtime Reconfiguration under WCET Guarantees       27         4.1       Challenges for a Guaranteed Reconfiguration Delay       27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                               |              |                                                                                   |           |  |  |  |

| 4       Runtime Reconfiguration under WCET Guarantees       27         4.1       Challenges for a Guaranteed Reconfiguration Delay       27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                               | 2.0          |                                                                                   |           |  |  |  |

| 4.1 Challenges for a Guaranteed Reconfiguration Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                               | 3.8          | Conclusion and Implications for Predictable Execution                             | :4        |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4                             | Run          | time Reconfiguration under WCET Guarantees                                        | <b>:7</b> |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                               | 4.1          | Challenges for a Guaranteed Reconfiguration Delay                                 | 27        |  |  |  |

| 4.2 Enabling Runtime Reconfiguration in Real-Time Systems with CoRQ 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                               | 4.2          | Enabling Runtime Reconfiguration in Real-Time Systems with CoRQ 2                 | 29        |  |  |  |

|   |            | 4.2.1 Command Execution                                                      |         | <br> | <br>. 30 |

|---|------------|------------------------------------------------------------------------------|---------|------|----------|

|   |            | 4.2.2 Guaranteed Reconfiguration Delay                                       |         | <br> | <br>. 31 |

|   |            | 4.2.3 Analyzing Sequences of Commands                                        |         | <br> | <br>. 31 |

|   | 4.3        | B Experimental Evaluation                                                    |         | <br> | <br>. 32 |

|   | 4.4        | Conclusion                                                                   |         | <br> | <br>. 33 |

| 5 | WC         | CET Analysia of Tooks on Buntima Pasanfigurable Brassasara                   |         |      | . 35     |

| 5 |            | CET Analysis of Tasks on Runtime-Reconfigurable Processors .<br>Related Work |         |      |          |

|   | 5.1        |                                                                              |         |      |          |

|   |            |                                                                              |         |      |          |

|   | 5.0        | <u> </u>                                                                     |         |      |          |

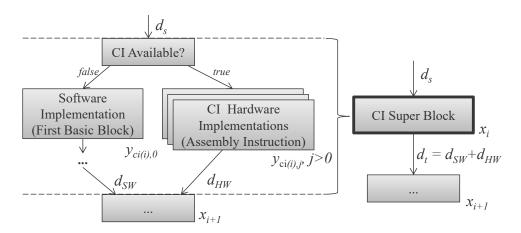

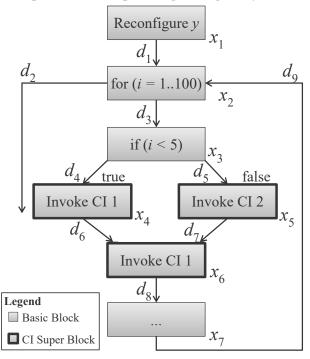

|   | 5.2        | r · · · · · · · · · · · · · · · · · · ·                                      |         |      |          |

|   | 5.3        |                                                                              |         |      |          |

|   | <b>5</b> 4 | 5.3.1 Path Analysis                                                          |         |      |          |

|   | 5.4        | 8                                                                            |         |      |          |

|   |            | 5.4.1 Microarchitectural Analysis                                            |         |      |          |

|   |            | 5.4.2 Path Analysis Constraints for Software Emulation                       |         |      |          |

|   |            | 5.4.3 Stalling vs. Software Emulation                                        |         |      |          |

|   | 5.5        | 6                                                                            |         |      |          |

|   | 5.6        | I                                                                            |         |      |          |

|   |            | 5.6.1 Implementation and Setup                                               |         |      |          |

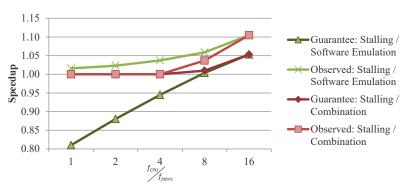

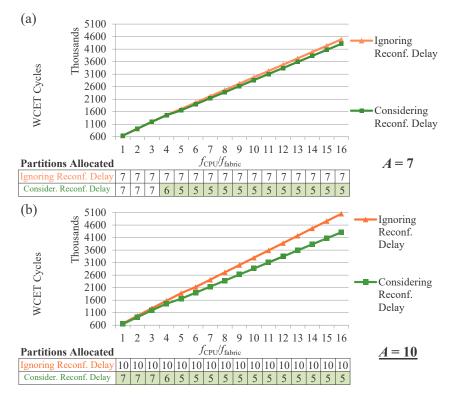

|   |            | 5.6.2 Results                                                                |         |      |          |

|   | 5.7        | 7 Conclusion                                                                 |         | <br> | <br>. 53 |

| 6 | WC         | CET Optimization using Reconfigurable Custom Instructions                    |         | <br> | <br>. 55 |

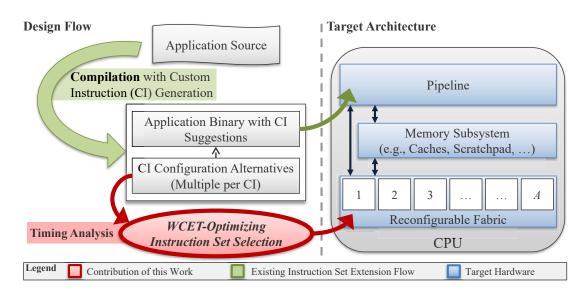

|   | 6.1        | Related Work and Motivation                                                  |         | <br> | <br>. 56 |

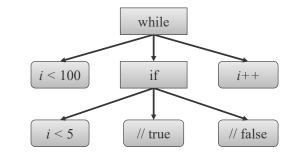

|   | 6.2        | 2 System Model                                                               |         | <br> | <br>. 58 |

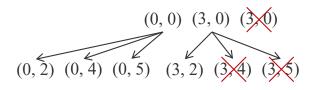

|   | 6.3        | Problem Formulation                                                          |         | <br> | <br>. 60 |

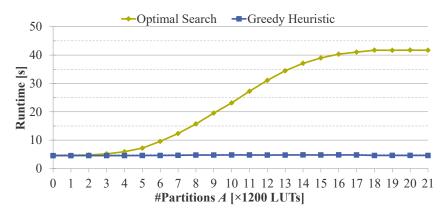

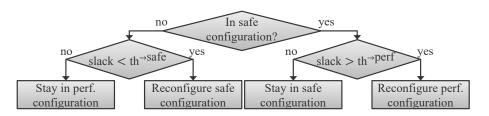

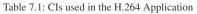

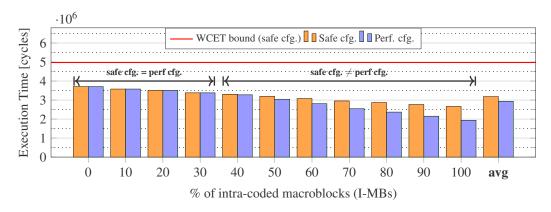

|   | 6.4        | Optimal Solution                                                             |         | <br> | <br>. 62 |