# Zero Voltage Switching Criteria of Triple Active Bridge Converter

Purgat, P.; Bandyopadhyay, S.; Qin, Z.; Bauer, P.

10.1109/TPEL.2020.3027785

**Publication date**

**Document Version** Accepted author manuscript

Published in

IEEE Transactions on Power Electronics

Citation (APA)

Purgat, P., Bandyopadhyay, S., Qin, Z., & Bauer, P. (2020). Zero Voltage Switching Criteria of Triple Active Bridge Converter. *IEEE Transactions on Power Electronics*, *36*(5), 5425-5439. [9208782]. https://doi.org/10.1109/TPEL.2020.3027785

## Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# Zero Voltage Switching Criteria of Triple Active Bridge Converter

Pavel Purgat<sup>‡</sup>, Soumya Bandyopadhyay<sup>‡</sup>, Zian Qin<sup>‡</sup>, and Pavol Bauer<sup>‡</sup>

<sup>‡</sup> DC Systems Energy Conversion & Storage, Faculty of Electrical Engineering, Mathematics, and Computer Science Delft University of Technology

Abstract—Triple active bridge (TAB) as an isolated multi-port converter is a promising integrated energy system for smart grids or electric vehicles. This paper aims to derive and analyse zero voltage switching (ZVS) regions of TAB, in which both switching losses are reduced, and EMI issues are mitigated. In the proposed closed-form solution of ZVS criteria, parameters such as the parasitic capacitance of the switches, the leakage inductance of the transformer, the switching frequency, the port voltage, the phase-shift inside and between the full-bridges are all taken into account. The analysis shows how the five degrees of freedom can be used to maintain ZVS operation in various operating points. The analysis and derived closed-form ZVS criteria are experimentally verified using a laboratory prototype. The derived analytical ZVS criteria are a powerful tool to study and optimise the operation of TAB converters.

Index Terms— bidirectional power flow, dc-dc converters,, triple active bridge, smart grids, zero voltage switching

#### I. Introduction

IGH penetration of renewable energy sources and storage in recent years brought increase interest in multi-port converters (MPC) as a potential solution for versatile energy management systems [1]. The MPCs can integrate multiple sources, storages, and loads with varied voltage and current ratings into a single power stage allowing multi-directional power flow between its ports. Therefore, potential applications for the MPCs range from electric vehicles [2], more-electric aircrafts [3], [4] to (dc) smart grids [5], [6].

Specific applications such as EV charging require galvanic isolation between the different ports due to safety [7]. Hence, a multi-winding high-frequency (HF) transformer is used to realize this galvanic isolation required for the MPCs. One of the promising topologies in the multi-winding transformer-coupled MPC family is the triple-active bridge (TAB) converter. The TAB converter is an MPC with three full bridges connected via a high frequency (HF) multi-winding transformer [7]–[9]. Derived from the dual-active bridge (DAB) converter family [10], the TAB converter integrates and exchanges the energy from/to all ports and provides full isolation among all ports and can match the different port voltage levels.

The basic TAB modulation uses 50% duty cycles on all three full bridges and uses the phase-shifts across the three

We thank Francesca Grazian for her assistance during the experimental validation of the study.

Corresponding Author: Zian Qin (z.qin-2@tudelft.nl) T +421 907395264, F +31 (0)152782969 Mekelweg 4, 2628CD Delft, The Netherlands

leakage inductors to transfer power between the ports [11]. However, operating with only two independent degrees of freedom leads to loss of soft-switching and high circulating currents in the HF link [11], [12]. Similarly, in DAB converters operating with a single phase-shift leads to loss of softswitching and higher current stress. Different dual phaseshifts modulations [13]-[15] and triple phase-shift modulations [16]–[18] were proposed for DAB to increase the operating efficiency. The soft-switching areas of DAB converters operated with all three degrees of freedom were identified using various approaches [19]-[25]. Firstly, many approaches use steady-state time-domain analysis or small-signal statespace modeling techniques [25], [26]. Using the time domain analysis DAB operation was characterized into twelve operating modes in [27] and later simplified into five operating modes using graphical method in [28]. Furthermore, computationally intensive numerical approaches that incorporate the effect of parasitic capacitances were used to derive ZVS boundaries [23]. Lastly, the impact of parasitic capacitance was taken into account using energy balance equations [24]. However, due to the higher number of degrees of freedom and superpositions of port voltages applied to a transformer, the TAB converters have several tens of operating modes. The complexity makes the use of graphical methods such as [28] or computational intensive methods such as [23] less insightful.

For TAB converters, the work rigorously deriving and analyzing the soft-switching boundaries is virtually nonexistent. A derivation of soft-switching boundaries for a three-port converter without considering the effect of parasitic capacitors and only considering the basic phase-shifts are described in [29]. Moreover, due to not considering the superposition of voltages on the transformer, the listed conditions in [29] are not complete. Derivation of ZVS for a three-port topology made of half-bridges is in [12]. Again, the effect of parasitic capacitances is not considered. The soft-switching conditions under all five independent degrees of freedom and taking into account the effect of parasitic capacitances were not yet derived and analyzed.

The ZVS condition analysis includes two steps: the first step is to express the transformer currents as a function of the port voltages, phase shift angles, switching frequency, and leakage inductance. The second step is to identify all the commutation modes of the converters. In each commutation mode, calculate the minimum current that is sufficient to discharge the switch's output capacitor that is going to turn on. In the available

literature, two approaches for the first step can be found: piecewise expression or harmonic form expression of transformer currents. A piece-wise expression is easy to understand [14]; however, implementing it in a digital controller is somewhat complicated, since the expression changes in each switching pattern. The implementation becomes even more involved with increasing number of switching patterns when the modulation changes from a single-phase shift to a dual-phase shift or further to a triple-phase shift. Thank to [22], harmonic form expression is a kind of unified interpretation of the transformer current no matter which switching pattern it is in or which modulation is used. It, therefore, makes expression more concise and the implementation in the digital controller much more straightforward.

Yet, from the dual active bridge to the triple active bridge, there is a gap. Since one more port is added, there are three more parameters as the transformer's input current expressions, including the port voltage, duty cycle, and phase shift angle. Moreover, adding the third port is not an extension of a dual active bridge in terms of the transformer currents or ZVS conditions. Since the third port is highly coupled with the initial two ports, the transformer current expressions and ZVS conditions of even the initial two ports are entirely changed. Thus, the ZVS condition analysis in triple active bridge converters can hardly be found in the literature. As a result, this paper demonstrates a concise and straightforward approach to analyze the ZVS criteria of TAB: firstly, all the operation scenarios are categorized into four commutation modes; then, in each mode, Thevenin Equivalence is applied to effectively address the minimum discharging current for each port meanwhile taking into account the coupling between the port voltages and leakage inductances; eventually, by the harmonic form expression of the transformer currents, the ZVS conditions can be calculated. Experimental results are obtained under various voltage ratios and phase shift angles to validate the analysis.

The rest of this paper is organized as follows. Section II recapitulates the operating principles and modeling of the TAB converter. In section III, the soft-switching boundaries of the TAB converter are derived, analyzed, and discussed. Section IV provides experimental validation of the ZVS boundaries derived in Sections III. Section V summarises the paper and provides an outlook on the application of the presented work.

## II. OPERATION & MODELLING

# A. Operating Principles

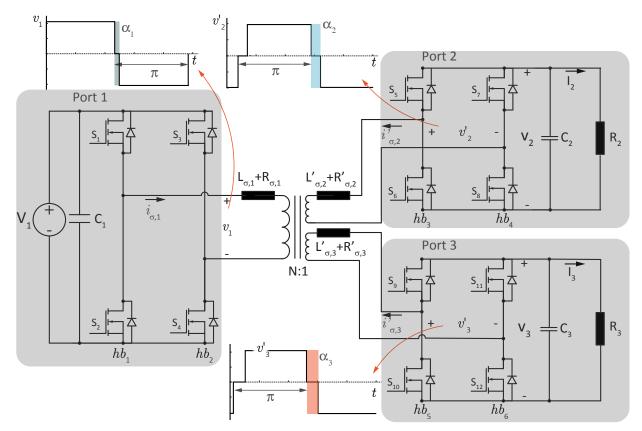

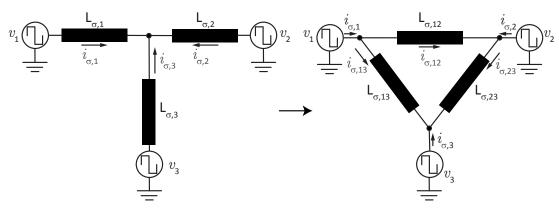

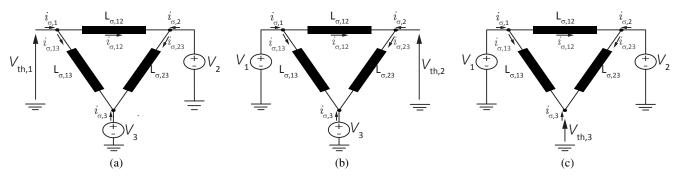

Fig. 1 shows the schematic of the TAB converter. Conceptually, the converter can be viewed as a network of inductors driven by voltage sources with controlled phase-shifts. The inductors can be inserted as separate components, or the transformer leakage inductances can be used. The simplified schematic of the converter is shown in Fig. 2. Figure 2 also shows the transformation of the transformer and the inductor network from a Y-model into  $\Delta$ -model.

Throughout this paper,  $\Delta$ -model is used to analyse the operation of TAB. As was done in [7], the link inductances

in  $\Delta$ -model can be computed from the individual leakage inductances of the transformer windings in Y-model as

$$L_{\sigma,12} = L_{\sigma,1} + L_{\sigma,2} + \frac{L_{\sigma,1}L_{\sigma,2}}{L_{\sigma,3}},$$

(1)

$$L_{\sigma,13} = L_{\sigma,1} + L_{\sigma,3} + \frac{L_{\sigma,1}L_{\sigma,3}}{L_{\sigma,2}},$$

(2)

$$L_{\sigma,23} = L_{\sigma,3} + L_{\sigma,2} + \frac{L_{\sigma,3}L_{\sigma,2}}{L_{\sigma,1}},$$

(3)

where  $L_{\sigma,2}=N^2L'_{\sigma,2}$ ,  $L_{\sigma,3}=N^2L'_{\sigma,3}$  and N is the transformer ratio. Similarly, the transformer currents of the TAB converter after transformation are

$$i_{\sigma,1} = i_{\sigma,12} + i_{\sigma,13},$$

(4)

$$i_{\sigma,2} = -i_{\sigma,12} + i_{\sigma,23},$$

(5)

$$i_{\sigma,3} = -i_{\sigma,13} - i_{\sigma,23},$$

(6)

where  $i_{\sigma,1}$  is the primary side transformer current and  $i_{\sigma,2}=\frac{i'_{\sigma,2}}{N},\ i_{\sigma,3}=\frac{i'_{\sigma,3}}{N}$  are the secondary side transformer currents. The transformer ratio is accounted in voltages as  $v_2=Nv'_2$  and  $v_3=Nv'_3$ .

The power flow in TAB converter can be controlled by six variables including: (a) two phase-shift angles between two port ac voltages ( $\varphi_{xy}$ ),(b) three duty-cycles of each port  $\alpha_x$ , and (c) switching frequency ( $f_s$ ). The switching frequency variation is not used in this paper as it can lead to operation in extremely high frequency at very light loads. TAB converter operated with phase-shift between the full-bridges or ports  $\varphi_{xy}$  and phase-shift between the half-bridges or phase legs  $\alpha_x$  inside each full-bridge will be analyzed in the paper.

## B. Fourier Series Model

The port ac voltages  $v_1$ ,  $v_2$  and  $v_3$  can be described using Fourier series [22]. The infinite sums describing the port voltages are

$$v_1(t) = \sum_{\substack{1 \le n < \infty \\ n \text{ odd}}} \left[ V_1 d_{1,r} \frac{\sin(nt\omega_s)}{n} \right], \tag{7}$$

$$v_2(t) = \sum_{\substack{1 \le n < \infty \\ n \text{ odd}}} \left[ V_2 d_{2,i} \frac{\cos(nt\omega_s)}{n} + V_2 d_{2,r} \frac{\sin(nt\omega_s)}{n} \right],$$

$$v_3(t) = \sum_{\substack{1 \le n < \infty \\ n \text{ odd}}} \left[ V_3 d_{3,i} \frac{\cos(nt\omega_s)}{n} + V_3 d_{3,r} \frac{\sin(nt\omega_s)}{n} \right],$$

(9)

where  $\omega_s = 2\pi f_s$  and

$$d_{1,r} = \frac{4}{\pi} \cos\left(\frac{n\alpha_1}{2}\right),\tag{10}$$

$$d_{2,r} = \frac{4}{\pi} \cos\left(\frac{n\alpha_2}{2}\right) \cos\left(n\varphi_{12}\right),\tag{11}$$

$$d_{2,i} = \frac{4}{\pi} \cos\left(\frac{n\alpha_2}{2}\right) \sin\left(n\varphi_{12}\right),\tag{12}$$

Fig. 1: Triple Active Bridge (TAB) converter schematic

Fig. 2: Delta transformation.

$$d_{3,r} = \frac{4}{\pi} \cos\left(\frac{n\alpha_3}{2}\right) \cos\left(n\varphi_{13}\right),\tag{13}$$

$$d_{3,i} = \frac{4}{\pi} \cos\left(\frac{n\alpha_3}{2}\right) \sin\left(n\varphi_{13}\right). \tag{14}$$

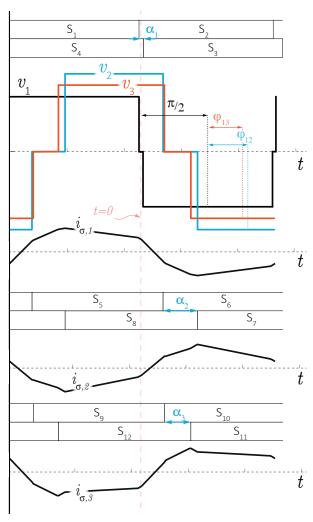

The definition of  $\varphi_{12}$ ,  $\varphi_{13}$  and  $\alpha_1$ ,  $\alpha_2$ ,  $\alpha_3$  is graphically demonstrated in Fig. 3.

The inductor currents in the circuit described in delta convention can be calculated as

$$i_{\sigma,xy}(t) - i_{\sigma,xy}(0) = \frac{1}{L_{\sigma,xy}} \int_0^t \left[ v_x(\tau) - v_y(\tau) \right] d\tau, \quad (15)$$

considering the switching symmetry across the switching cycle it is clear that current at t=0 is the same as the current at  $t=\frac{\pi}{2\omega_s}$ , i.e.  $i_{\sigma,xy}(\frac{\pi}{2\omega_s})=i_{\sigma,xy}(0)$ . The transformer current

in delta circuit can be written as

$$i_{\sigma,12}(t) = \frac{-V_2}{L_{\sigma,12}\omega_s} \sum_{\substack{1 \le n < \infty \\ n \text{ odd}}} \left[ m_{12}d_{1,r} \frac{\cos(nt\omega_s)}{n^2} - d_{2,r} \frac{\cos(nt\omega_s)}{n^2} + d_{2,i} \frac{\sin(nt\omega_s)}{n^2} \right],$$

$$(16)$$

#### Current Closed-form solution

$$\begin{split} i_{\sigma,1}(\tau_{j}) &\quad -\frac{\pi V_{2}}{2\omega_{s}L_{\sigma,12}} \left[ 1 + m_{12} \left( \frac{\left| \frac{\alpha_{1}}{2} + \tau_{j} \right| + \left| \frac{-\alpha_{1}}{2} + \tau_{j} \right|}{\pi} - 1 \right) - \frac{\left( \left| \frac{\alpha_{2}}{2} + \tau_{j} - \varphi_{12} \right| + \left| \frac{-\alpha_{2}}{2} + \tau_{j} - \varphi_{12} \right| \right)}{\pi} \right] + \\ &\quad -\frac{\pi V_{3}}{2\omega_{s}L_{\sigma,13}} \left[ 1 + m_{13} \left( \frac{\left| \frac{\alpha_{1}}{2} + \tau_{j} \right| + \left| \frac{-\alpha_{1}}{2} + \tau_{j} \right|}{\pi} - 1 \right) - \frac{\left( \left| \frac{\alpha_{3}}{2} + \tau_{j} - \varphi_{13} \right| + \left| \frac{-\alpha_{3}}{2} + \tau_{j} - \varphi_{13} \right| \right)}{\pi} \right] \\ i_{\sigma,2}(\tau_{j}) &\quad \frac{\pi V_{2}}{2\omega_{s}} \left[ \frac{1}{L_{\sigma,12}} \left[ 1 + m_{12} \left( \frac{\left| \frac{\alpha_{1}}{2} + \tau_{j} \right| + \left| \frac{-\alpha_{1}}{2} + \tau_{j} \right|}{\pi} - 1 \right) - \frac{\left( \left| \frac{\alpha_{2}}{2} + \tau_{j} - \varphi_{12} \right| + \left| \frac{-\alpha_{2}}{2} + \tau_{j} - \varphi_{12} \right| \right)}{\pi} \right] + \\ &\quad \frac{-1}{L_{\sigma,23}} \left[ \frac{1}{m_{23}} \left( 1 - \frac{\left| \frac{\alpha_{3}}{2} + \tau_{j} - \varphi_{13} \right| + \left| \frac{\alpha_{3}}{2} - \tau_{j} + \varphi_{13} \right|}{\pi} \right) + \frac{\left| \frac{\alpha_{2}}{2} + \tau_{j} - \varphi_{12} \right| + \left| \frac{\alpha_{3}}{2} - \tau_{j} + \varphi_{12} \right|}{\pi} - 1 \right] \right] \\ i_{\sigma,3}(\tau_{j}) &\quad \frac{\pi V_{3}}{2\omega_{s}} \left[ \frac{1}{L_{\sigma,13}} \left[ 1 + m_{13} \left( \frac{\left| \frac{\alpha_{1}}{2} + \tau_{j} \right| + \left| \frac{-\alpha_{1}}{2} + \tau_{j} \right|}{\pi} - 1 \right) - \frac{\left( \left| \frac{\alpha_{3}}{2} + \tau_{j} - \varphi_{13} \right| + \left| \frac{\alpha_{3}}{2} - \tau_{j} + \varphi_{13} \right|}{\pi} \right) - 1 \right] \right] \\ &\quad \frac{1}{L_{\sigma,23}} \left[ m_{23} \left( \frac{\left| \frac{\alpha_{2}}{2} + \tau_{j} - \varphi_{12} \right| + \left| \frac{\alpha_{2}}{2} - \tau_{j} + \varphi_{12} \right|}{\pi} - 1 \right) - \frac{\left( \left| \frac{\alpha_{3}}{2} + \tau_{j} - \varphi_{13} \right| + \left| \frac{\alpha_{3}}{2} - \tau_{j} + \varphi_{13} \right|}{\pi} \right) - 1 \right] \right] \end{aligned}$$

Fig. 3: Phase leg switched voltages and port currents during commutation.

$$i_{\sigma,13}(t) = \frac{-V_3}{L_{\sigma,13}\omega_s} \sum_{\substack{1 \le n < \infty \\ n \text{ odd}}} \left[ m_{13}d_{1,r} \frac{\cos(nt\omega_s)}{n^2} -d_{3,r} \frac{\cos(nt\omega_s)}{n^2} + d_{3,i} \frac{\sin(nt\omega_s)}{n^2} \right],$$

$$(17)$$

$$i_{\sigma,23}(t) = \frac{-V_3}{L_{\sigma,23}\omega_s} \sum_{\substack{1 \le n < \infty \\ n \text{ odd}}} \left[ m_{23} \left( d_{2,r} \frac{\cos(nt\omega_s)}{n^2} - d_{2,i} \frac{\sin(nt\omega_s)}{n^2} \right) - d_{3,r} \frac{\cos(nt\omega_s)}{n^2} + d_{3,i} \frac{\sin(nt\omega_s)}{n^2} \right],$$

$$(18)$$

where  $m_{12} = \frac{V_1}{V_2}$ ,  $m_{13} = \frac{V_1}{V_3}$  and  $m_{23} = \frac{V_2}{V_3}$ .

## C. Closed Form Solution

By substituting the harmonic form expression of the delta circuit currents in (16)-(18) and duty cycle in (10)-(14), into the port currents in (4)-(6), the closed-form solution of the port current  $i_{\sigma,1}(\tau_j)$ ,  $i_{\sigma,2}(\tau_j)$  and  $i_{\sigma,3}(\tau_j)$  at the events of switching transitions  $\tau_j$  can be obtained, and they are summarized in Table I. The times of switching event  $\tau_j$  are defined in Table IV. Note that in the derivation procedure of the closed form solution of the port currents from harmonic form expression, following properties of infinite series of odd components are used [22],

$$\sum_{\substack{1 \le n < \infty \\ n \text{ odd}}} \frac{1}{n^2} = \frac{\pi^2}{8},\tag{19}$$

$$\sum_{\substack{1 \le n < \infty \\ n \text{ odd}}} \frac{\cos(n\beta)}{n^2} = \frac{\pi(\pi - |2\beta|)}{8},$$

(20)

where  $\beta$  is any angle in radians.

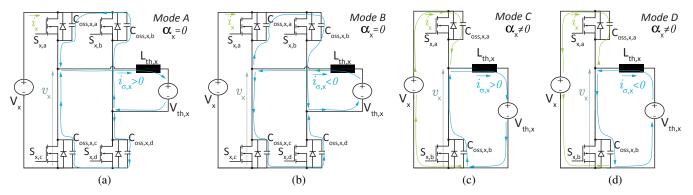

Fig. 4: Port schematics during four possible commutation modes.

TABLE II: ZVS Conditions of TAB Converter

| Mode | Switches turned-on | Conditions                                                                                                                                                                                                                                       |

|------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A    | $S_c$ and $S_b$    | $\text{if } V_{\text{th},x} > 0 \text{ the ZVS condition is }  i_{\sigma,x}\left(\tau_{j}\right)  \geq 2V_{x}\sqrt{\frac{C_{\text{oss},x}}{L_{\text{th},x}}}\frac{V_{\text{th},x}}{V_{x}}$                                                       |

|      |                    | if $V_{\text{th},x} < 0$ , the ZVS is assured                                                                                                                                                                                                    |

| В    | $S_a$ and $S_d$    | $\text{if } V_{\text{th},x} < 0 \text{ the ZVS condition is }  i_{\sigma,x}\left(\tau_{j}\right)  \geq 2V_{x}\sqrt{-\frac{C_{\text{oss},x}}{L_{\text{th},x}}\frac{V_{\text{th},x}}{V_{x}}}$                                                      |

|      |                    | if $V_{\text{th},x} > 0$ , the ZVS is assured                                                                                                                                                                                                    |

| С    | $S_b$              | $\text{if } V_{\text{th},x} > \frac{V_x}{2}, \text{ the ZVS condition is }  i_{\sigma,x}\left(\tau_j\right)  \geq 2V_x \sqrt{\frac{C_{\text{oss},x}}{L_{\text{th},x}}} \frac{V_{\text{th},x}}{V_x} - \frac{C_{\text{oss},x}}{2L_{\text{th},x}}$  |

|      |                    | if $V_{	ext{th},x} < \frac{V_x}{2}$ , the ZVS is assured                                                                                                                                                                                         |

| D    | $S_a$              | $\text{if } V_{\text{th},x} < \frac{V_x}{2}, \text{ the ZVS condition is }  i_{\sigma,x}\left(\tau_j\right)  \geq 2V_x \sqrt{-\frac{C_{\text{oss},x}}{L_{\text{th},x}}} \frac{V_{\text{th},x}}{V_x} + \frac{C_{\text{oss},x}}{2L_{\text{th},x}}$ |

|      |                    | if $V_{\text{th},x} > \frac{V_x}{2}$ , the ZVS is assured                                                                                                                                                                                        |

### III. ZERO VOLTAGE SWITCHING

The full-bridge ac voltages and the corresponding currents are shown in Fig. 3. In an ideal case, the energy stored in the MOSFETs parasitic capacitors is ignored, and the magnetizing inductance of the transformer is considered infinite. In this ideal case, the ZVS operation of the converter switches is only dependent on the direction of the output bridge current during the state transition. ZVS occurs when the output current of a bridge is flowing through the active switch of the corresponding half-bridge as the half-bridges opposing transistor becomes active; in such a case, the current will naturally commute to the opposing switch anti-parallel diode after the active switched is turned off.

MOSFET's parasitic capacitance adds a soft-switching condition, in the form of minimal current in the leakage inductance required to complete the ZVS commutation. To derive

the ZVS conditions for the TAB converter, it is assumed that the converter operates in steady-state, i.e., only one phase leg commutates at each switching event.

TAB can be operated with five phase-shifts. Two phase-shifts between ports  $\varphi_{12}$ ,  $\varphi_{13}$ , and three phase-shifts that are defined between phase legs of each port  $\alpha_1$ ,  $\alpha_2$  and  $\alpha_3$ . The phase-shifts  $\varphi_{12}$ ,  $\varphi_{13}$  as marked in Fig.3 are defined as the difference between the middle points of the switching cycles. These five degrees of freedom can create tens of different operating modes, and examining each with graphical tools is impractical. Therefore to analyze ZVS of a TAB converter, a comprehensive investigation of ZVS conditions for generic full-bridge operated with phase-shifts  $\varphi_x$  and  $\alpha_x$  is presented. In the generic full-bridge, four separate switching modes are identified. These four modes encompass all unique commutations, i.e., the remaining commutations are always

symmetrical counter-parts of described commutations. The four commutation modes can be divided into two groups based on the phase leg phase shift  $\alpha_x$ , and further subdivided by the direction of the port current  $i_{\sigma,x}$ . In second step, values of inductor  $L_{\text{th},x}$  and amplitude of voltage source  $v_{\text{th},x}$  in the generic full bridge are derived. The need for the second step stems from the fact that the inductor and the voltage source in the TAB converter are not simple constants (unlike in DAB), but are superpositions of each ports state at the given time instant. Therefore, Thevenin equivalents of these voltages are derived in the second step. The third step consists of synthesizing the conditions from the first step, Thevenin equivalents impedances and voltage sources, and the respective sequences of switching instances  $\tau_j$ . These three steps establish conditions for ZVS in the TAB converter.

# A. Mode A: $\alpha_x = 0$ , $i_{\sigma,x}(\tau_i) > 0$

In mode A all four switches are commutating,  $S_{x,a}$  and  $S_{x,d}$  have been turned off, while  $S_{x,b}$  and  $S_{x,c}$  are going to be turned on. From Fig. 4a following current equations can be written

$$i_{\sigma,x}\left(\tau_{j}\right) = -2C_{\text{oss},x}\frac{\mathrm{d}v_{x}}{\mathrm{d}t},\tag{21}$$

$$i_x\left(\tau_i\right) = 0. \tag{22}$$

The minimum current requirement for ZVS is obtained from the energy absorbed by  $V_{th,x}$ , which can be calculated as follows

$$E_{\text{absorbed}} = \int_{T_{--}} V_{\text{th},x} i_{\sigma,x}(\tau_j) dt.$$

(23)

Combining (21), (22) and assuming the voltage  $v_x$  is changing from  $V_x$  to 0 in (23), following is obtained

$$E_{\text{absorbed}} = 2C_{\text{oss},x}V_{\text{th},x}V_{x}.$$

(24)

The sum of energy stored in the parasitic capacitors does not change during commutation. To find the minimum current amplitude requirement, an energy inequality can be written as

$$\frac{1}{2}L_{\mathsf{th},x}i_{\sigma,x}^2(\tau_j) \ge 2C_{\mathsf{oss},x}V_{\mathsf{th},x}V_x. \tag{25}$$

The polarity of the voltage  $V_{\mathrm{th},x}$  is assumed to be positive in (25). If the voltage  $V_{\mathrm{th},x}$  is negative, then ZVS is always achieved. The minimal current condition for Mode A, when  $V_{\mathrm{th},x}>0$  can be written as

$$|i_{\sigma,x}(\tau_j)| \ge 2V_x \sqrt{\frac{C_{\text{oss},x}}{L_{\text{th},x}}} \frac{V_{\text{th},x}}{V_x}.$$

(26)

# B. Mode B: $\alpha_x = 0$ , $i_{\sigma,x}(\tau_i) < 0$

As shown in Fig. 4b, in mode B, all four switches are commutating, where  $S_{x,b}$  and  $S_{x,c}$  have been turned off while  $S_{x,a}$  and  $S_{x,d}$  are going to be turned on. The inductor current is flowing into the full bridge, which is in reverse compared

to mode A. The current equations from Fig. 4b can be written

$$i_{\sigma,x}(\tau_j) = -2C_{\text{oss},x}\frac{\mathrm{d}v_x}{\mathrm{d}t},$$

(27)

$$i_x(\tau_j) = 0. (28)$$

Similarly as in mode A, following energy inequality can be derived

$$\frac{1}{2}L_{\mathsf{th},x}i_{\sigma,x}^2(\tau_j) \ge -2C_{\mathsf{oss},x}V_{\mathsf{th},x}V_x. \tag{29}$$

In (29) it is assumed that  $V_{\text{th},x}$  is negative, otherwise ZVS is assured. The minimal current requirement for mode B can be written as

$$|i_{\sigma,x}(\tau_j)| \ge 2V_x \sqrt{-\frac{C_{\text{oss},x}}{L_{\text{th},x}}} \frac{V_{\text{th},x}}{V_x}.$$

(30)

The inequality (30) is derived for switches  $S_{x,a}$  and  $S_{x,d}$  turning on.

# C. Mode C: $\alpha_x \neq 0$ , $i_{\sigma,x}(\tau_j) > 0$

Mode C commutation is shown in Fig. 4c. Mode C occurs when the phase-shift  $\alpha_x$  is non-zero. The soft-switching conditions for leading and lagging phase-leg become different. According to Fig. 4c the currents are

$$i_{\sigma,x}(\tau_j) = -2C_{\text{oss},x}\frac{\mathrm{d}v_x}{\mathrm{d}t},\tag{31}$$

$$i_x(\tau_j) = -C_{\text{oss},x} \frac{\mathrm{d}v_x}{\mathrm{d}t}.$$

(32)

As was done for modes A and B, calculating the absorbed energy by source  $v_{th,x}$  leads to calculation of the minimum current amplitude requirement. Energy absorbed by the sources can be calculated as

$$E_{\text{absorbed}} = \int_{T_{\text{com}}} V_{\text{th},x} i_{\sigma,x}(\tau_j) dt - \int_{T_{\text{com}}} V_x i_x(\tau_j) dt.$$

(33)

Combining to (31), (32) and assuming the voltage  $v_x$  to change from  $V_x$  to 0 in (33) following is obtained

$$E_{\text{absorbed}} = 2C_{\text{oss},x}V_{\text{th},x}V_x - C_{\text{oss},x}V_x^2. \tag{34}$$

Similarly as for modes A and B, minimum current requirement can be obtained from

$$\frac{1}{2}L_{\rm th}i_{\sigma,x}^{2}(\tau_{j}) \ge 2C_{{\rm oss},x}V_{{\rm th},x}V_{x} - C_{{\rm oss},x}V_{x}^{2}, \tag{35}$$

From (35) a ZVS condition can be obtained

$$|i_{\sigma,x}(\tau_j)| \ge 2V_x \sqrt{\frac{C_{\text{oss},x}}{L_{\text{th},x}}} \frac{V_{\text{th},x}}{V_x} - \frac{C_{\text{oss},x}}{2L_{\text{th},x}},$$

(36)

where  $V_{\text{th},x} > \frac{V_x}{2}$  otherwise ZVS is assured for switch  $S_b$ .

# D. Mode D- $\alpha_x \neq 0$ , $i_{\sigma,x}(\tau_i) < 0$

The counter part of mode C is mode D which occurs when the inductor current has opposite polarity. Circuit describing mode D is shown in Fig. 4d. The current equations can be written as

$$i_{\sigma,x}(\tau_j) = -2C_{\text{oss},x}\frac{\mathrm{d}v_x}{\mathrm{d}t},\tag{37}$$

| Port no. | $L_{th,x}$                                                         | Half-bridge | $V_{th,x}$                                                                                                                           | $i_{\sigma,x}$  |

|----------|--------------------------------------------------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 1        | $\frac{L_{\sigma,13}L_{\sigma,12}}{L_{\sigma,13} + L_{\sigma,12}}$ |             | $V_2(\tau_1) \frac{L_{\sigma,13}}{L_{\sigma,13} + L_{\sigma,12}} + V_3(\tau_1) \frac{L_{\sigma,12}}{L_{\sigma,13} + L_{\sigma,12}}$  | $i_{\sigma,1}$  |

|          |                                                                    | Lagging     | $-V_2(\tau_2)\frac{L_{\sigma,13}}{L_{\sigma,13} + L_{\sigma,12}} - V_3(\tau_2)\frac{L_{\sigma,12}}{L_{\sigma,13} + L_{\sigma,12}}$   | $-i_{\sigma,1}$ |

| 2        | $\frac{L_{\sigma,23}L_{\sigma,12}}{L_{\sigma,23} + L_{\sigma,12}}$ |             | $V_1(\tau_3) \frac{L_{\sigma,23}}{L_{\sigma,23} + L_{\sigma,12}} + V_3(\tau_3) \frac{L_{\sigma,12}}{L_{\sigma,23} + L_{\sigma,12}}$  | $i_{\sigma,2}$  |

|          |                                                                    | Lagging     | $-V_1(\tau_4) \frac{L_{\sigma,23}}{L_{\sigma,23} + L_{\sigma,12}} - V_3(\tau_4) \frac{L_{\sigma,12}}{L_{\sigma,23} + L_{\sigma,12}}$ | $-i_{\sigma,2}$ |

| 3        | $\frac{L_{\sigma,13}L_{\sigma,23}}{L_{\sigma,13}+L_{\sigma,23}}$   | Leading     | $V_1(\tau_5) \frac{L_{\sigma,23}}{L_{\sigma,23} + L_{\sigma,13}} + V_2(\tau_5) \frac{L_{\sigma,13}}{L_{\sigma,23} + L_{\sigma,13}}$  | $i_{\sigma,3}$  |

|          |                                                                    | Lagging     | $-V_1(\tau_6) \frac{L_{\sigma,23}}{L_{\sigma,23} + L_{\sigma,13}} - V_2(\tau_6) \frac{L_{\sigma,13}}{L_{\sigma,23} + L_{\sigma,13}}$ | $-i_{\sigma,3}$ |

Fig. 5: Equivalent Thevenin circuits.

$$i_x(\tau_j) = -C_{\text{oss},x} \frac{\mathrm{d}v_x}{\mathrm{d}t}.$$

(38)

Similarly as for mode C, energy absorbed and supplied can be derived. The notable difference is the change of voltage  $v_x$  from 0 to  $V_x$ . Using the inductor and capacitances energies, minimum current amplitude requirement can be written as

$$\frac{1}{2}L_{\text{th},x}i_{\sigma,x}^{2}(\tau_{j}) \ge -2C_{\text{oss},x}V_{\text{th},x}V_{x} + C_{\text{oss},x}V_{x}^{2}.$$

(39)

From (39) the minimum amplitude current requirement can be obtained as

$$|i_{\sigma,x}(\tau_j)| \ge 2V_x \sqrt{-\frac{C_{\text{oss},x}}{L_{th,x}} \frac{V_{\text{th},x}}{V_x} + \frac{C_{\text{oss},x}}{2L_{\text{th},x}}}.$$

(40)

Condition (40) is derived for turn on of switch  $S_a$  when voltage  $V_{\text{th},x}$  is smaller than  $\frac{V_x}{2}$ , otherwise ZVS is assured for  $S_a$ .

The ZVS conditions for all modes are summarized in Table II. The parameters like  $V_{\text{th},x}$ ,  $L_{\text{th},x}$  and  $i_{\sigma,x}$  for the conditions are then derived as follows in Table III.

# E. Thevenin Equivalent Circuits

The delta circuit from Fig. 2 is simplified into three Thevenin equivalent circuits as shown in Fig. 5. During commutation, the port voltage either remains the same or has already changed to new value, and thereby they are considered as constant voltage and expressed with uppercase letters. The values of  $V_x$  during each commucation are defined in Table IV. For illustration, the Thevenin equivalent impedance during commutation of port one can be derived from circuit in Fig. 5a. The equivalent impedance is calculated by short-circuiting  $V_2$  and  $V_3$  and equals

$$L_{\text{th},1} = \frac{L_{\sigma,12}L_{\sigma,13}}{L_{\sigma,12} + L_{\sigma,13}}.$$

(41)

The Thevenin equivalent voltage for the same circuit is a superposition of the two voltage dividers at time instant  $\tau_1$  and can be written as

$$V_{\text{th},1}(\tau_1) = V_2(\tau_1) \frac{L_{\sigma,13}}{L_{\sigma,12} + L_{\sigma,13}} + V_3(\tau_1) \frac{L_{\sigma,12}}{L_{\sigma,12} + L_{\sigma,13}}.$$

(42)

Thevenin equivalent impedances and voltages can be derived for other ports in similar manner, and are summarized in Table III.

| Port no. | Half-bridge | Voltages for Thevenin Circuit                              |                                                                                     |                                                            | $	au_j$                                                                             |                                              |

|----------|-------------|------------------------------------------------------------|-------------------------------------------------------------------------------------|------------------------------------------------------------|-------------------------------------------------------------------------------------|----------------------------------------------|

| 1        | Leading     | $V_2(\tau_1) = \begin{cases} V_2 \\ 0 \\ -V_2 \end{cases}$ | if $\tau_1 < \tau_3$ ,<br>if $\tau_3 < \tau_1 < \tau_4$ ,<br>if $\tau_4 < \tau_1$ , | $V_3(\tau_1) = \begin{cases} V_3 \\ 0 \\ -V_3 \end{cases}$ | if $\tau_1 < \tau_5$ ,<br>if $\tau_5 < \tau_1 < \tau_6$ ,<br>if $\tau_6 < \tau_1$ , | $	au_1 = -rac{lpha_1}{2}$                   |

|          | Lagging     | $V_2(\tau_2) = \begin{cases} V_2 \\ 0 \\ -V_2 \end{cases}$ | if $\tau_2 < \tau_3$ ,<br>if $\tau_3 < \tau_2 < \tau_4$ ,<br>if $\tau_4 < \tau_2$ , | $V_3(\tau_2) = \begin{cases} V_3 \\ 0 \\ -V_3 \end{cases}$ | if $\tau_2 < \tau_5$ ,<br>if $\tau_5 < \tau_2 < \tau_6$ ,<br>if $\tau_6 < \tau_2$ , | $	au_2 = rac{lpha_1}{2}$                    |

| 2        | Leading     | $V_1(\tau_3) = \begin{cases} V_1 \\ 0 \\ -V_1 \end{cases}$ | if $\tau_3 < \tau_1$ ,<br>if $\tau_1 < \tau_3 < \tau_2$ ,<br>if $\tau_2 < \tau_3$ , | $V_3(\tau_3) = \begin{cases} V_3 \\ 0 \\ -V_3 \end{cases}$ | if $\tau_3 < \tau_5$ ,<br>if $\tau_5 < \tau_3 < \tau_6$ ,<br>if $\tau_6 < \tau_3$ , | $\tau_3 = \varphi_{12} - \frac{\alpha_2}{2}$ |

|          | Lagging     | $V_1(\tau_4) = \begin{cases} V_1 \\ 0 \\ -V_1 \end{cases}$ | if $\tau_4 < \tau_1$ ,<br>if $\tau_1 < \tau_4 < \tau_2$ ,<br>if $\tau_2 < \tau_4$ , | $V_3(\tau_4) = \begin{cases} V_3 \\ 0 \\ -V_3 \end{cases}$ | if $\tau_4 < \tau_5$ ,<br>if $\tau_5 < \tau_4 < \tau_6$ ,<br>if $\tau_6 < \tau_4$ , | $\tau_4 = \varphi_{12} + \frac{\alpha_2}{2}$ |

| 3        | Leading     | $V_1(\tau_5) = \begin{cases} V_1 \\ 0 \\ -V_1 \end{cases}$ | if $\tau_5 < \tau_1$ ,<br>if $\tau_1 < \tau_5 < \tau_2$ ,<br>if $\tau_2 < \tau_5$ , | $V_2(\tau_5) = \begin{cases} V_2 \\ 0 \\ -V_2 \end{cases}$ | if $\tau_5 < \tau_3$ ,<br>if $\tau_3 < \tau_5 < \tau_4$ ,<br>if $\tau_4 < \tau_5$ , | $\tau_5 = \varphi_{13} - \frac{\alpha_3}{2}$ |

|          | Lagging     | $V_1(\tau_6) = \begin{cases} V_1 \\ 0 \\ -V_1 \end{cases}$ | if $\tau_6 < \tau_1$ ,<br>if $\tau_1 < \tau_6 < \tau_2$ ,<br>if $\tau_2 < \tau_6$ , | $V_2(\tau_6) = \begin{cases} V_2 \\ 0 \\ -V_2 \end{cases}$ | if $\tau_6 < \tau_3$ ,<br>if $\tau_3 < \tau_6 < \tau_4$ ,<br>if $\tau_4 < \tau_6$ , | $\tau_6 = \varphi_{13} + \frac{\alpha_3}{2}$ |

## F. Complete ZVS Expressions

Complete ZVS conditions of TAB depend on the sequence of the switching, as the Thevenin voltage can change in the condition depending on the sequence. This dependence can be illustrated using Fig. 3. It is clear that when calculating the Thevenin equivalent voltage for S2 of port one,  $v_3$  is positive. However, when calculating the Thevenin equivalent voltage, for example, for S7 of port two,  $v_3$  becomes negative. A similar situation can happen to any port, depending on the sequence. Therefore the voltages in the Thevenin equivalent are functions of the sequence of the switching events. Table IV gives a complete overview of the sequences.

1) Non-Linear Parasitic Capacitance  $C_{oss,x}$ : The  $C_{oss}$  is not constant, and it varies with drain-source voltage Vds of the switch in a nonlinear way. As a nonlinear function of  $V_{ds}$ , the  $C_{oss}$  is usually provided in the datasheet of the power switches. Based on it, the equivalent output capacitance of the switch can be calculated. The derivation of (24) is shown here to demonstrate how the nonlinearity is considered. (24) is obtained by substituting (21) and (22) into (23), which then becomes

$$E_{\text{absorbed}} = 2V_{th,x} \int_0^{V_x} C_{oss,x}(v_x) dv_x = 2V_{th,x} \bar{C}_{oss,x}(V_x) V_x$$

(43)

where  $V_x$  is the dc link voltage of the port where the transistor operates,  $v_x$  is the instant voltage of the  $C_{oss}$ ,  $V_{th,x}$  is contant in the discharging procedure.  $C_{oss,x}(v_x)$  is provided

in the datasheet. The only thing is that the datasheet usually doesn not provide an analytical  $C_{oss,x}(v_x)$  but data points of  $C_{oss,x}(v_x)$ . Thus, curve fitting is needed to get an analytical  $C_{oss,x}(v_x)$ , which can be submitted to the above equation to obtain  $E_{absorbed}$ . In the end,  $\bar{C}_{oss,x}(V_x)$  as a function of  $V_x$  can be calculated as,

$$\bar{C}_{oss,x}(V_x) = \frac{1}{V_x} \int_0^{V_x} C_{oss,x}(v_x) dv_x \tag{44}$$

As seen, if  $V_x$  does not change or have only a slight change,  $\bar{C}_{oss,x}(V_x)$  can be considered as constant. In case  $V_x$  varies a lot,  $\bar{C}_{oss,x}(V_x)$  at different  $V_x$  can be calculated beforehand, and a look-up table based on it can be used for online ZVS analysis.

2) Dead-Time: The dead time can influence the ZVS from two aspects: 1. the rising edge or falling edge of the port ac voltage may get delayed due to deadtime. Which edge will be delayed depends on the polarity of the port current at the moment of related leg commutation. This effect will be significant when deadtime is comparable with the switching cycle; 2. ZVS is a procedure of LC resonance. Assuming the converter operates on the boundary of ZVS before the switch turns on, its drain-source voltage will first drop to zero and increase again. So the deadtime must match the resonance time to turn on the switch at the exact time when its drain-source voltage drops to zero. Earlier or later, ZVS can not be achieved. However, this is only valid when the converter is on the boundary of ZVS. If the port current is much larger than

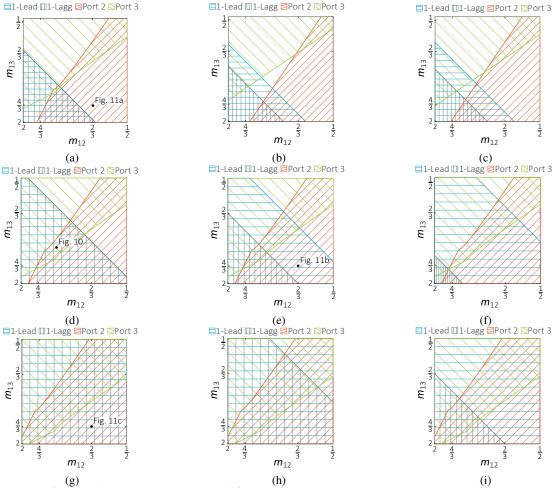

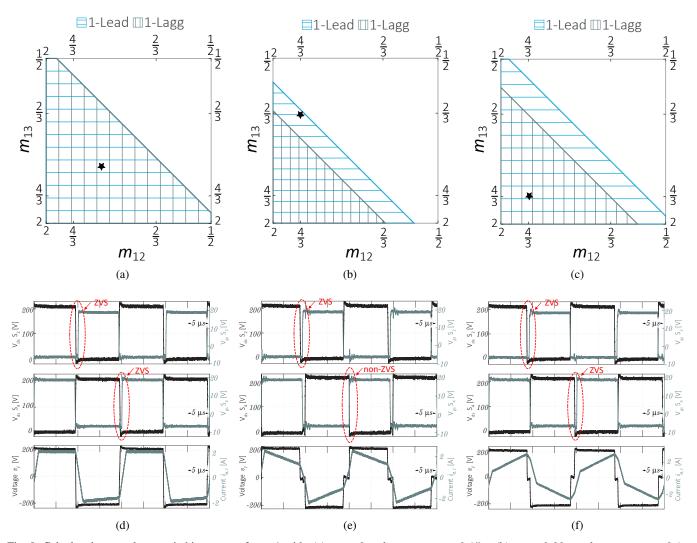

Fig. 6: Zero voltage switching when port one uses phase-shift  $\alpha_1$  while  $\alpha_2=\alpha_3=0$ . In (a)-(c) the phase-shifts are  $\varphi_{12}=\varphi_{13}=0.05\pi$ , in (d)-(f)  $\varphi_{12}=\varphi_{13}=0.15\pi$  and in (g)-(i)  $\varphi_{12}=\varphi_{13}=0.3\pi$ . In (a),(d) and (g) phase-shift  $\alpha_1=0$ , in (b),(e) and (h) phase-shift  $\alpha_1=0.15\pi$  and in (c), (f) and (i) phase-shift  $\alpha_1=0.45\pi$ .

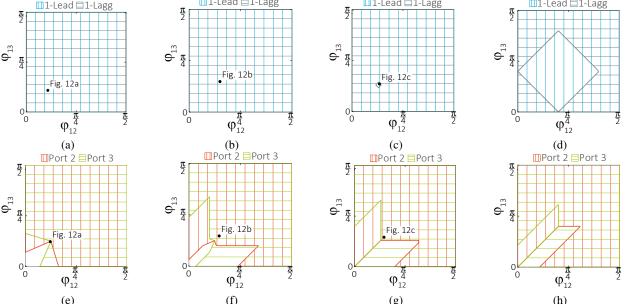

(e) (f) (g) (h) Fig. 7: Calculated zero voltage switching areas when  $m_{12}=m_{13}=\frac{4}{3}.$  In (a) and (e)  $\alpha_1=0.$  In (b) and (f)  $\alpha_1=0.2\pi.$  In (c) and (g)  $\alpha_1=0.25\pi$  and in (d) and (h)  $\alpha_1=0.4\pi$

Fig. 8: Calculated zero voltage switching areas when  $m_{12}=m_{13}=\frac{2}{3}$ . In (a), (d) and (g)  $\alpha_2=\alpha_3=0$ . In (b), (e) and (h)  $\alpha_2=\alpha_3=0.15\pi$ . In (c), (f) and (i)  $\alpha_2=\alpha_3=0.4\pi$ .

the minimum current for ZVS, as long as deadtime is longer than the switch's discharging time, ZVS can be achieved.

## G. Soft-switching Analysis

The surfaces were calculated using parameters summarised in Table V. Figure 6 shows the ZVS areas of all three ports as a function of voltage ratios  $m_{12}$  and  $m_{13}$  when phase-shifts  $\varphi_{12}$ ,  $\varphi_{13}$  and  $\alpha_1$  are used while  $\alpha_2 = \alpha_3 = 0$ . In figures, 1-Lead and 1-Lagg are defined as the leading leg (composed of  $S_1$  and  $S_2$ ) and lagging leg (composed of  $S_3$  and  $S_4$ ) of port one; 2-Lead and 2-Lagg are defined as the leading leg (composed of  $S_5$  and  $S_6$ ) and lagging leg (composed of  $S_7$  and  $S_8$ ) of port two; 3-Lead and 3-Lagg are defined as the leading leg (composed of  $S_9$  and  $S_{10}$ ) and lagging leg (composed of  $S_{11}$  and  $S_{12}$ ) of port three. In Fig. 6 phase-shifts  $\varphi_{12}$ ,  $\varphi_{13}$ are equal and are varied in the vertical direction, going from  $0.05\pi$  in the first row to  $0.3\pi$  in the third row. Phase-shift  $\alpha_1$ is varied in the horizontal direction, i.e., in the first column  $\alpha_1 = 0$ , while in the third, it is  $0.3\pi$ . A general observation is that ZVS is achieved at ports with higher voltage, while the ports that have smaller voltage do not achieve ZVS. Moreover, as is the case in the dual active bridge, increasing the phaseshifts  $\varphi_{12}$ ,  $\varphi_{13}$  leads to ZVS across the large range of voltage ratios. However, large phase-shifts also mean larger losses due to increased circulating power. Secondly, it is clear that for port one, which is assumed to always lead in Fig. 6, it is, in general, easier to achieve ZVS for the leading phase-leg.

The ZVS areas of all three ports as a function of phaseshifts  $\varphi_{12}$  and  $\varphi_{13}$  when voltage ratios  $m_{12}$  and  $m_{13}$  are both equal to  $\frac{4}{3}$  is shown in Fig. 7. Figure 7 also shows the effect of changing phase-shift  $\alpha_1$ . As is clear from the figure, achieving ZVS on port one with the highest voltage is possible across the whole operating region. However, for port two and three, the soft-switching areas are limited. Especially at very light loads achieving ZVS on all phase-legs is difficult. Increasing phaseshift  $\alpha_1$  reduces the ZVS area of the lagging half-bridge in port one. It is interesting to observe the difference between Fig. 7b and Fig. 7c, when even a relatively small difference in phaseshift  $\alpha_1$  leads to loss of soft-switching on the lagging phaseleg of port one. When phase-shift  $\alpha_1$  is increased even further, then soft-switching can be achieved even for very small phaseshifts on port two and three. However, it leads to loss of softswitching for lagging phase-leg on port one.

The ZVS areas of all three ports as a function of phase-shifts  $\varphi_{12}$  and  $\varphi_{13}$  when voltage ratios  $m_1$  and  $m_2$  are both equal to  $\frac{2}{3}$  is shown in Fig. 8. Figure 8 shows the ZVS area

Fig. 9: Calculated zero voltage switching areas of port 1 with: (a)  $\alpha_1=0$  and  $\varphi_{12}=\varphi_{13}=0.15\pi$ ; (b)  $\alpha_1=0.08\pi$  and  $\varphi_{12}=\varphi_{13}=0.1\pi$ ; and (c)  $\alpha_1=0.08\pi$  and  $\varphi_{12}=\varphi_{13}=0.2\pi$ . The ZVS areas are validated by testing shown in: (d) as a verification of (a); (e) as a verification of (b); (f) as a verification of (c). Note: The operation points of the test in (d) (e) (f) are marked as a star in (a) (b) (c), respectively.

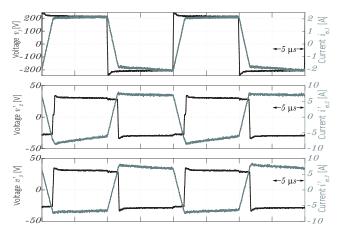

Fig. 10: Operation of TAB converter at unity voltages and all halfbridges achieving ZVS. The phase-shifts  $\varphi_{12}$  and  $\varphi_{13}$  are  $0.15\pi$ .

for each port separately for better clarity as four out of five degrees of freedom are in use. ZVS is achieved on port one only for relatively large phase-shifts  $\varphi_{12}$  and  $\varphi_{13}$ . Increasing phase-shifts  $\alpha_2$  and  $\alpha_3$  leads to an increase of ZVS area of the port one. However, the cost of achieving ZVS transitions on port one is the loss of soft-switching on the leading phase-leg on ports two and three. The origin of this can be seen in Fig. 3. As is clear, the current needs time to reverse polarity before the lead half-bridge turns on. This time is reduced when phase-shifts  $\alpha_2$  and  $\alpha_3$  are larger than zero. On the contrary, for the lagging half-bridge, this time is increased, thus achieving ZVS for the lagging leg is easier. Moreover, it is clear that achieving ZVS on all ports and all phase-leg simultaneously becomes very difficult when the ports are not loaded equally or have highly unbalanced voltages.

# IV. EXPERIMENT

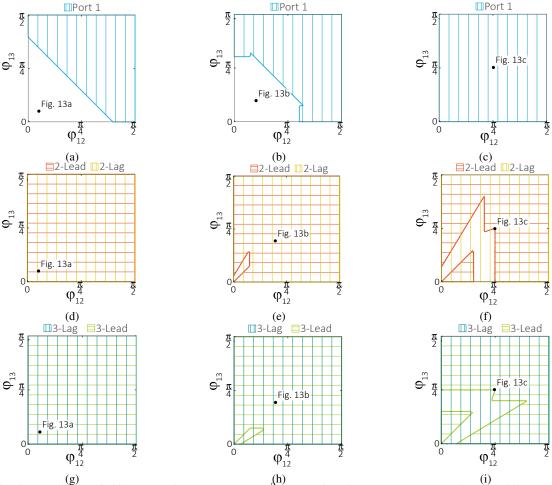

A prototype converter has been built to verify the analysis presented in the previous section. The prototype parameters are summarised in Table V. Several operating points were chosen to demonstrate ZVS or hard commutations.

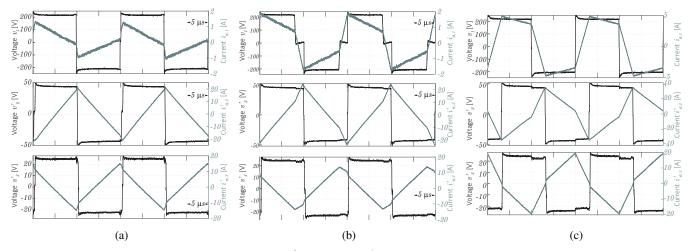

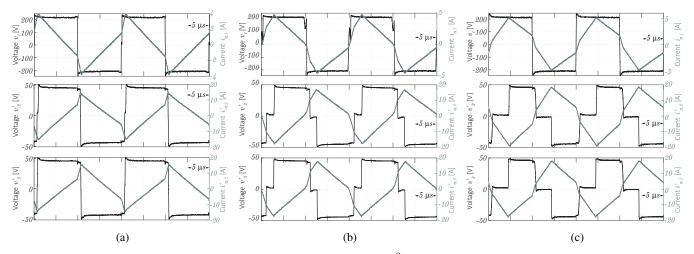

Fig. 11: Measured commutations of ports when  $m_{12}=\frac{2}{3}$  and  $m_{13}=\frac{4}{3}$ . In (a)  $\varphi_{12}=\varphi_{13}=0.05\pi$ . In (b)  $\varphi_{12}=\varphi_{13}=0.15\pi$  and  $\alpha_1=0.15\pi$ . In (c)  $\varphi_{12}=\varphi_{13}=0.3\pi$

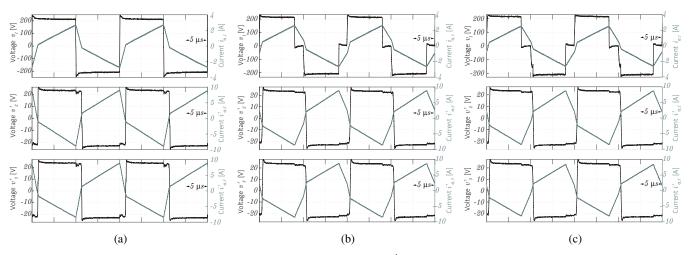

Fig. 12: Measured commutations of ports when voltage ratios  $m_{12}=m_{13}=\frac{4}{3}$ . In (a)  $\varphi_{12}=\varphi_{13}=0.1\pi$ . In (b)  $\varphi_{12}=\varphi_{13}=0.15\pi$  and  $\alpha_1=0.2\pi$ . In (c)  $\varphi_{12}=\varphi_{13}=0.15\pi$  and  $\alpha_1=0.25\pi$ .

Fig. 13: Measured commutations of ports when voltage ratios  $m_{12}=m_{13}=\frac{2}{3}$ . In (a)  $\varphi_{12}=\varphi_{13}=0.1\pi$ . In (b)  $\varphi_{12}=\varphi_{13}=0.2\pi$  and  $\alpha_1=0.15\pi$ . In (c)  $\varphi_{12}=\varphi_{13}=0.25\pi$  and  $\alpha_1=0.4\pi$

Since the three ports are symmetrical, showing the ZVS region for one port should cover all the scenarios. Therefore, the analyzed ZVS regions for Port one, shown in Fig. 9 (a)-(c) are verified, and the test results are shown in Fig. 9 (d)-(f). The operating points of the test in Fig.9 (d)-(f) are marked in Fig. 9(a)-(c), respectively. The test results show MOSFET drain-source voltage, gate-source voltage, port ac voltage, and current, which can be used to identify whether the two legs of Port one are in ZVS or not. For instance, the test in Fig. 9(e) shows that the leading leg (S2) is in ZVS, while the lagging leg (S4) is out of ZVS, which matches the analysis in Fig. 14(b) very well. Similarly, it can be seen the test results in Fig. 9(d) and (f) also match the analyzed ZVS region in Fig. 9(a) and (c) well.

More tests are done at other operation points, and the operation points are also marked in Fig. 6, Fig. 7 and Fig. 8. First the ZVS operation of the converter when voltage ratios are  $\frac{2}{3}$  and  $\frac{4}{3}$  for  $m_{12}$  and  $m_{13}$  respectively are shown in Fig. 11. The operating point shown in Fig. 11a is also marked in Fig. 6a. It is clear that the port with the smallest voltage does not have a soft-switching transition as the current during the transition has the opposite polarity. Similarly, ZVS is not achieved at Port one, as the current is just crossing zero during the commutation. Next operating point is shown in Fig. 11b marked in Fig. 8e. The port with the highest voltage is softswitched. The port with the smallest voltage is hard-switched, as shown by the current polarity. At Port one, the leading halfbridge achieves ZVS. However, the lagging half-bridge is hard switched as the current changes polarity during phase-shift  $\alpha_1$ . The last operating point shown for various voltage ratios is in Fig. 11c and shown in Fig. 6g. As expected, when the phase-shifts are large, even for significantly different voltages, a complete ZVS operation can be achieved on ports two and one. However, the current at Port three is still too small to achieve soft-switching.

Figure 12 confirms the effect of phase-shift  $\alpha_1$  when voltage ratios  $m_{12} = m_{13}$  are  $\frac{4}{3}$ . Figure 12a shows operating point marked in Fig. 7a and Fig. 7e. In the experimental results, the currents are already reversed on all three ports. Figures 7b and 7f mark the operating point measured in Fig. 12b. Port one achieves ZVS, even at the lagging port. Port two and three show that the current had enough time to cross zero before the commutation, and the current is higher at the end of commutation than it was in the previous case, and the ZVS transition is achieved. The last operating point marked in Fig. 7c and Fig. 7g is shown in Fig. 12c. At these operating points, the current at ports two and three had time to change polarity before commutation. However, the current at Port one, when the lagging phase-leg commutates, changes polarity. This leads to a hard transition, thus increasing losses and electromagnetic interference.

Last operating point verified is shown in Fig. 13 when voltage ratios are  $m_{12}=m_{13}=\frac{2}{3}$ , in this set of experimental results the effect of phase-shifts  $\alpha_2$  and  $\alpha_3$  are verified. Starting with operating point marked in Fig. 8a, 8d, 8g is shown in Fig. 13a where port one does not achieve ZVS as clearly the current has opposite polarity as needed. However, ZVS is smoothly achieved on Port two and three. The effect

of introducing phase-shifts  $\alpha_2$  and  $\alpha_3$  is shown in Fig. 13b, this operating point is marked in Fig. 8b, 8e, 8h. It can be observed that the current at Port one is crossing zero during commutation; thus, double transitions are occurring. However, at these operating points, ZVS is kept on all switches on the secondary ports. It is clear why achieving ZVS for the lagging half-bridges on ports two and three are easier than for the leading half-bridges. The current has more time to rise. This effect is even stronger for the operating point shown in Fig. 13c which is marked in Fig. 8c, 8f, 8i. It is possible to achieve ZVS at port one at this operating point as the commutation occurs before the current reverses polarity and no hard commutations occur. However, at ports two and three, it is clear that the current during commutation of the leading half-bridges is still minimal compared to other transitions. The small current amplitude leads to breaking the energy condition and hard transition for the leading half-bridges. On the other hand, the lagging phase-legs undergo soft transitions as the current had enough time to rise.

## V. CONCLUSION

The paper derives the zero voltage switching (ZVS) criteria of the triple active bridge (TAB) converter using Fourier series expansion. Closed-form solutions are summarised and used to investigate the influence of different practical design aspects on the soft-switching regions, including the dc side voltage ratio, the phase shift between ports, and the internal phase shift of each port.

A significant advantage of the derived ZVS criteria is that the effect of parasitic capacitors is considered, ensuring complete commutation of each phase-leg. In general, the port with higher voltage can achieve ZVS easier. Phase shift inside the full bridge can be applied to the port with higher voltage so that the ZVS region of the ports with lower voltage will be enlarged. However, the cost is a reduction of the ZVS region of the port with non-zero internal phase shift, and to be more specific, the ZVS region of its lagging leg if the port is sourcing power, or leading leg if the port is absorbing power. Experiments on a laboratory prototype then verify the closed-form solution of the ZVS and the theoretical analysis. The derived ZVS criteria present a powerful tool to study the operation of TAB converter and further optimisation of its operation. Moreover, the approach outlined in the paper can be generalised to any phase-shift operated n-port topology.

#### **APPENDIX**

#### PROTOTYPE PARAMETERS

TABLE V: Prototype Parameters

| Parameter             | Acronym              | Value             |

|-----------------------|----------------------|-------------------|

| HV MOSFET             | $S_{1-4}$            | C3M0030090K       |

| LV MOSFET             | $S_{5-12}$           | IPB017N10N5       |

| HV MOSFET Capacitance | $C_{oss,1-4}$        | 131 [pF]          |

| LV MOSFET Capacitance | $C_{oss,5-12}$       | 1810 [pF]         |

| Transformer ratio     | N                    | 7 [-]             |

| Switching Frequency   | $f_{sw}$             | 50 [kHz]          |

| Primary Inductance    | $L_{\sigma,1}$       | 106 [μH]          |

| Secondary Inductance  | $L_{\sigma,x}$       | $3 [\mu H]$       |

| Output Capacitance    | $C_{\text{out},x,x}$ | 1.22 [mF]         |

| Primary Resistance    | $R_{\sigma,1}$       | 206 [m $\Omega$ ] |

| Secondary Resistance  | $R_{\sigma,x}$       | 22 [m $\Omega$ ]  |

#### REFERENCES

- A. K. Bhattacharjee, N. Kutkut, and I. Batarseh, "Review of multiport converters for solar and energy storage integration," *IEEE Transactions* on *Power Electronics*, vol. 34, no. 2, pp. 1431–1445, 2018.

- [2] S. Y. Kim, H. Song, and K. Nam, "Idling port isolation control of three-port bidirectional converter for evs," *IEEE Transactions on Power Electronics*, vol. 27, no. 5, pp. 2495–2506, May 2012.

- [3] P. Wheeler and S. Bozhko, "The more electric aircraft: Technology and challenges." *IEEE Electrification Magazine*, vol. 2, pp. 6–12, 2014.

- [4] G. Sulligoi, A. Vicenzutti, and R. Menis, "All-electric ship design: From electrical propulsion to integrated electrical and electronic power systems," *IEEE Transactions on Transportation Electrification*, 2016.

- [5] M. Neubert, A. Gorodnichev, J. Gottschlich, and R. W. D. Doncker, "Performance Analysis of a Triple-Active Bridge Converter for Interconnection of Future DC-Grids," 2016 IEEE Energy Conversion Congress and Exposition, pp. 1–8, 2016.

- [6] P. Purgat, L. Mackay, M. Schulz, Y. Han, Z. Qin, M. März, and P. Bauer, "Design of a power flow control converter for bipolar meshed lvdc distribution grids," in 2018 IEEE 18th International Power Electronics and Motion Control Conference, Aug 2018, pp. 1073–1078.

- [7] C. Zhao and J. W. Kolar, "A novel three-phase three-port ups employing a single high-frequency isolation transformer," in *Power Electronics Specialists Conference*, 2004. PESC 04. 2004 IEEE 35th Annual, vol. 6. IEEE, 2004, pp. 4135–4141.

- [8] S. Falcones, R. Ayyanar, and X. Mao, "A dc-dc multiport-converter-based solid-state transformer integrating distributed generation and storage," *IEEE Transactions on Power electronics*, vol. 28, no. 5, pp. 2192–2203, 2012.

- [9] Y. Chen, P. Wang, H. Li, and M. Chen, "Power flow control in multiactive-bridge converters: Theories and applications," in 2019 IEEE Applied Power Electronics Conference and Exposition. IEEE, 2019.

- [10] R. W. De Doncker, D. M. Divan, and M. H. Kheraluwala, "A three-phase soft-switched high-power-density dc/dc converter for high-power applications," *IEEE transactions on industry applications*, vol. 27, no. 1, pp. 63–73, 1991.

- [11] C. Zhao, S. D. Round, and J. W. Kolar, "An isolated three-port bidirectional dc-dc converter with decoupled power flow management," *IEEE Transactions on Power Electronics*, vol. 23, no. 5, pp. 2443–2453, Sept 2008.

- [12] H. Tao, J. L. Duarte, and M. A. M. Hendrix, "Three-port triple-half-bridge bidirectional converter with zero-voltage switching," *IEEE Transactions on Power Electronics*, vol. 23, no. 2, pp. 782–792, March 2008

- [13] S. Bal, D. B. Yelaverthi, A. K. Rathore, and D. Srinivasan, "Improved modulation strategy using dual phase shift modulation for active commutated current-fed dual active bridge," *IEEE Transactions on Power Electronics*, vol. 33, no. 9, pp. 7359–7375, Sep. 2018.

- [14] Z. Qin, Y. Shen, P. C. Loh, H. Wang, and F. Blaabjerg, "A dual active bridge converter with an extended high-efficiency range by dc blocking capacitor voltage control," *IEEE Transactions on Power Electronics*, vol. 33, no. 7, pp. 5949–5966, July 2018.

- [15] J. Huang, Y. Wang, Z. Li, and W. Lei, "Unified triple-phase-shift control to minimize current stress and achieve full soft-switching of isolated bidirectional dc-dc converter," *IEEE Transactions on Industrial Electronics*, vol. 63, no. 7, pp. 4169–4179, July 2016.

- [16] Y. Shen, X. Sun, W. Li, X. Wu, and B. Wang, "A modified dual active bridge converter with hybrid phase-shift control for wide input voltage range," *IEEE Transactions on Power Electronics*, vol. 31, no. 10, pp. 6884–6900, Oct 2016.

- [17] N. Hou, W. Song, and M. Wu, "Minimum-current-stress scheme of dual active bridge dc-dc converter with unified phase-shift control," *IEEE Transactions on Power Electronics*, vol. 31, no. 12, pp. 8552–8561, Dec 2016.

- [18] A. Tong, L. Hang, G. Li, X. Jiang, and S. Gao, "Modeling and analysis of a dual-active-bridge-isolated bidirectional dc/dc converter to minimize rms current with whole operating range," *IEEE Transactions on Power Electronics*, vol. 33, no. 6, pp. 5302–5316, June 2018.

- [19] H. Zhou and A. M. Khambadkone, "Hybrid modulation for dual-active-bridge bidirectional converter with extended power range for ultracapacitor application," *IEEE Transactions on Industry Applications*, vol. 45, no. 4, pp. 1434–1442, July 2009.

- [20] A. K. Jain and R. Ayyanar, "Pwm control of dual active bridge: Comprehensive analysis and experimental verification," *IEEE Transactions on Power Electronics*, vol. 26, no. 4, pp. 1215–1227, April 2011.

- [21] J. Everts, J. Van den Keybus, F. Krismer, J. Driesen, and J. W. Kolar, "Switching control strategy for full zvs soft-switching operation of a dual active bridge ac/dc converter," in 2012 Twenty-Seventh Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Feb 2012, pp. 1048–1055.

- [22] J. Riedel, D. G. Holmes, B. P. McGrath, and C. Teixeira, "Zvs soft switching boundaries for dual active bridge dc-dc converters using frequency domain analysis," *IEEE Transactions on Power Electronics*, vol. 32, no. 4, pp. 3166–3179, April 2017.

- [23] J. Everts, "Closed-form solution for efficient zvs modulation of dab converters," *IEEE Transactions on Power Electronics*, vol. 32, no. 10, pp. 7561–7576, Oct 2017.

- [24] Zhiyu Shen, R. Burgos, D. Boroyevich, and F. Wang, "Soft-switching capability analysis of a dual active bridge dc-dc converter," in 2009 IEEE Electric Ship Technologies Symposium, April 2009, pp. 334–339.

- [25] S. S. Shah, V. M. Iyer, and S. Bhattacharya, "Exact solution of zvs boundaries and ac-port currents in dual active bridge type dc-dc converters," *IEEE Transactions on Power Electronics*, vol. 34, no. 6, pp. 5043–5047, June 2019.

- [26] F. Krismer and J. W. Kolar, "Accurate small-signal model for the digital control of an automotive bidirectional dual active bridge," *IEEE* transactions on power electronics, vol. 24, no. 12, pp. 2756–2768, 2009.

- [27] F. Krismer and J. W. Kolar, "Closed form solution for minimum conduction loss modulation of dab converters," *IEEE Transactions on Power Electronics*, vol. 27, no. 1, pp. 174–188, Jan 2012.

- [28] S. Shao, M. Jiang, W. Ye, Y. Li, J. Zhang, and K. Sheng, "Optimal phase-shift control to minimize reactive power for a dual active bridge dc-dc converter," *IEEE Transactions on Power Electronics*, vol. 34, no. 10, pp. 10 193–10 205, Oct 2019.

- [29] L. Jiang and D. Costinett, "A Triple Active Bridge DC-DC Converter Capable of Achieving Full-Range ZVS," 2016 IEEE Applied Power Electronics Conference and Exposition (APEC), vol. 3, no. c, pp. 872– 879, 2016.