# ZrO<sub>2</sub> as a high-**k** dielectric for strained SiGe MOS devices

# R MAHAPATRA, G S KAR, C B SAMANTARAY, A DHAR,

D BHATTACHARYA<sup>†</sup> and S K RAY\*

Department of Physics and Meteorology, <sup>†</sup>Material Science Centre, Indian Institute of Technology, Kharagpur 721 302, India

Abstract. The potential of ZrO<sub>2</sub> thin film as a high-**k** gate dielectric for scaled MOSFET devices has been studied. ZrO<sub>2</sub> has been deposited directly on a Si<sub>0.8</sub>Ge<sub>0.2</sub> substrate by reactive RF magnetron sputtering. An equivalent oxide thickness of < 20 Å with a leakage current of the order of  $10^{-4}$  A/cm<sup>2</sup> at 1 V has been obtained. Well-behaved capacitance-voltage characteristics with an interface state density of  $2 \times 10^{11}$  cm<sup>-2</sup>eV<sup>-1</sup> have been achieved. The deposited dielectric exhibits low charge trapping under constant current stressing.

Keywords. ZrO<sub>2</sub>; high-k dielectric; SiGe MOS devices.

### 1. Introduction

The enhancement of hole mobility in compressively strained SiGe layers deposited on Si is well known (People 1986; Crabbe et al 1992). However, the use of SiGe in mainstream metal-oxide-semiconductor field effect transistor (MOSFET) structures, has been plagued with the problems of poor gate oxides. In thermal oxidation of SiGe, the preferential oxidation of Si leads to the formation of Ge-rich layers at the oxide-substrate interface and causes serious degradation of oxide properties (LeGoues et al 1989). In addition, the strain relaxation of SiGe imposes serious thermal budget limitations (Hull et al 1988). These limitations have led to an interest for a new gate material deposited at low temperatures for SiGe devices. In recent years, high-k materials have drawn considerable attention as possible replacements for conventional Si oxide in ULSI. High-k materials such as Ta<sub>2</sub>O<sub>5</sub> (Autran et al 1997; Luan et al 1998; Park et al 1998; van Dover et al 1998), TiO<sub>2</sub> (Guo et al 1998; He et al 1998) and strontium titanate (Mckee et al 1998) are not suitable for SiGe applications because they are not thermally stable on Si, and require a passivation barrier (oxynitride or nitride) to prevent interfacial layer growth. The passivation layers increase the process complexity and limit the scalability of the gate stack. ZrO<sub>2</sub> is one of few high-**k** materials that is predicted to be thermally stable on Si, based on a thermodynamic study (Hubbard and Scholm 1996). It has a high dielectric constant  $(20 \sim 25)$  and a large band gap (7.8 eV). The deposition and electrical properties of  $ZrO_2$  on strained  $Si_{1-x}Ge_x$ (x = 20%) heterostructure have been investigated in this study and the results are presented.

#### 2. Experimental

Lightly phosphorus doped Si wafers with a resistivity of  $8-14 \Omega$ -cm and  $\langle 001 \rangle$  orientation were used as the starting substrate. *In situ* doped epitaxial layers of Si<sub>0.8</sub>Ge<sub>0.2</sub> were deposited on Si buffer layer by ultra-high-vacuum chemical vapour deposition (UHVCVD) at 550°C using Si<sub>2</sub>H<sub>6</sub>, GeH<sub>4</sub> and PH<sub>3</sub>. Prior to ZrO<sub>2</sub> deposition, the samples were subjected to a standard cleaning schedule followed by a dip for 1 min in dilute HF to remove the native oxide and to terminate the surface with hydrogen prior to loading in the process chamber. ZrO<sub>2</sub> was deposited by RF magnetron sputtering at a rf power 50 W with a base pressure  $1 \times 10^{-6}$  Torr. Reactive sputtering was performed in an Ar + O<sub>2</sub> ambient with the ratio 4 : 1 keeping the operating pressure of  $1 \times 10^{-1}$  Torr and the substrate temperature at 350°C.

Electrical characterizations of  $\text{ZrO}_2$  films were carried out using fabricated Al–gate metal–insulator–semiconductor (MIS) capacitor structures. High frequency (100 kHz) capacitance–voltage (*C*–*V*) characteristics were used to extract the flat-band voltage (*V*<sub>FB</sub>) and interface state density (*D*<sub>it</sub>) at midgap energy. The d.c. current–voltage (*I*–*V*) characteristics were studied to evaluate the breakdown property of the MIS capacitors. Charge trapping behaviour of the dielectric was studied using constant current stressing of the capacitors.

#### 3. Results and discussion

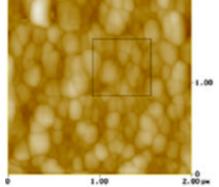

Semiconductor surface roughness is one of the important parameters, which can adversely affect the performance and reliability of the devices. Atomic force microscopy (AFM) was used to study the surface morphology of the film with a Nanoscope III system, from Digital Instruments. Figure 1 shows the atomic force micrograph of

<sup>\*</sup>Author for correspondence

ZrO<sub>2</sub> film deposited on Si<sub>0.8</sub>Ge<sub>0.2</sub>. Root mean square roughness of deposited films is about 8.87 nm, which is higher than conventional thermal oxide grown on Si.

Figure 2 shows the high frequency (100 kHz) capacitance-voltage (C-V) characteristics of Si/Si<sub>0.8</sub>Ge<sub>0.2</sub>/ZrO<sub>2</sub>/ Al MIS structures. A well-behaved C-V curve is obtained with a relatively low value of flat band voltage. The capacitance in accumulation region is measured to be 8.24 nF, which corresponds to the equivalent silicon oxide thickness (EOT) = 1.83 nm. The dielectric constant of ZrO<sub>2</sub> films is found to be 20. The interface state density is calculated using Terman (1962) method. By comparison of the experimental 100 kHz C-V and the ideal high frequency C-V curve with the same equivalent oxide thickness, the interface state density is found to be  $2.0 \times 10^{11} \text{ cm}^{-2} \text{ eV}^{-1}$ . The magnitude is comparable to the best results published so far on the interfacial properties of gate oxides on SiGe layers (Tchikatilov et al 1996; Sharma et al 1999).

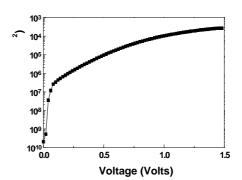

The key advantage offered by high-k materials is to increase the physical oxide thickness and reduce leakage currents without significantly increasing the actual EOT of gate dielectrics. The current density vs voltage (J-V)characteristics of ZrO<sub>2</sub> films is shown in figure 3. At a bias of 1 V, the leakage current density is around  $10^{-4}$  A cm<sup>-2</sup>. This is much lower than the leakage of SiO<sub>2</sub> gate oxide with the same equivalent oxide thickness (Buchanan and Lo 1997). The lower leakage current in ZrO<sub>2</sub> is attributed to the increased physical thickness of the higher dielectric constant material, and the high energy band gap of  $ZrO_2$ . Both the energy band gap of  $ZrO_2$  $(7 \cdot 8 \text{ eV})$  and the increased physical thickness (due to high dielectric constant of ZrO<sub>2</sub>) contribute to the reduction of tunnelling of carriers through the dielectric. It has been reported that the conduction band offset for ZrO<sub>2</sub> is 1.4 eV, while the valence band offset is 3.3 eV (Robertson et al 2000). These band offsets also indicate that the barrier heights for both electrons and holes are quite high leading to lower leakage current density in the film.

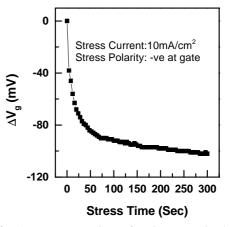

The charge trapping behaviour of ZrO<sub>2</sub> films under constant current stress of 10 mA/cm<sup>2</sup> for 300 s, measured by continuously monitoring the change in gate voltage  $(\Delta V_{\rm G})$  required to maintain a constant current under gate injection, is presented in figure 4. The positive and negative gate voltage shifts indicate electron and hole trapping, respectively (Hao et al 1994). The gate voltage change,  $\Delta V_{\rm G}$ , is found to be  $-100 \,\mathrm{mV}$  for constant

**Figure 3.** J-V characteristics of  $ZrO_2$  films.

Figure 2. High frequency C-V characteristics of Al/ZrO<sub>2</sub>/ Si<sub>0.8</sub>Ge<sub>0.2</sub>/Si MIS structure.

-0.5 0.0

0.5

Gate Voltage (Volts)

Figure 4.  $\Delta V_{\rm G}$  vs stress time of ZrO<sub>2</sub> on strained Si<sub>0.8</sub>Ge<sub>0.2</sub> under a constant current stress.

Figure 1. AFM micrograph of deposited ZrO<sub>2</sub> film on strained SiGe.

10

8

6

4

2

0

-1.0

Capacitance (nF)

EOT=18Å

$\varepsilon_r = 19 - 20$

1.0 1.5 2.0

current stress, indicating the hole trapping in the films. The presence of hole traps rather than electron traps in the oxide indicates the absence of any Ge segregation in the oxide–semiconductor interface during the oxidation process. The small  $\Delta V_{\rm G}$  also exhibits considerably lower charge trapping rates in deposited ZrO<sub>2</sub>, making it highly attractive for SiGe MOS device applications.

## 4. Conclusions

We have demonstrated that  $ZrO_2$  exhibits excellent electrical properties to become potential alternative to conventional SiO<sub>2</sub>, especially for ULSI SiGe MOSFETs with gate oxide < 20 Å thick.  $ZrO_2$  film with equivalent oxide thickness of < 20 Å has been achieved by RF sputtering. The interface state density of the dielectric on Si<sub>0.8</sub>Ge<sub>0.2</sub> has been calculated to be  $2 \times 10^{11}$  cm<sup>-2</sup> eV<sup>-1</sup>. Experimental results show remarkably low leakage current, without any significant charge trapping under constant current stressing.

### References

- Autran J L, Devine R, Chaneliere C and Balland B 1997 *IEEE Electron Device Lett.* **18** 447

- Buchanan D A and Lo S H 1997 Microelectron. Eng. 36 13

- Crabbe E F, Comfort J H, Lee W, Cressler J D, Meyerson

B S, Megdanis A C, Sun J Y C and Stork J M C 1992 *IEEE Electron. Device Lett.* **13** 259

- Guo X, Ma T P, Tamagawa T and Halpern B L 1998 Tech. Dig. Int. Electron. Devices Meet. 377

- Hao M Y, Maiti B and Lee J C 1994 Appl. Phys. Lett. 64 2102

- He B, Ma T, Campbell S A and Gladfelter W L 1998 Tech. Dig. Int. Electron Devices Meet. 1038

- Hubbard K J and Scholm D G 1996 J. Mater. Res. 11 2757

- Hull R, Bean J C, Werder D J and Leibenguth R E 1988 Appl. *Phys. Lett.* **52** 1605

- Le Goues F K, Rosenberg R and Meyerson B S 1989 Appl. Phys. Lett. 54 644

- Luan H F, Wu B Z, Kang L G, Kim B Y, Vrtis R, Roberts D and Kwong D L 1998 *Tech. Dig. Int. Electron. Devices Meet.* 609

- Mckee R A, Walker F J and Chisholm M F 1998 *Phys. Rev.* Lett. **81** 3014

- Park D, Lu Q, Ling T J, Hu C, Kalnitsky A, Tay S and Cheng C C 1998 Tech. Dig. Int. Electron. Devices Meet. 381

- People R 1986 IEEE J. Quantum Electron. 22 1696

- Robertson J, Riassi E, Maria J P and Kingon A L 2000 J. Vac. Sci. Technol. **B18** 1785

- Sharma R, Fretwell J L, Ngai T and Banerjee S 1999 J. Vac. Sci. Technol. **B17** 460

- Tchikatilov D, Yang Y F and Yang E S 1996 *Appl. Phys. Lett.* **69** 2578

- Terman M L 1962 Solid State Electron. 5 285

- van Dover R B, Fleming R M, Schneemeyer L F, Alers G B and Werder D J 1998 *Tech. Dig. Int. Electron Devices Meet.* 823