All figures (26)

Figure 4 Flex-SISO module.

Figure 3 A block-structured parity check matrix, where each block row (or layer) defines a super-code. Each sub-matrix of the parity check matrix is either a zero matrix or a z × z cyclically shifted identity matrix.

Figure 2 Dividing a factor graph into sub-graphs.

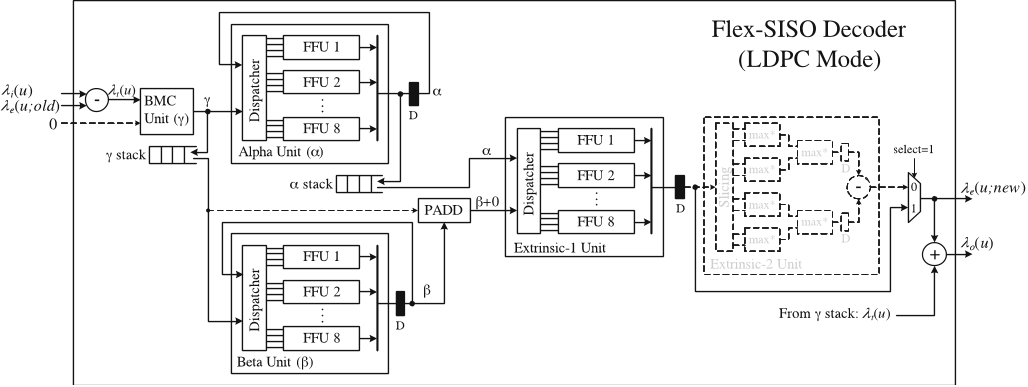

Figure 19 Flexible SISO decoder architecture.

Figure 20 Data flow graph for Turbo decoding.

Figure 11 Trellis structure for a single parity check code.

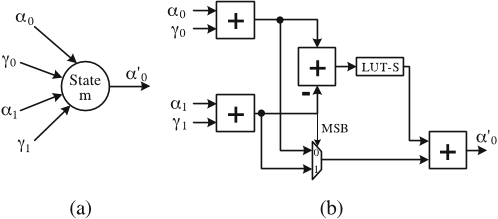

Figure 10 Turbo ACSA structure. a Flow of state metric calculation. b Circuit diagram for the Turbo ACSA unit.

Figure 9 Turbo decoder architecture based on the Flex-SISO module.

Figure 16 Simulation results for a rate 1/2, length 2304 WiMAX LDPC code.

Figure 17 Comparison of the convergence speed.

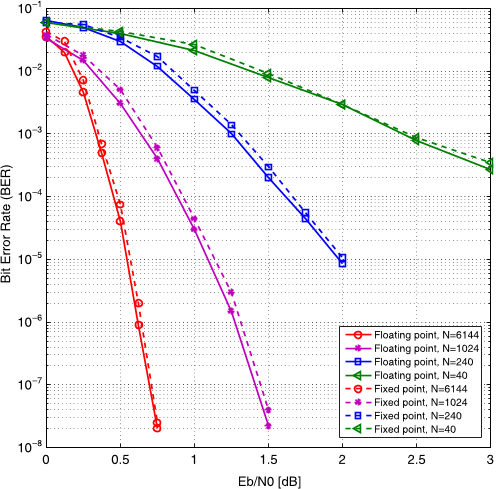

Figure 18 Simulation results for 3GPP-LTE Turbo codes with a variety of block sizes.

Figure 1 Trellis representation for LDPC codes where a twostate trellis diagram is associated with each check node.

Table 7 Turbo decoder architecture comparison with existing solutions.

Table 1 LUT approximation for g(x) = log(1 + e−|x|).

Table 2 LUT implementation for Q.2 quantization.

Figure 12 A forward–backward decoding flow to compute the extrinsic LLRs for single parity check code.

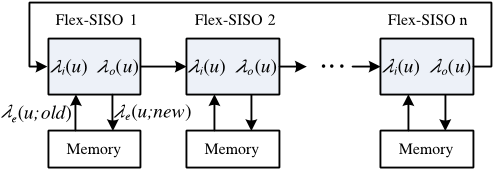

Figure 5 LDPC decoding using Flex-SISO modules where a LDPC code is decomposed into n super-codes, and n Flex-SISO modules are connected in series to decode.

Figure 21 Flexible SISO decoder architecture in LDPC mode.

Figure 22 Parallel LDPC/Turbo decoder architecture based on multiple Flex-SISO decoder cores.

Table 5 Flex-SISO decoder area distribution.

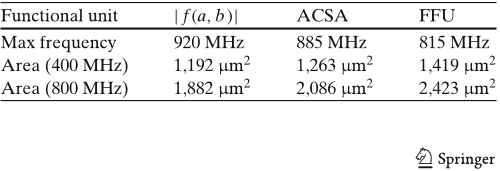

Table 4 Synthesis results for different functional units.

Figure 14 Circuit diagram for the LDPC | f (a,b)| functional unit.

Table 3 Functional description of the FFU.

Figure 15 Circuit diagram for the flexible functional unit (FFU) for LDPC/Turbo decoding.

Figure 6 LDPC decoder architecture based on the Flex-SISO module.

Figure 7 Traditional Turbo decoding procedure using two SISO decoders, where the extrinsic LLR values are exchanged between two SISO decoders.