184 IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 58, NO. 1, JANUARY 2011

A New High-Efficiency Single-Phase

Transformerless PV Inverter Topology

Tamás Kerekes, Member, IEEE, Remus Teodorescu, Senior Member, IEEE, Pedro Rodríguez, Member, IEEE,

Gerardo Vázquez, Student Member, IEEE, and Emiliano Aldabas, Member, IEEE

Abstract—There is a strong trend in the photovoltaic inverter

technology to use transformerless topologies in order to acquire

higher efficiencies combining with very low ground leakage cur-

rent. In this paper, a new topology, based on the H-bridge with a

new ac bypass circuit consisting of a diode rectifier and a switch

with clamping to the dc midpoint, is proposed. The topology is

simulated and experimentally validated, and a comparison with

other existing topologies is performed. High conversion efficiency

and low leakage current are demonstrated.

Index Terms—Leakage current, parasitic capacitance, switch-

ing converter.

I. INTRODUCTION

P

HOTOVOLTAIC (PV) inverters become more and more

widespread within both private and commercial circles.

These grid-connected inverters convert the available direct cur-

rent supplied by the PV panels and feed it into the utility grid.

According to the latest report on installed PV power, during

2007, there has been a total of 2.25 GW of installed PV systems,

out of which the majority (90%) has been installed in Germany,

Spain, U.S., and Japan. At the end of 2007, the total installed

PV capacity has reached 7.9 GW of which around 92% is grid

connected [1].

There are two main topology groups used in the case of

grid-connected PV systems, namely, with and without galvanic

isolation [2]. Galvanic isolation can be on the dc side in the

form of a high-frequency dc–dc transformer or on the grid

side in the form of a big bulky ac transformer. Both of these

solutions offer the safety and advantage of galvanic isolation,

but the efficiency of the whole system is decreased due to power

losses in these extra components. In case the transformer is

omitted, the efficiency of the whole PV system can be increased

with an extra 1%–2%. The most important advantages of trans-

formerless PV systems can be observed in Fig. 1, such as higher

efficiency and smaller size and weight compared to the PV

systems that have galvanic isolation (either on the dc or ac side).

Fig. 1 has been made from the database of more than

400 commercially available PV inverters, presented in a com-

mercial magazine about PV systems [3]. Transformerless

Manuscript received December 19, 2008; revised April 6, 2009; accepted

May 14, 2009. Date of publication June 5, 2009; date of current version

December 10, 2010.

T. Kerekes and R. Teodorescu are with the Institute of Energy Technology,

Aalborg University, Aalborg, Denmark.

P. Rodríguez, G. Vázquez, and E. Aldabas are with the Technical University

of Catalonia (UPC), Barcelona, Spain.

Color versions of one or more of the figures in this paper are available online

at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TIE.2009.2024092

Fig. 1. Advantages and drawback of different inverter topologies.

inverters are represented by the dots (transformerless), the

triangles represent the inverters that have a low-frequency

transformer on the grid side (LF-transformer), and last, the

stars represent the topologies, including a high-frequency dc–dc

transformer (HF-transformer), adding a galvanic isolation be-

tween the PV and grid. The conclusion drawn from these graphs

is that transformerless inverters have higher efficiency and

smaller weight and size than their counterparts with galvanic

separation.

Transformerless PV inverters use different solutions to min-

imize the leakage ground current and improve the efficiency of

the whole system, an issue that has previously been treated in

many papers [4]–[11].

In order to minimize the ground leakage current through the

parasitic capacitance of the PV array, several techniques have

been used.

0278-0046/$26.00 © 2011 IEEE

KEREKES et al.: NEW HIGH-EFFICIENCY SINGLE-PHASE TRANSFORMERLESS PV INVERTER TOPOLOGY 185

One of them is to connect the midpoint of the dc-link

capacitors to the neutral of the grid, like the half-bridge, neutral

point clamped (NPC), or three-phase full bridge with a split

capacitor topology, thereby continuously clamping the PV array

to the neutral connector of the utility grid. Half-bridge and NPC

type of converters have very high efficiency, above 97%, as

shown in [6]. Furthermore, the topology proposed in [6] reduces

the dc current injection, which is an important issue in the

case of transformerless topologies and is limited by different

standards. The noninjection of dc current into the grid is topo-

logically guaranteed by adding a second capacitive divider to

which the neutral terminal of the grid is connected. An extra

control loop is introduced that compensates for any dc current

injection, by controlling the voltage of both capacitive dividers

to be equal. A disadvantage of half-bridge and NPC type of

converters is that, for single-phase grid connection, they need a

700-V dc link.

Another solution is to disconnect the PV array from the grid,

in the case of H-bridge (HB) inverters, when the zero vector

is applied to the load (grid). This disconnection can be done

either on the dc side of the inverter (like the topology from [4]

and H5 topology from Solar Technologies AG [13]) or on the

ac side (like the Highly Efficient and Reliable Inverter Concept

(HERIC) topology from Sunways [12]).

In this paper, a new topology called HB zero-voltage state

rectifier (HB-ZVR) is proposed where the midpoint of the dc

link is clamped to the inverter only during the zero-state period

by means of a diode rectifier and one switch.

In Section II, a comparison of known transformerless topolo-

gies and the HB-ZVR is performed using simulation, focus-

ing on the voltage to earth and ground leakage current. In

Section III, experimental results are shown, confirming the

simulations. Section IV presents the efficiency curve of the

compared topologies.

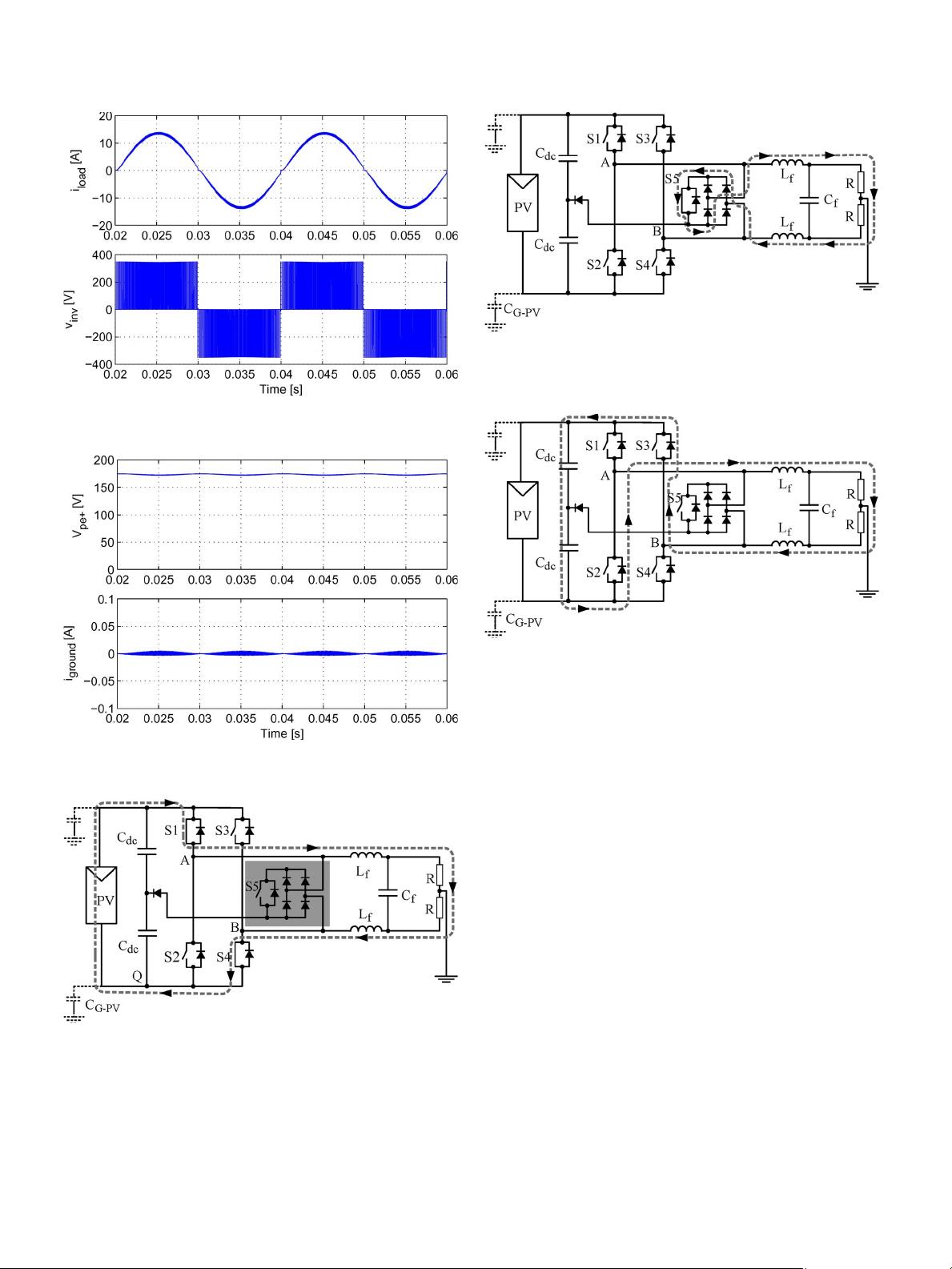

II. T

RANSFORMERLESS TOPOLOGY ANALY S IS

As discussed in previous works [8], [11], the common-mode

voltage generated by a topology and modulation strategy can

greatly influence the ground leakage current that flows through

the parasitic capacitance of the PV array. Generally, the utility

grid does not influence the common-mode behavior of the

system, so it can be concluded that the generated common-

mode voltage of a certain inverter topology and modulation

strategy can be shown using a simple resistor as load. Therefore,

in the case of simulations, only a resistive l oad is used, and the

common-mode voltage is measured between the dc+ terminal

of the dc source and the grounded middle point of the resistor

as shown in Fig. 2.

In the following, simulation results obtained using Matlab

Simulink with the PLECS toolbox are shown. The simulation

step size is 0.1 μs, with an 8-kHz switching frequency.

Simulation parameters:

L

f

=1.8 mH filter inductance;

C

f

=2μF filter capacitance;

R =7.5Ω load resistance;

V

dc

= 350 V input dc voltage;

C

dc

= 250 μF dc-link capacitance;

Fig. 2. Test setup used for common-mode voltage measurement.

Fig. 3. HB-Unip topology: Active vector applied to load, using S1 and S4 for

positive voltage.

C

G−PV

= 100 nF parasitic capacitance of PV array;

F

sw

=8kHz switching frequency f or all cases except

that the switching frequency for unipolar

pulsewidth modulation (PWM) has been

chosen to be F

sw

=4kHz, so the output

voltage of the inverter has the same fre-

quency for all cases.

A. HB With Unipolar Switching

Most single-phase HB inverters use unipolar switching in

order to improve the injected current quality of the inverter,

which is done by modulating the output voltage to have three

levels with twice the switching frequency. Moreover, this type

of modulation reduces the stress on the output filter and de-

creases the losses in the inverter.

The positive active vector is applied to the load by turning on

S1 and S4, as shown in Fig. 3.

The negative active vector is done similarly, but in this case,

S2 and S3 are turned on.

As shown in Fig. 4, the zero-voltage state is achieved by short

circuiting the output of the inverter for the case of the unipolar

switching pattern. The waveforms for this case are detailed in

Fig. 5, and it can be seen that the output voltage has three levels:

+V, 0, and −V due to the unipolar switching pattern.

As shown in Fig. 6, in the case of a transformerless PV

system using this type of topology and modulation, the high-

frequency common-mode voltage, measured across C

G−PV

,

will lead to a very high leakage ground current, making it un-

safe and therefore not usable (recommended) for transformer-

less PV applications.

186 IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 58, NO. 1, JANUARY 2011

Fig. 4. HB-Unip topology: Zero vector applied to load, using S1 and S3 for

positive voltage.

Fig. 5. HB-Unip topology: Load current and inverter output voltage.

Fig. 6. HB-Unip topology: Voltage to ground and ground leakage current.

B. HERIC

This topology, shown in Fig. 7, combines the advantages

of the three-level output voltage of the unipolar modulation

with the reduced common-mode voltage, as in the case of

bipolar modulation. This way, the efficiency of the inverter is

Fig. 7. HERIC topology: Active vector applied to load, using S1 and S4

during positive half-wave.

Fig. 8. HERIC topology: Zero vector applied to load, using S6 during positive

half-wave.

increased, without compromising the common-mode behavior

of the whole system.

The zero-voltage state is realized using a bidirectional switch

shown with a gray background in Fig. 7. This bidirectional

switch is made up of two insulated-gate bipolar transistors

(IGBTs) and two diodes (S5 and S6). During the positive half-

wave of the load (grid) voltage, S6 is switched on and is used

during the freewheeling period of S1 and S4. On the other hand,

during the negative half-wave, S5 is switched on and is used

during the freewheeling period of S2 and S3 [12].

This way, using S5 or S6 as shown in Fig. 8, the zero-voltage

state is realized by short-circuiting the output of the inverter,

during which period the PV is separated from the grid, because

S1–S4 or S2–S3 are turned off.

As shown in Fig. 9, the output voltage of the inverter has

three levels and the load current ripple is very small, although,

in this case, the frequency of the current is equal to the switch-

ing frequency. As shown in Fig. 10, the inverter generates no

common-mode voltage; therefore, the leakage current through

the parasitic capacitance of the PV would be very small.

C. Proposed Topology (HB-ZVR)

Another solution for generating the zero-voltage state can

be done using a bidirectional switch made of one IGBT and

one diode bridge. The topology is detailed in Fig. 11, showing

the bidirectional switch as an auxiliary component with a

gray background. This bidirectional switch is clamped to the

KEREKES et al.: NEW HIGH-EFFICIENCY SINGLE-PHASE TRANSFORMERLESS PV INVERTER TOPOLOGY 187

Fig. 9. HERIC topology: Load current and inverter output voltage.

Fig. 10. HERIC topology: Voltage to ground and ground leakage current.

Fig. 11. HB-ZVR topology: Active vector applied to load, using S1 and S4

during positive half-wave.

midpoint of the dc-link capacitors in order to fix the potential

of the PV array also during the zero-voltage vector when S1–S4

and S2–S3 are open. An extra diode is used to protect from

short-circuiting the lower dc-link capacitor.

During the positive half-wave, S1 and S4 are used to generate

the active state, supplying a positive voltage to the load, as

shown in Fig. 11.

Fig. 12. HB-ZVR topology: Zero vector applied to load, using S5 during

positive half-wave.

Fig. 13. HB-ZVR topology: Deadtime between turnoff of S1 and S4 and turn-

on of S5 during positive half-wave.

The zero-voltage state is achieved by turning on S5 when S1

and S4 are turned off, as shown in Fig. 12. The gate signal for

S5 will be the complementary gate signal of S1 and S4, with

a small deadtime to avoid short-circuiting the input capacitor.

By using S5, it is possible for the grid current to flow in both

directions; this way, the inverter can also feed reactive power to

the grid, if necessary.

During the negative half-wave of the load voltage, S2 and S3

are used to generate the active vector and S5 is controlled using

the complementary signal of S2 and S3 and generates the zero-

voltage state, by short-circuiting the outputs of the inverter and

clamping them to the midpoint of the dc-link.

During the deadtime, between the active state and the zero

state, there is a short period when the freewheeling current finds

its path through the antiparallel diodes to the input capacitor

while all the switches are turned off. This is shown in Fig. 13

and leads to higher losses, compared to the HERIC topology,

where the freewheeling current finds its path through the bidi-

rectional switch, either through S5 or S6, depending on the sign

of the current.

As shown in Fig. 14, the output voltage of the inverter has

three levels, taking into account the freewheeling part during

deadtime. In this case also, the load current ripple is very small

and the frequency i s equal to the switching frequency.

To show that this topology does not generate a vary-

ing common-mode voltage, V

cm

has been calculated for the

188 IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 58, NO. 1, JANUARY 2011

Fig. 14. HB-ZVR load current and inverter output voltage.

switching states regarding the positive, zero, and negative

vectors

V

cm

=

V

AQ

+ V

BQ

2

(1)

Positive : V

AQ

= V

dc

; V

BQ

=0⇒ V

cm

=

V

dc

2

(2)

Zero : V

AQ

=

V

dc

2

; V

BQ

=

V

dc

2

⇒ V

cm

=

V

dc

2

(3)

Negative : V

AQ

=0; V

BQ

= V

dc

⇒ V

cm

=

V

dc

2

. (4)

As detailed by (1)–(4), the common-mode voltage is constant

for all switching states of the converter. Therefore, the leakage

current through the parasitic capacitance of the PV would be

very small, as shown in Fig. 15.

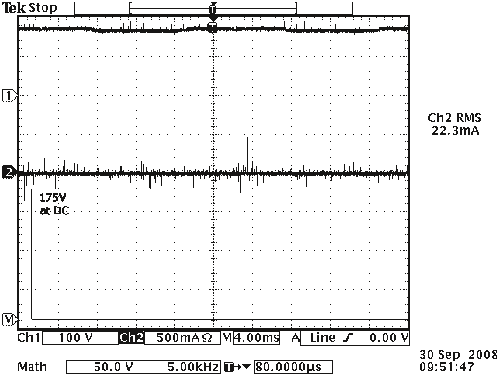

III. E

XPERIMENTAL RESULTS

In the case of the experimental results, the setup has the same

parameters as was the case of the simulations: V

dc

= 350 V,

C

dc

= 250 μF, L

f

=1.8 mH, C

f

=2μF, F

sw

=8kHz, and

deadtime =2.5 μs.

To compare the behavior of the different inverters, all

three t opologies have been tested using the same components.

PM75DSA120 Intelligent Power Modules with maximum rat-

ings of 1200 V and 75 A from Mitsubishi as IGBTs and DSEP

30-06BR with maximum ratings of 600 V and 30 A as diodes

from IXYS have been used in the diode bridge of the proposed

topology.

Fig. 15. HB-ZVR topology: Voltage to ground and ground leakage current.

Fig. 16. Experimental setup: Modular solution.

The modular based setup shown in Fig. 16 makes it possible

to test the different topologies, namely, full bridge with bipolar

or unipolar modulation, the HERIC topology, and the proposed

HB-ZVR, using the same components.

A. HB With Unipolar Switching (Experiment)

The main advantage of the HB inverter with unipolar switch-

ing is that the output voltage has three levels and the frequency

of the output voltage is the double of the switching frequency,

thereby increasing the efficiency of the inverter and decreasing

the size of the output filter. However, the major drawback

of this topology is the high-frequency common-mode volt-

age, which makes it unsuitable to be used for transformerless

PV systems.

As shown in Fig. 17, the unipolar PWM strategy used in the

case of the HB topology generates a high-frequency common-

mode voltage, measured between the dc+ terminal of the

dc-link and ground, shown by channel 1 in Fig. 17.

As also shown in Fig. 17, the fast Fourier transform (FFT)

represented by channel M details the spectrum of the common-

mode voltage. This common-mode voltage has very high am-

plitudes both at dc and the switching frequency. In addition, a

low-frequency component can be seen on the measured voltage,

which is caused by the 100-Hz single-phase power variation.